# THE MAGAZINE FOR COMPUTER APPLICATIONS

# #124 NOVEMBER 2000 WIRELESS COMMUNICATIONS

**Debugging Wireless Devices**

**Design2K Winning Projects**

Build a PIC-Based SBC

**TPU Programming Basics**

#### ChipCenter: The Web's Definitive Electronics Resource

Address http://www.chipcenter.com/circuitcellar

#### LOGIN/REGISTER

**Buy Parts Now!**

myChipCenter

Knowlege Centers

- Guides & Experts

- Product Reviews

- Communities

- Online Tools

- Circuit Cellar

- Resources

- Real Life

SEARCH CHIPCENTER

Let us help keep vour project on track or simplify your design decision. Put your tough technical questions to the ASK US team.

The ASK US research staff of engineers has been assembled to share expertise with others. The forum is a place where engineers can congregate to get some tough questions answered, or just browse through the archived Q&As to broaden their own intelligence base.

8 Additional Questions

# CIRCUIT CELLAR ONLINE

THE MAGAZINE FOR COMPUTER APPLICATIONS Circuit Cellar Online offers articles illustrating creative solutions

and unique applications through complete projects, practical tutorials, and useful design techniques.

This Month (Archive About Us) Contact Looking for More?

#### THE ETHERNET DEVELOPMENT BOARD

#### by Fred Eady

#### Part 1: Putting it all Together

Fred moves the Florida room online as he follows through on the recent promise he made in the print version of *Circuit Cellar* to look at some simple, valuable Ethernet hardware. He makes things easy with a step-by-step process to get your Ethernet engine fully functional. This is part one of the series, so look for his upcoming articles to round out the picture. GOD

October 2000

#### **UML IN A PRODUCT'S LIFE CYCLE**

#### by Venu Kosuri

Intended to be an introduction to UML, this article focuses on illustrating how to use its concepts in the development life cycle of a product. UML is a stateof-the-art modeling methodology useful for real-time systems, so if you're still a beginner, Venu will guide you through to the end.

October 2000

October 2000

October 2000

#### **ABETTER BATTERY CHARGER** by Thomas Richter

It seems logical that there would be a push for smaller, lightweight, highcapacity batteries with today's outcropping of all kinds of portable equipment. Battery technology is making strides towards enhanced algorithms for faster charging and minimal battery damage. In this article, Thomas looks at the next generation of microcontrollers leading the way past the competition.

#### EVERYTHING CHANGES—Using the Const Modifier **Lessons From the Trenches**

#### by George Martin

**ANYGATE IN A STORM**

Silicon Update Online

ultimately how high prices will climb.

by Tom Cantrell

Sometimes we have the knowledge, but don't utilize all the tools we have available to us. George looks at the forgotten modifier beyond char, int, long, and float for writing code in C. Remember the often overlooked const qualifier? Well, it can be used to ensure that the data won't be modified during execution, eliminating unexpected changes.

This month, Tom sets us afloat with Micrel's SY55851U (Anygate). Rather than

letting you sink in a sea of ones and zeros, Anygate can act as a lifejacket of

sorts, making up for its lack of features with bipolar process and differential

Semiconductor's OneGate, Tom wonders about the future of gate delay, and

signaling for fast action. Musing about his recent reports about ON

GO

GOP

GO

Content-Addressable Memory Bob Paddock GPS Technology Overview GPS Manufacturers **Rick Prescott**

October 2000

set of **Circuit Cellar** Online archives.

SAVE

DOWNLOAD

TIME

Mfr Data Sheets

App Notes Ask Us

SuperSearch

Search Type:

Search for:

\*lm317\*

Part Number

GO

First 6 issues July-Dec 1999 are available.

CD Includes: All HTML files Article PDF Code files

Navigate and use just as you would online. (no Internet connection required)

|   | 12            | <b>Wireless Devices</b><br>Handling Power Efficiency and Debugging<br>Brian Branson & David Gonzales |    |  |  |  |  |

|---|---------------|------------------------------------------------------------------------------------------------------|----|--|--|--|--|

|   | 20            | Simplified TPU Programming<br>Jeff Loeliger                                                          |    |  |  |  |  |

|   | 34            | A PIC17C44-Based Computer<br>Duane Perkins                                                           |    |  |  |  |  |

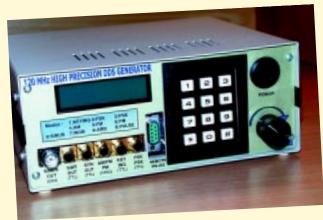

|   | 56            | <b>Design2K Winners</b><br>edited by Rob Walker                                                      |    |  |  |  |  |

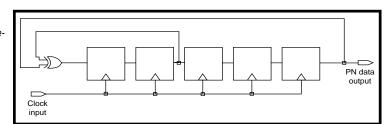

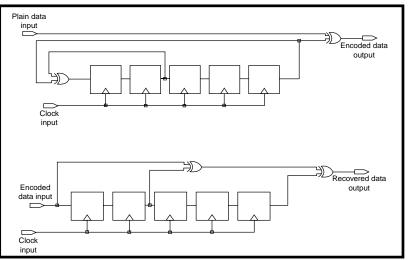

|   | 62            | <b>Applications of PN Sequences</b><br>Tom Napier                                                    |    |  |  |  |  |

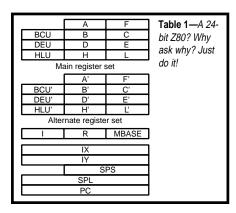

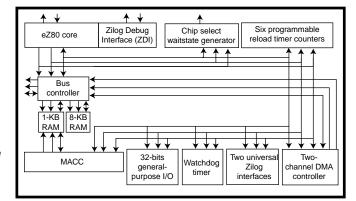

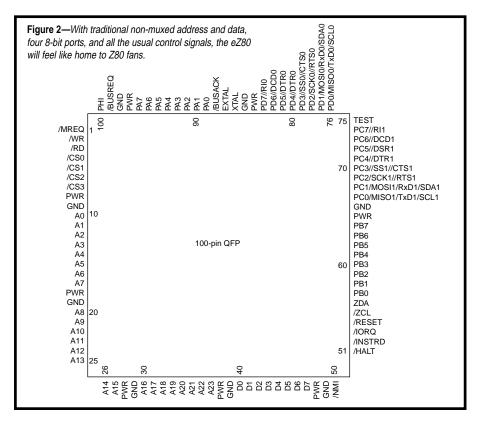

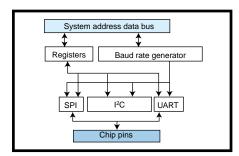

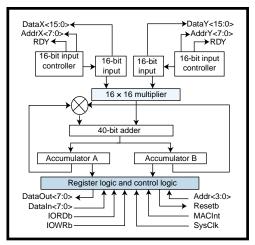

|   | 68            | Embedded LivingThe "S" is for SpeedBreathe New Life into Your Z180 DesignsMike BaptisteTask Manager  | 6  |  |  |  |  |

|   | 74            | Rob Walker         Silicon Update       An International Blend         eZ Does It                    |    |  |  |  |  |

|   | 70            | Tom Cantrell     New Product News       edited by Rick Prescott       From the Bench                 | 8  |  |  |  |  |

|   | 10            | Megawatt Castles Made of Sand<br>Exploring the Solar Cell<br><i>Ieff Bachiochi</i>                   | 11 |  |  |  |  |

|   |               | Test Your EQ                                                                                         | 84 |  |  |  |  |

|   |               | Advertiser's Index<br>December Preview                                                               | 95 |  |  |  |  |

|   |               | DED PC                                                                                               | 96 |  |  |  |  |

| 4 | 40 Nouveau PC |                                                                                                      |    |  |  |  |  |

| 4 | edited        | I by Rick Prescott Real-Time PCs Debugging an FPGA Module Finding the Right Test Case Ingo Cyliax    |    |  |  |  |  |

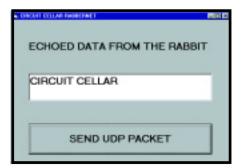

| 4 | 8 арс         | <b>Applied PCs</b><br>Rabbit Season<br>Part 3: Network Analysis<br><i>Fred Eady</i>                  |    |  |  |  |  |

## TASK MANAGER

### An International Blend

he way I see it, this issue will hit the newsstands just in time for me to provide some last minute voting advice for the readers here in the U.S. Unfortunately, I follow politics just

about as closely as I follow the U.S. pole-vault team, that is, every four years I manage to gain interest for a month or so.

This year it just so happened that the Olympic games were winding down as the election fanfare was heating up (which event contains more drama is debatable). But, I won't carry on about the election woes of the U.S., after all, the Circuit Cellar audience extends far beyond the territories of the U.S.

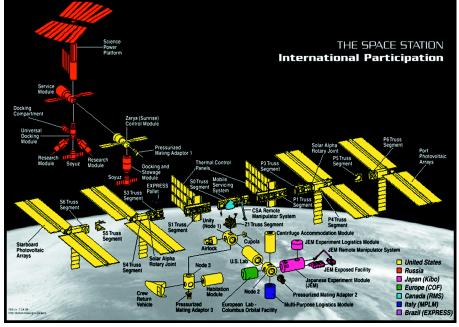

A recent check of our web site statistics shows that developers and designers in almost 70 countries (outside the U.S.) have subscribed to Circuit Cellar via the Internet (almost makes me want to vote for the candidate who helped "invent" the Internet). If there was an awards ceremony, we'd be listening to the Canadian national anthem and saying thanks to our friends to the north.

Australia would easily take the silver medal with more than twice as many online orders as the United Kingdom, which has the third highest order rate. Just out of the medals would be Mexico with a few subscriptions less than the U.K. However, until ordering a magazine subscription over the Internet becomes an Olympic event, Canada, Australia, and the U.K. will have to settle for bragging rights.

The international reach of Circuit Cellar doesn't stop with online subscription ordering. The Design2K contest sponsored by Philips turned out to be one of the most far-reaching contests we've had. As with any Circuit Cellar design contest, there was a variety of entries and you'll find the top projects starting on page 56 or on the Internet at www.circuitcellar.com/design2k/winners. Almost half of the projects we received for the Design2K contest were from outside of the U.S. With such an international field of entries, it's no wonder that eight different countries are represented among the winners.

Congratulations to all of the winners in the Design2K contest and thanks to all of you who submitted projects. More than one of the judges commented on the fact that the number of great projects made the judging process more of a challenge than they had expected.

There's no question that Philips did a great job of promoting and supporting the contest, so thanks to Sarah Ward and Kevin Gardner for keeping things running smoothly on their end.

Sure we're still a long way from offering Circuit Cellar in the language of your choice, but that doesn't mean you can't earn the respect of designers and developers around the world. Take a look at page 7 and finish your Z183 design by January 15 and you'll be on your way to winning international honor (and some prizes that are a lot more practical than an Olympic medal).

EDITORIAL DIRECTOR/PUBLISHER Steve Ciarcia

MANAGING EDITOR Rob Walker

**TECHNICAL EDITORS** Jennifer Belmonte Rachel Hill Jennifer Huber

WEST COAST EDITOR Tom Cantrell

CONTRIBUTING EDITORS Mike Baptiste Ingo Cyliax Fred Eady George Martin George Novacek

NEW PRODUCTS EDITORS Harv Weiner **Rick Prescott**

PROJECT EDITORS Steve Bedford Bob Paddock James Soussounis David Tweed

ASSOCIATE PUBLISHER Joyce Keil

CHIEF FINANCIAL OFFICER Jeannette Ciarcia

> CUSTOMER SERVICE Elaine Johnston

> > ART DIRECTOR KC Zienka

**GRAPHIC DESIGNERS** Naomi Hoeger Mary Turek

> STAFF ENGINEERS Jeff Bachiochi Anthony Capasso John Gorsky

> > QUIZ MASTER David Tweed

EDITORIAL ADVISORY BOARD Ingo Cyliax Norman Jackson David Prutchi

Cover photograph Ron Meadows-Meadows Marketing PRINTED IN THE UNITED STATES

#### ADVERTISING

ADVERTISING SALES REPRESENTATIVE Fax: (860) 871-0411 Kevin Dows (860) 872-3064 ADVERTISING COORDINATOR

E-mail: kevin.dows@circuitcellar.com Fax: (860) 871-0411

E-mail: val.luster@circuitcellar.com

Valerie Luster (860) 875-2199

ADVERTISING CLERK

Sally Collins CONTACTING CIRCUIT CELLAR

#### SUBSCRIPTIONS:

INFORMATION: www.circuitcellar.com or subscribe@circuitcellar.com TO SUBSCRIBE: (800) 269-6301, www.circuitcellar.com/subscribe.htm, or subscribe@circuitcellar.com

PROBLEMS: subscribe@circuitcellar.com

GENERAL INFORMATION:

TELEPHONE: (860) 875-2199 FAX: (860) 871-0411

INTERNET: info@circuitcellar.com, editor@circuitcellar.com, or www.circuitcellar.com EDITORIAL OFFICES: Editor, Circuit Cellar, 4 Park St., Vernon, CT 06066

AUTHOR CONTACT: E-MAIL: Author addresses (when available) included at the end of each article.

For information on authorized reprints of articles,

contact Jeannette Ciarcia (860) 875-2199 or e-mail jciarcia@circuitcellar.com

CIRCUIT CELLAR®, THE MAGAZINE FOR COMPUTER APPLICATIONS (ISSN 1528-0608) and Circuit Cellar Online are published monthly by Circuit Cellar Incorporated, 4 Park Street, Suite 20, Vernon, CT 06066 (860) 875-2751. Periodical rates paid at Vernon CT and additional offices. One-year (12 issues) subscription rate USA and possessions \$21.95, Canada/Mexico \$31.95, all other countries \$49.95. Two-year (24 issues) subscription rate USA and possessions \$39.95, Canada/Mexico \$55, all other countries \$85. All subscription orders payable in U.S. funds only via VISA, MasterCard, international postal money order, or check drawn on U.S. bank.

Direct subscription orders and subscription-related questions to Circuit Cellar Subscriptions, P.O. Box 5650, Hanover, NH 03755-5650 or call (800) 269-6301.

Postmaster: Send address changes to Circuit Cellar, Circulation Dept., P.O. Box 5650, Hanover, NH 03755-5650.

Circuit Cellar® makes no warranties and assumes no responsibility or liability of any kind for errors in these programs or schematics or for the consequences of any such errors. Furthermore, because of possible variation in the quality and condition of materials and workmanship of re assembled projects. Circuit Cellar® obtacimas any responsibility for the safe and proper function of reader-assembled projects based upon or plans, descriptions, or information published by Circuit Cellar®. sed upon or fror

The information provided by Circuit Cellar® is for educational purposes. Circuit Cellar® makes no claims or warrants that readers have a right to buil things based upon these ideas under patent or other relevant intellectual property law in their jurisdiction, or that readers have a right to construct or operate any of the devices described herein under the relevant patent or other intellectual property law of the reader's jurisdiction. The reader saumes any risk of infingement liability for constructing or operating such devices.

Entire contents copyright @ 2000 by Circuit Cellar Incorporated. All rights reserved. Circuit Cellar and Circuit Cellar INK are registered trademarks of Circuit Cellar Inc. Reproduction of this publication in whole or in part without written consent from Circuit Cellar Inc. is prohibited.

rob.walker@circuitcellar.com

## NEW PRODUCT NEWS Edited by Rick Prescott

#### PALM COMPUTING DATA OFF-LOADING

The **HandCar** software for palm hand-helds can read and launch HOBO and StowAway data loggers. Data from many data loggers can be stored in the palm device and later offloaded to a PC for graphing, analysis, or exporting to other programs. HandCar allows users to manage data loggers on location using the palm device.

The software provides functions to verify logger operation, view current measurements, and check battery status (for loggers that support this function). During launching, the software synchronizes the data logger clock. HandCar runs on the Palm III, Palm V, and Palm VII organizers. An optional palm-to-PC interface can off-load data to a PC without a docking station.

HandCar software costs \$40.

Allison Technology Corp. (281) 239-8500 Fax: (281) 239-8006 www.atcweb.com

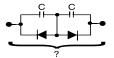

#### LITHIUM-ION BATTERY CHARGER CONTROLLER

The **MAX1737** is a standalone battery charger controller for one to four lithium-ion cells. This device features better than 0.8% battery-regulation voltage accuracy, 90% conversion efficiency, and a complete state machine to safely control the charging sequence.

The step-down, switch-mode DC/DC converter uses a small external dual N-channel FET as a power switch and synchronous rectifier to provide several amperes of accu-

rate charging current and sustain efficiency over a wide input voltage range. An internal voltage regulator powers the IC, allowing operation up to 28 V, and the controllers, ability to work with a duty cycle of up to 98% results in low dropout voltage.

The controller regulates the voltage setpoint and charging current with two loops working together to transition between current regulation and voltage regulation. To service the system load during charging, an additional control loop monitors the total current drawn from the input source. This loop can lower the charging current to prevent overload of the input supply when the system load increases, allowing the use of a low-cost wall adapter.

A built-in safety timer automatically terminates charging after a selectable time limit is reached. Battery temperature is monitored by an external thermistor to prevent charging if the battery temperature is too high or low. The chip charges near-dead cells if the battery voltage is below 2 W per cell. Fast charge, full charge,

> and fault conditions are indicated via LEDs driven by opendrain outputs.

The controller comes in a 28pin QSOP package and is specified for the extended industrial temperature range (-40°C to 85° C). Prices start at **\$2.85** for 1000. A preassembled evaluation kit is available.

Maxim Integrated Products (408) 737-7600 (800) 998-8800 www.maxim-ic.com

8

# NEW PRODUCT NEWS

#### MOTION CONTROLLERS FOR STEPPING MOTORS

With speed, programmable pulse and direction output, and user-selectable profiling modes (S-curve, trapezoidal, velocity contouring, electronic gearing), the **Navigator MC2500** is ideal for applications such as medical automation, materials handling, test equipment, and robotics.

Features include asymmetric acceleration and deceleration, on-the-fly velocity and acceleration changes, trace capabilities for system performance checks and diagnostics, and on-the-fly stall detection. The controller provides multiple

breakpoints per axis to offer precise sequencing and event control by the application program. It accepts feedback from an incremental encoder (up to 5 megacounts per second) or from an absolute encoder or resolver (up to 160 megacounts per second) to read the current axis position.

Input signals include two limit switches (one for each

direction of travel) and one home indicator. One generalpurpose programmable input and output signal per axis is provided. In addition, eight general-purpose analog (O to 5 V) and 256 general-purpose discrete inputs/outputs (16-bit wide) are available.

Consisting of two components, a 132-pin processor and a low-pin logic device, the chipset allows off-loading of resource-intensive motion control functions from the host processor. The instruction set supports more than

130 commands, offering flexibility to designers during application programming.

Engineering samples are available. Prices start at **\$46** in OEM quantities. The Navigator Developer's Kit is offered for **\$995**.

Performance Motion Devices, Inc. (781) 674-9860 Fax: (781) 674-9861 www.pmdcorp.com

# **READER** I/O

#### THAT'S THE WAY I LIKE IT

Normally I don't write to magazine editors, I just show my support by continuing to buy. However, after reading the September issue (122) I am moved to write, and I have to say how great I thought this issue was.

Specifically, there were a large number of complete projects, spanning a whole range of subjects and attractive to people with a range of skill-sets and accomplishment. I know that putting together each article involves a lot of work, and even more work to get it together for each magazine issue. This one was the best yet. Thank you.

#### Andrew Errington

#### SIMPLE AND EASY

Steve's brief comments on the Napster fiasco in your "Imputed Liability?" column (*Circuit Cellar*, 123) was one of the most logical and common-sense treatments of the hoopla that I have seen, anywhere.

I've been a long time reader and as a kid followed Steve's articles on homebuilt weather stations and such in BYTE, I appreciate his common-sense approach to problems. It's very refreshing these days and I am glad that *Circuit Cellar* has retained this philosophy. Keep it up! and thanks for the great mag.

#### Jim Fitzgerald

#### A LITTLE HELP?

Does anyone have a schematic for a programmable pushbutton code lock, hopefully using a PIC?

## Jon Payne jppayne@thepaynes.net

Although we don't object to posting reader questions in this forum, the quickest answers to your design questions may be available on the Circuit Cellar newsgroups, which are accessible from our homepage.

#### ALMOST, BUT NOT ENOUGH

After much anticipation, I received October's issue. My excitement of understanding and possibly using the PCI bus was crushed. It seems the "Catch-

ing the PCI Bus" series has ended with just theory.

I hope Ingo will continue this series because I have a strong desire to build a PCI card and have been pursuing this on my own and I'm making many mistakes.

I started with a Logitech ISA board and added a daughter board so I could play with addressing and the data bus on the ISA slot. Now, I would like to make a PCI card. A guide would be immeasurably valuable. Can someone direct me to a guide for building a PCI card?

#### Trevor Pearce tpearce@dwtunnel.com

#### NAVIGATING A DESIGN CONTEST

After reading Riccardo Rocca's Design99 project article, I think a great competition could be considered which uses Mr. Rocca's chosen application (autonomous GPS). I am thinking of something like a San Francisco to Sydney race, sort of a cross between around-the-world ballooning and engineering school robot wars.

Using dry hull designs and rigid airfoils, extreme seaworthiness could be achieved with craft limited in size to avoid creation of shipping hazards (say, 6 feet and 75 lbs max). A successful entry in this competition would utilize inputs from many disciplines, from oceanography to applied engineering.

To make the completion of the race interesting, a suitably small target would be designated as the finish line. With on-board error-recovery and telemetry provisions, a launch of these intrepid creations might be something like NASA's sending a probe to mars.

#### Jeff Spellman

There are certainly some logistical problems that would have to be overcome for a contest like this to take place, but we thought it would interesting to hear what Circuit Cellar readers have to say.

To get the variety of projects that are submitted for Circuit Cellar design contests, the contests generally specify a processor and not an entire application. However, being a Circuit Cellar reader means you can voice your opinion about the way we do things. What kind of design contest would interest you? Send comments or suggestions to: contest.administrator@circuitcellar.com.

## FEATURE ARTICLE

Brian Branson & David Gonzales

## Wireless Devices

Handling Power Efficiency and Debugging

Facing the increasing demand for integrated wireless solutions, debugging capability and power efficiency have become crucial. Branson and Gonzales address these issues as well as the idea of global standards that will make life easier. s the demand for highly integrated wireless solutions continues to increase, silicon providers respond with a broad array of intellectual property, increasingly dense technologies, and an industry-wide focus on Systemon-Chip (SoC) design tools and integration methodologies. The trend towards reducing the number of components in these systems clearly has the advantage of reducing cost, power consumption, and manufacturing complexity.

On the other hand, product developers are left with the daunting task of creating complex devices with increasingly reduced visibility of subsystem interaction. These devices use programmable microcontroller (MCU) and digital signal processor (DSP) cores coupled with embedded memories and a myriad of peripheral modules on a single chip. The proliferating market of highly integrated systems obviously is increasing the need for improved methods of system validation.

SoC design methodologies for programmable cores now include static debug blocks that may be used during the early stages of product development. By including additional debugrelated capability on-chip, suppliers offer designers the ability to fully understand the behavior of a given system, including validation of both hardware and software architectures and their interdependence. This is essential for evaluating real-time power consumption in Internet-ready hand-held devices.

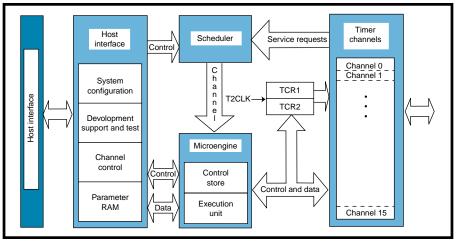

This article explores the issues associated with developing powerefficient hand-held wireless devices and the necessary on-chip debug capability needed for rapid product development. Debugging highly-integrated multiple core systems on a single chip will be discussed using the M-Core M341 micro-RISC processor as an example. We'll also discuss an implementation of a real-time debug port based on the IEEE Industry Standards and Technology Organization (ISTO) Nexus 5001 Forum specification.

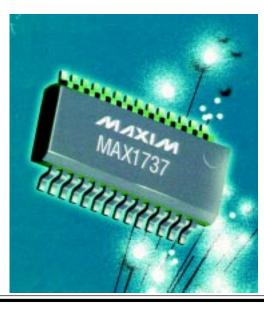

To better appreciate the problems of developing a low-power, high-performance system, let's look at a cellular handset. A digital cellular handset can be partitioned into three main sections (see Figure 1). The RF section receives and transmits analog and digital information; the analog

Figure 1—This is a block diagram of the digital cellular handset. baseband and control section handles intermediate frequency conversion, user interaction, and power control; and the power management section distributes and manages power to all elements of the handset.

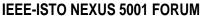

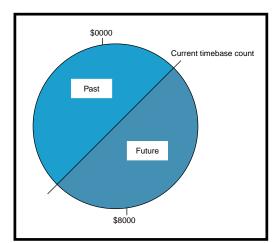

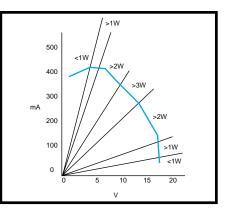

In first and second generation digital cellular solutions, overall baseband power consumption is derived from the combination of standby leakage power, active power for time-based protocol software stacks and data (voice) transmission, and system event power induced by an active page, call, or other user-induced event (see Figure 2). The relative periods of standby and active power can be calculated accurately based on knowledge of the wireless protocol. Hence, standby power consumption can be estimated via leakage current information for a given technology and the amount of time the chip stays in this inactive mode.

Active power consumption is more difficult to estimate. But, for repetitive software stacks performing known protocol functions, this too can be accurately determined. Consider then the problem of estimating and optimizing on-chip power consumption during user-induced events such as WAP browsing, high-speed down/up link transactions, or Motion Picture and Entertainment Group (MPEG) structured audio activity.

The embedded system contains all the necessary capability to perform these functions, even in parallel with other events, but their behavior is less deterministic. The software that is written to handle this multitude of system activity must be carefully opti-

mized to improve battery life for a particular application. Prior studies indicate that the three main blocks of the cellular handset each consume 15 to 50 mA of current depending on their states of activity (see Table 1).

#### **REAL-TIME ANALYSIS**

Lab bench analysis of prototype systems permits conventional methods of evaluation such as circuit boards with logic analyzer Table 1—Check outthe power consump-tion numbers.

| Task           | Digital power | Analog power | RF power |

|----------------|---------------|--------------|----------|

| Network access | 40 mA         | 20 mA        | 40 mA    |

| Call service   | 20–30 mA      | 20 mA        | 50 mA    |

| 3G playback    | 35 mA         | 15 mA        | 20–30 mA |

interfaces. Typically these boards provide a means for initial powerup and integration of software and hardware modules. Each core in the baseband processor chip is evaluated individually in a static debug form; each is put in a special mode of operation that checks its programmer model register and memory while singlestepping a test program (downloaded from a host computer). After the system passes the "smoke test" where each processor exits reset and performs initialization functions correctly, the task of debugging the real-time kernel and interrupt structures begins.

Debugging a real-time wireless device traditionally requires a logic analyzer monitoring an external bus interface where at each clock cycle a sample of bus activity is recorded. But, this is expensive and physically impossible for microcontrollers and DSPs because they operate above 100 MHz.

When bus interfaces are not available, developers embed printf statements at strategic points. So, data needed is sent to a peripheral port and retrieved by a host processor. The information is minimal and creates intrusive delays in the application. As software layers became more complex, this method became too time-consuming. Now, microcontroller developers are demanding reliable and cost-effective solutions from suppliers.

During the past two years, a consortium of companies has worked diligently to address the issue of real-time debugging of highly-embedded systems. The automotive, telecommunications, and network appliance industries have driven this effort to reduce time to market for new products. The consortium began with five companies and has grown to more than 25 participating in the definition of a specification, which is now governed by the IEEE-ISTO Nexus 5001 Forum. Current participants include Accurate Technologies, Motorola, Embedded System Products, Hitachi, Mitsubishi, Hewlett Packard, Ashling Microsystems, and more.

The IEEE-ISTO Nexus 5001 Forum's goal is to define a common set of microcontroller on-chip debug features, protocols, pins, and interfaces to external tools that can be used by realtime embedded application developers. At this time, revision 1.0 of the specification serves as the model for future on-chip debug resources implemented by silicon vendors.

The forum is comprised of four groups. The business group constructs and coordinates activities among the companies involved. Companies in the technical group create specifications and coordinate technical activities with the other groups. The third group

> concentrates on validation. This bunch of companies develops verification methodology for the architectures and tools. The final part of the forum is the API group, which is charged with developing abstraction layers and a software interface for tools and silicon. [1] One major objective

One major objective of the forum is to help development tool ven-

Figure 2—This demonstrates the characteristic power consumption for the cellular handset.

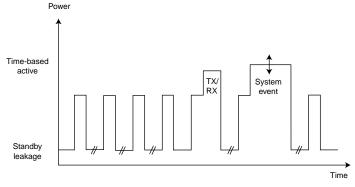

Figure 3—The dual-core cellular handset baseband transceiver is shown here.

dors more easily provide a standard set of tools that may be used on a number of embedded microcontrollers. In the spirit of reusability, many semiconductor vendors have been recognized for having debug ports and tool sets that sufficiently address the static debug requirements of their architectures.

Providing a cost-effective yet powerful migration path to a standard set of dynamic debug features is one of the key goals of the forum. More than 70% of leading embedded microcontroller vendors have dedicated circuits and pins that assist in new product development based on the IEEE 1149.1 Joint Test Action Group (JTAG) four-wire serial interface.

The JTAG pins and protocol help developers with static debug methodologies in a master/slave mode, but there are no means for the embedded microcontroller to initiate real-time information transfers to a host computer. The Nexus standard addresses this need with a scalable set of features whereby existing debug blocks may be used with an extensible auxiliary port.

The features associated with this new auxiliary port focus on real-time transfer of information to and from the embedded microcontroller.

The Nexus 5001 Forum has categorized static and dynamic debug features according to class levels to address various levels of development needs. These classes provide a means for implementing a scalable debug architecture that can address different market segment requirements. Also, it should be noted that when a product is in development, you want to have as many debug features as possible because of constraints of time to market. After a device is

put into production, however, it may not

be necessary or desirable to have all the development features and pins. You may save by implementing a scalable debug port that meets only the requirements needed for specific stages of the product life cycle.

#### EMBEDDED PERFORMANCE

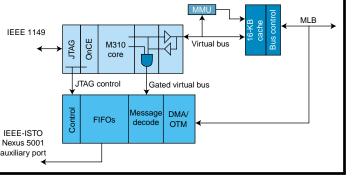

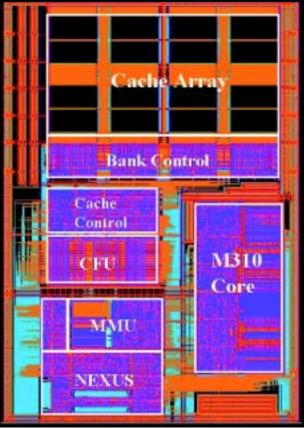

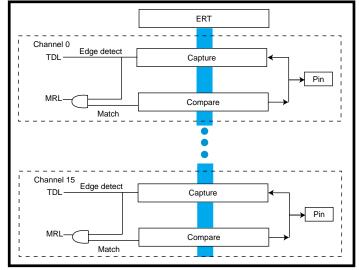

As stated, the heart of the cellular handset is the baseband transceiver that performs all computations relative to call service, Internet web interaction, and handset control. Figure 3 shows a block diagram of a Motorola wireless baseband processor, including separate MCU and DSP core complexes interfaced to separate on-chip RAM and ROM memories and core-specific peripheral and I/O functions.

In order to understand each core's operation and the way cores interact, you should pin-out the internal core buses to external pads, thus achieving good visibility of core bus cycles. However, because of the desire to reduce I/O and package costs, this becomes prohibitive. Nonetheless,

#### WAP DEBUG

Rather than elaborate on the details of the IEEE-ISTO Nexus 5001 specification, we're going to evaluate some of the needs of debugging an Internetready handset. The WAP architectural specification focuses on optimizing for efficient use of device resources. But the task of providing a communications protocol as well as an Internet protocol layer dictates that the RAM be 1 to 4 MB and the flash ROM, which holds the kernel, be 256 to 512 KB.

Because the number of external accesses to RAM directly affects power consumption, the microcontroller engine must have an efficient instruction set, resident cache, and Memory Management Unit (MMU) to reduce external bus transactions. One of the important power consumption goals is to write the handset code so that it efficiently uses the cache.

After the cache and MMU are enabled, the interaction of the core and cache is no longer visible unless there is a cacheable instruction or data miss resulting in an external access to fill the cache. This problem is aggravated when you must debug code that exhibits abnormal behavior in real time or there is a need to capture power measurements when running specific code.

The M-Core M341 architecture implements a Nexus 5001 port for accessing user resources using a highspeed output port to transmit realtime program and data information.

The feature set of the Nexus 5001

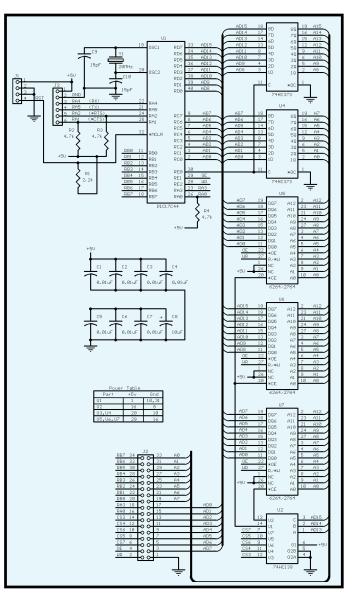

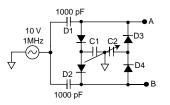

port is from Class 3, providing static debug capability and real-time process identification, program trace, data trace, and read/write access to M-Core Local Bus (MLB) resources. An efficient mode of transmission must be used so that realtime 32-bit address and data values are reported through a 2- to 8-bit output port (see Figure 4).

Figure 4—Here's the M-Core M341 processor with the Nexus 5001 debug port.

14 Issue 124 November 2000

#### APPLYING REAL-TIME FEATURES

A set of data packets commonly referred to as public messages in the Nexus 5001 specification has been defined for efficient transfer of debug information between the embedded processor and a development system. Public messages consist of a transfer code, or TCODE, source processor identification number, and the data associated with the particular feature being accomplished. The key ingredient of public messages is

their efficiency, which means packets may be variable in length depending on the TCODE.

A JTAG serial interface controls messaging capability. The interface couples with a OnCE static debug block and provides access to all Nexus 5001 registers on the M-Core M341 processor. Messaging is enabled prior to deassertion of the reset pin so that exit from reset can be monitored.

| Dimensional of the Construction of the Cons |          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| N/I         All         All <th>10.000</th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10.000   |

| NI         All                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10.000   |

| All         Holes (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 1000, (= 100,          | 10.000   |

| Alia         Bit Torm         Bit Torm         Bit Torm         Control           See Anna 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10.000   |

| State         and an         mail and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10.000   |

| Prime         Intern State         Control         Other         Description         Description <thdescription< th="">         Descrip is and instrument in the scrip</thdescription<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10.000   |

| MH         JUN         T         F         Example limits         SULP         P         4-01         E3P         F           Nm         3         5         6         5         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6 </th <th></th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| New<br>Party         24/2         1         6         6-min.         24.9         6         6-min.         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9         44.9 <th< th=""><th></th></th<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

| 247 3L74 8 8 6-conc. Name 31520 87 118 6-01 119<br>497 312 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1000     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

| C20 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | A STREET |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . AL . N |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -        |

| 790 - 5 10.2 010 D. 100 D.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3 4      |

| 794 5 X X X X X X X X X X X X X X X X X X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| 258 - 7 34.8 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2 1      |

| 200 4 4 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| 790 B B B B B B B B B B B B B B B B B B B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

| 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11111    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

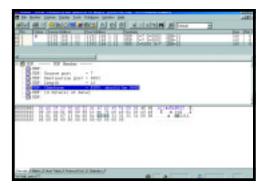

Photo 1—HIWave's Hi-WARE debugger and the Tektronix TLA714 trace buffer are shown here.

#### MONITORING PROGRAM FLOW

Program behavior includes changes in the program counter because of branching, jumping to subroutines, and servicing interrupts and exceptions. Analysis shows that 12 to 13% of instructions executed in a program are change of flow. Therefore, it is not necessary to report every instruction's address, rather only the change of flow. Where you are relative to a reference start address and where you are heading when you change program flow should follow the source listing.

Three types of public messages provide program flow behavior. Real-time operating system (OS) debug must have a means for reporting a process ownership identifier. The Ownership Trace Message objective is to give the current value of the data bus when a process writes to a special address (user base address). This is where Nexus 5001 snoop logic comparators cap-

ture the data bus. Thus, whenever a context switch of the OS occurs, a process identifier may be transmitted using the ownership trace message. This is a key part of correlating virtual-to-physical address maps of the MMU while sending messages to the source level debugger.

Branch trace messages report when direct or indirect branch instructions are executed. The difference in the

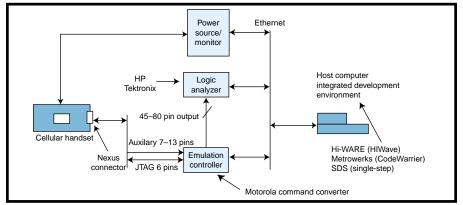

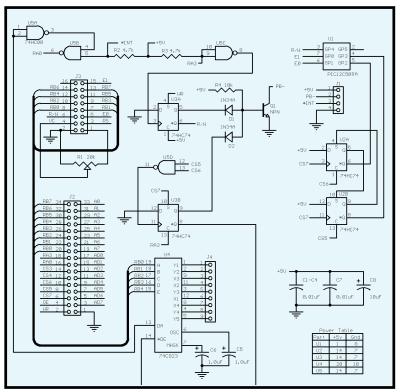

Figure 5—Here's a real-time debug environment.

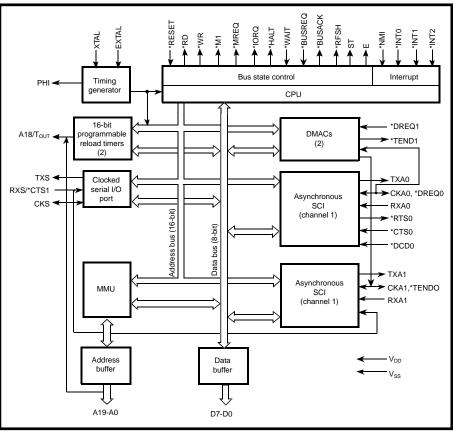

messages is that during a direct branch, the only information needed is the number of instructions executed since the last change of flow. A reference address using a synchronization message is normally transmitted to discover the program counter's location. After that occurs, all references are made to that address until an indirect change of flow occurs. This reduces the number of bits transmitted in a message. Indirect branch messages report the number of instructions executed since the last change of flow and the address where the program counter is jumping to, thus establishing a new reference address.