# CERTIFICATIONS

# #118 MAY 2000 EMBEDDED APPLICATIONS

**Dallas 1-Wire Weather Station**

Embedded Networking at the Racetrack

DALLAS

**Equipment Grounding**

Home Controlled Heating Systems

# **CIRCUIT CELLAR**

Double your technical pleasure each month. After you read Circuit Cellar magazine, get a second shot of engineering adrenaline with Circuit Cellar Online, hosted by ChipCenter.

# — FEATURES —

# Making the Change

# From Standalone to Internet Appliance

# Edward Steinfeld

Plenty of devices have made the transition from standalone product to Internet appliance, but Edward looks at why you might consider making the change in your next project and how you can get the most out of Internet appliances.

# **Recycle Your Code**

# **Conversion and Optimization Techniques**

# Stephen Bowling

Portable code and design reusability have become increasingly important as designers are given shorter design cycles and time-to-market goals. As Stephen explains, the PIC18Cxxx architecture lets you get more mileage out of your programming efforts.

# The SHARC in C

# Mike Smith

In a recent project, Mike set out to develop DSP algorithms suitable for producing an improved sound stage for headphones. Using the Analog Devices 21061 SHARC, he modified the phase and amplitude of the audio signal before it is sent to the ear, thus creating "virtual" speakers that give the effect of listening via room speakers.

# **Resource Links**

• Real Time Clocks and How to Set Them • Rugged Data Storage Bob Paddock

# **Test Your EQ**

**8 Additional Ouestions**

# - COLUMNS -**Considering the Details**

# **Looking Good** Using a Graphics-Based LCD Module

Bob Perrin and Tak Auyeung Advances in technology have brought graphics-based LCDs into the budget range of many embedded applications. Unfortunately, graphics modules aren't as easy to work with as the ubiquitous character-based display. Using C, Bob and Tak explain what it takes to implement a graphics-based module.

# Lessons from the Trenches **Embed This PC**

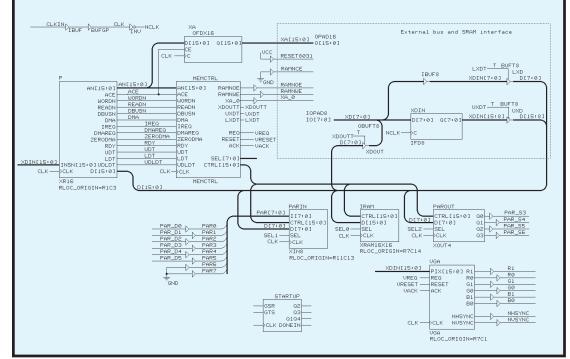

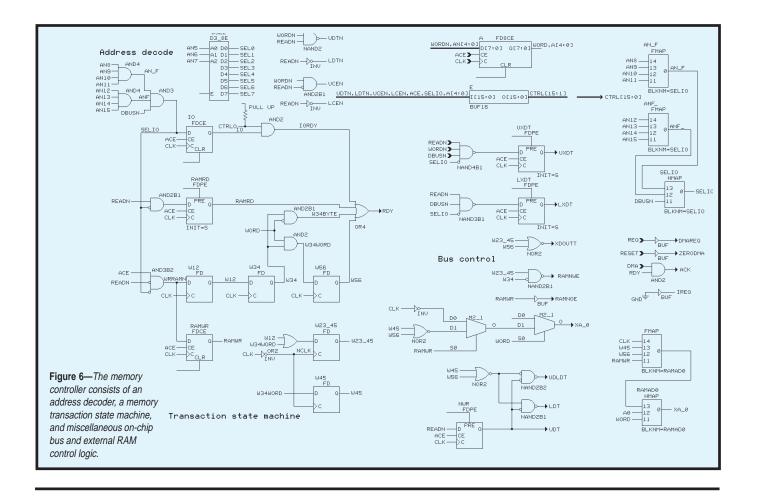

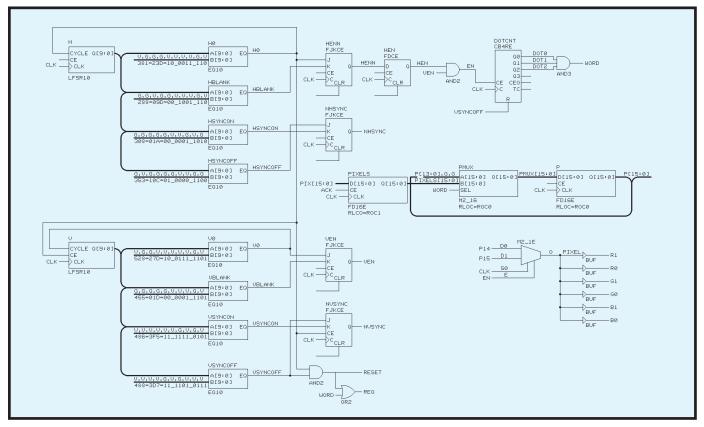

# Part 4: Designing Peripherals In

George Martin

George has covered the CPU options and selected DRAM and BIOS flash memory devices for the embedded '486 project. In the final part of this series, he ties it all together and takes a look at what kinds of peripherals you might want to add on.

# Silicon Update Online

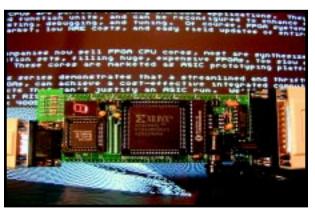

### The Retreat of Silicon Tom Cantrell

Most of the attention being paid to the march of WWW.CIRCUITCEILLAR.COM/ONLINE Table of Contents for Annie of silicon is focused on the mega-chips. But, Table of Contents for April 2000

Let us help keep your project on track or simplify your design decision. Put your tough technical questions to the ASK US team.

The ASK US research staff of engineers has been assembled to share expertise with others. The forum is a place where engineers can congregate to get some tough questions answered, or just browse through the archived Q&A's to broaden their own intelligence base.

|    | 10                                                                                       |                   |                                                                                                       |                                                       |    |

|----|------------------------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----|

|    | 10 A Reliable Network for Embedded Systems—Getting on Track<br>Val Popescu & Gary Gibson |                   |                                                                                                       |                                                       |    |

|    | 18 The Shocking Truth About EMC<br>Part 2: Practical Application<br>George Novacek       |                   |                                                                                                       |                                                       |    |

|    | 28                                                                                       |                   | <b>ather Data—</b> Getting More Than One Wire's Worth<br><i>lliam Beals &amp; Russell Chadwick</i>    |                                                       |    |

|    | 32                                                                                       |                   | <b>ying Power—</b> A Low-Cost Power Supply<br>bert Kondner                                            |                                                       |    |

|    | 36                                                                                       | Par               | i <b>lding a RISC System in an FPGA</b><br>t 3: System-on-a-Chip Design<br><i>Gray</i>                |                                                       |    |

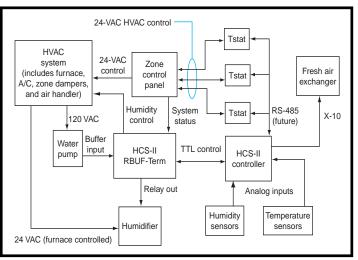

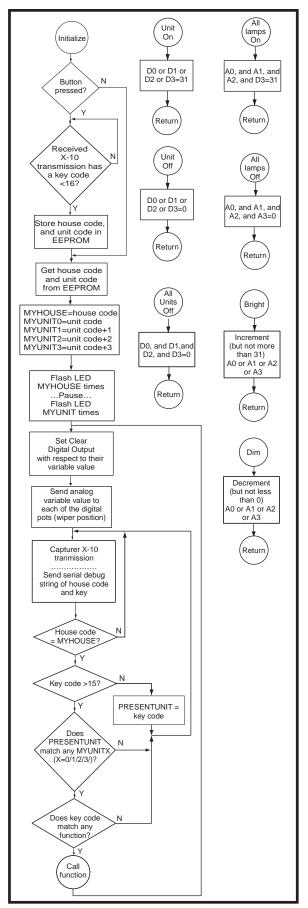

|    | 68                                                                                       | HC                | bedded Living<br>CS = Heating Control System?<br>ke Baptiste                                          |                                                       |    |

|    | 60                                                                                       |                   | <b>MicroSeries</b><br>Op-Amp Specification—Part 2: Getting Some Input<br><i>Joe DiBartolomeo</i>      | Task Manager                                          | 6  |

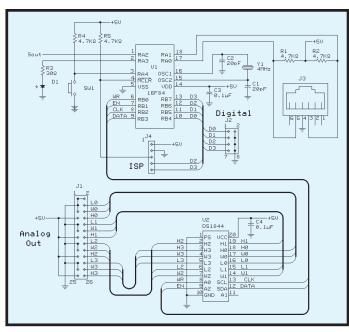

|    | 74                                                                                       | ±.                | From the Bench<br>Digital and Analog Output Control                                                   | Rob Walker<br>It Takes All Kinds                      |    |

|    |                                                                                          | _                 | Taking Route X-10<br>Jeff Bachiochi                                                                   | New Product News<br>edited by Harv Weiner             | 8  |

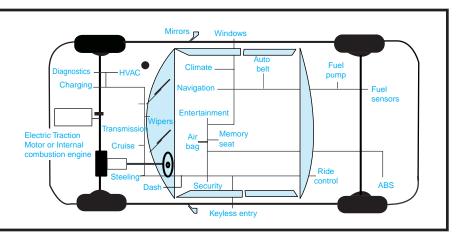

|    | 78                                                                                       | ±.                | Silicon Update<br>On the Road Again<br>Part 1: Going Places with Silicon<br>Tom Cantrell              | Test Your EQ                                          | 83 |

|    |                                                                                          |                   |                                                                                                       | Advertiser's Index<br>June Preview                    | 95 |

|    |                                                                                          |                   | SIM                                                                                                   | Priority Interrupt<br>Steve Ciarcia<br>Publishing 101 | 96 |

|    | MBEDD                                                                                    |                   |                                                                                                       | 7                                                     |    |

|    |                                                                                          |                   |                                                                                                       | 1 < ( )                                               |    |

| 48 | 8 Nouvea<br>edited                                                                       |                   | C<br>Harv Weiner                                                                                      |                                                       |    |

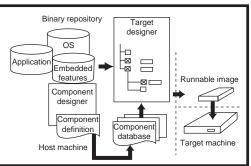

| 50 | ) rpc                                                                                    | <b>Rea</b><br>Par | al-Time PCs<br>al-Time Executive for Multiprocessor System<br>t 1: Introduction to RTEMS<br>to Cyliax |                                                       |    |

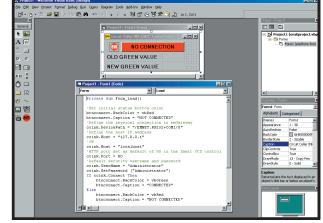

| 54 | <b>4</b> APC                                                                             | Uno<br>Par        | plied PCs<br>der the Covers<br>t 2: Applications via NT Embedded 4.0<br>d Eady                        |                                                       |    |

# TASK MANAGER

# It Takes All Kinds

e recently circulated a personality test here at *Circuit Cellar* to see what kind of people it takes to put the magazine together. I took the test, and the results came back negative. Well, not exactly, but I'm not sure how to take the news. The test said I was, among other things,

logic oriented, contemplative, thoughtful, and a "typical computer geek." Looking at the characteristics of other personality types, I see that all of the characteristics for the other five personalities are definable terms like extrovert, impatient, loyal, and so on. It seems obvious that whoever came up with this test should add "often stereotypical" to the list of his or her character traits. It's a good thing that I also happen to be a person who "prefers to avoid confrontation," otherwise I might have considered making a visit to the Smell & Taste Treatment and Research Foundation in Chicago where this test originated.

No doubt, there will be some of you who read this and get excited. ("A typical computer geek? All right, he's one of us!") To those of you who may be a little leery about subscribing to a magazine with a typical computer geek as the Managing Editor, relax. The personality test revealed that we also have a few perfectionists on board and even a few "generally successful people" here at *Circuit Cellar*. Now, tell me that isn't reassuring.

If there were a point to all of this, it would be that it takes a variety of people to put the magazine together each month. Anyone who follows our columnists can tell you that.

Tom enjoys monitoring the march of silicon and keeping us posted on what's new and how it effects us. This month he takes us under the hood to explain how the latest automobiles are networked. Ingo likes to dig in and explore the details of topics like GPS, FPGAs, and in this issue, he kicks off a series on RTEMS. Fred Eady knows how to appreciate the simple things in engineering, and each month he preaches that, "It doesn't have to be complicated to be embedded." No matter how much you love your cubicle, Mike Baptiste's home control ideas can make your home a better place to be. And, whether Jeff's riding the elevators here at HQ to test accelerometers or continuing the *Circuit Cellar* tradition of home control coverage via X-10, he always brings us something useful from the bench.

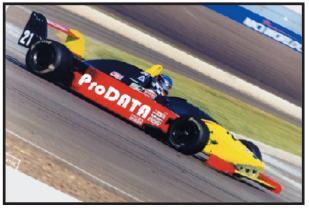

Our monthly themes help provide variety among the feature articles each month, too. This month's theme, Embedded Applications, covers everything from network nodes in high-performance racecars to a weather station that uses amateur radio to transmit weather data to the Internet. Coming up in the second half of the year, you'll be seeing Robotics, Internet & Connectivity, and Wireless Communication issues, to name a few. There will be plenty of great project articles on a variety of topics.

We can't be everything to everyone, but in response to your suggestions, we added a few new themes this year. It's time to set up next year's editorial calendar, so if you have a topic you would like to see covered in 2001, drop me an e-mail. After all, we don't want to forget those people who are "easily bored with routine."

rob.walker@circuitcellar.com

EDITORIAL DIRECTOR/PUBLISHER Steve Ciarcia

MANAGING EDITOR Rob Walker

TECHNICAL EDITORS Jennifer Belmonte Rachel Hill Jennifer Huber

WEST COAST EDITOR Tom Cantrell

CONTRIBUTING EDITORS Mike Baptiste Ingo Cyliax Fred Eady George Martin Bob Perrin

NEW PRODUCTS EDITOR Harv Weiner

PROJECT EDITORS Steve Bedford Janice Hughes Elizabeth Laurençot James Soussounis David Tweed ASSOCIATE PUBLISHER Sue Skolnick

CIRCULATION MANAGER Rose Mansella

CHIEF FINANCIAL OFFICER Jeannette Ciarcia

> CUSTOMER SERVICE Elaine Johnston

> > ART DIRECTOR KC Zienka

GRAPHIC DESIGNER Mary Turek

STAFF ENGINEERS Jeff Bachiochi John Gorsky

> QUIZ MASTER David Tweed

EDITORIAL ADVISORY BOARD Ingo Cyliax Norman Jackson

Norman Jackson David Prutchi

Cover photograph Ron Meadows—Meadows Marketing PRINTED IN THE UNITED STATES

### ADVERTISING

ADVERTISING SALES MANAGER Bobbi Yush (860) 872-3064 ADVERTISING COORDINATOR

Fax: (860) 871-0411 E-mail: bobbi.yush@circuitcellar.com

E-mail: val.luster@circuitcellar.com

Valerie Luster (860) 875-2199

ADVERTISING CLERK

RK Sally Collins

CONTACTING CIRCUIT CELLAR

Fax: (860) 871-0411

# SUBSCRIPTIONS:

INFORMATION: www.circuitcellar.com or subscribe@circuitcellar.com TO SUBSCRIBE: (800) 269-6301 or via our editorial offices: (860) 875-2199

GENERAL INFORMATION:

TELEPHONE: (860) 875-2199 FAX: (860) 871-0411

INTERNET: info@circuitcellar.com, editor@circuitcellar.com, or www.circuitcellar.com EDITORIAL OFFICES: Editor, Circuit Cellar, 4 Park St., Vernon, CT 06066 AUTHOR CONTACT:

E-MAIL: Author addresses (when available) included at the end of each article.

For information on authorized reprints of articles,

contact Jeannette Ciarcia (860) 875-2199 or e-mail jciarcia@circuitcellar.com.

CIRCUIT CELLAR<sup>®</sup>, THE MAGAZINE FOR COMPUTER APPLICATIONS (ISSN 1528-0608) and Circuit Cellar Online are published monthly by Circuit Cellar Incorporated, 4 Park Street, Suite 20, Vernon, CT 06066 (860) 875-2751. Periodical rates paid at Vernon, CT and additional offices. One-year (12 issues) subscription rate USA and possessions \$21.95, Canada/Mexico \$31.95, all other countries \$49.95. Two-year (24 issues) subscription rate USA and possessions \$39, Canada/Mexico \$55, all other countries \$45. All subscription orders payable in U.S. funds only via VISA, MasterCard, international postal money order, or check drawn on U.S. bank.

Direct subscription orders and subscription-related questions to Circuit Cellar Subscriptions, P.O. Box 698, Holmes, PA 19043-9613 or call (800) 269-6301.

Postmaster: Send address changes to Circuit Cellar, Circulation Dept., P.O. Box 698, Holmes, PA 19043-9613.

Circuit Cellar® makes no warranties and assumes no responsibility or liability of any kind for errors in these programs or schematics or for the consequences of any such errors. Furthermore, because of possible variation in the quality and condition of materials and workmanship of readerassembled projects, Circuit Cellar® disclaims any responsibility for the safe and proper function of reader-assembled projects based upon or from plans, descriptions, or information published by Circuit Cellar®.

The information provided by Circuit Cellar® is for educational purposes. Circuit Cellar® makes no claims or warrants that readers have a right to build things based upon these ideas under patent or other relevant intellectual property law in their jurisdiction, or that readers have a right to construct or operate any of the devices described herein under the relevant patent or other intellectual property law of the reader's jurisdiction. The reader assumes any risk of infringement liability for constructing or operating such devices.

Entire contents copyright © 2000 by Circuit Cellar Incorporated. All rights reserved. Circuit Cellar and Circuit Cellar INK are registered trademarks of Circuit Cellar Inc. Reproduction of this publication in whole or in part without written consent from Circuit Cellar Inc. is prohibited.

# NEW PRODUCT NEWS

# INDUSTRIAL CONTROLLER

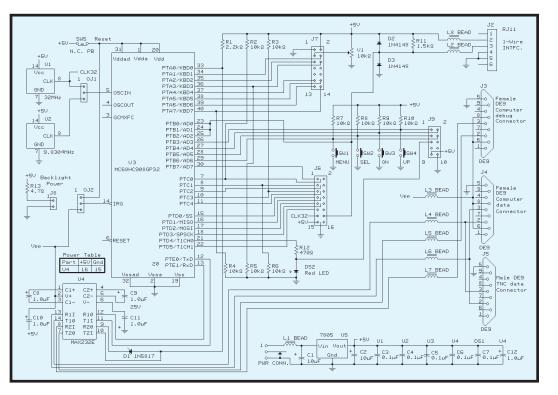

The **RPC-2350G** is an industrial controller with EL or LCD graphic display capability. Its numerous analog, digital I/O, and counter lines make it a core processor for OEM applications. A built-in programming language supports graphic functions and I/O. Applications for the controller include instrumentation, analysis, and industrial machine control.

Analog I/O consists of eight channels of 12-bit A/D, two channels of D/A, and four 20-mA outputs. Its 49 digital lines are used for pulse outputs, counting, and timing. A 24-bit counter connects to a proximity sensor, quadrature encoder, or 20-MHz pulses. Frequency and pulse width measurements are possible. Pulse outputs are provided. Nine high-current lines drive

solenoids, relays, LEDs, and small motors. Two RS-232/485 network ports are available. An SPI port connects to a variety of external devices.

It has 512 KB of battery backed RAM and 512 KB of supported flash memory. Its battery-backed real-time clock and RAM run for about three years. Programs are stored in flash memory, while formulas, constants, and recipes can be stored in RAM or flash memory. Power requirements are 5 V or 7–30 VDC.

CAMBASIC (an event-driven, floating-point, multitasking programming language) speeds program development. Programs are downloaded using a serial port, then the CAMBASIC operating system compiles and runs the programs. Application programs that show how to use the major functions are included.

The RPC-2350G model includes EL and LCD graphics ports. The RPC-2350 model doesn't include

the graphic display port or regulator. Both models include a character display port. Pricing starts at **\$375** in single quantities.

> Remote Processing (800) 642-9971 Fax: (303) 690-1875 www.rp3.com

# NEW PRODUCT NEWS

# **RISC-BASED C-ENGINE**

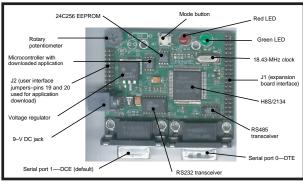

The **ADPI C-Engine** is a lowpower compact RISC-based Cengine that can be used in applications where multiple serial ports, analog inputs, analog outputs, digital I/O, and onboard memory storage are required. Applications include environmental and wastewater, test and measurement, control and data acquisition, SCADA, and portable or stationary applications.

Its compact size is ideal for OEMs needing to add features to existing products. The engine can develop new designs. The ADPI C-Engine is expandable with add-on modules available from ADPI or with proprietary designs based on customer specifications. The system can be programmed using the GNU shareware compiler, which eliminates the need to license a BIOS or operating system. Software libraries are provided by ADPI.

The C-Engine features an H8/3006 processor with 256 KB of onboard flash memory (upgradeable to 2 MB). A compact flash slot that supports up to 64 MB and an onboard 16-bit memory I/O expansion is provided. There are eight 10-bit A/D ports or six 10-bit A/D and one 8-bit D/A port. Its LCD display port supports parallel LCDs up to  $4 \times 40$ , and its keypad interface supports up to  $3 \times 4$  matrix. An input voltage of 2-3 VDC battery or 6-20 VDC is required. The ADPI C-Engine costs \$188.

Analog & Digital Peripherals, Inc. (937) 339-2241 Fax: (937) 339-0070 www.adpi.com

# FEATURE ARTICLE

Val Popescu and Gary Gibson

# A Reliable Network for Embedded Systems

Getting on Track

Getting a low-cost and reliable embedded network on track can be quite a chore. Val and Gary put together a system of network nodes that is not only on track, but on *the* track—in a high-performance racecar! Let's take a ride with LogNet. here are communication protocols for nearly every combination of speed, media, data structure, distance, and cost. The novelty of another protocol would probably be lost on most engineers unless it addresses a rather peculiar application space.

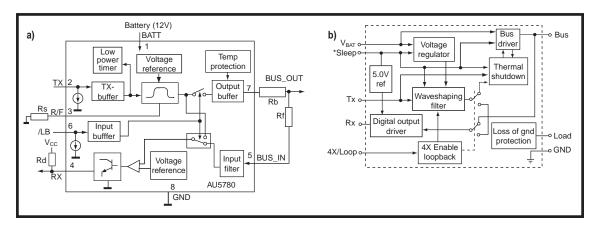

The LogNet protocol and implementation was initially conceived for connecting data acquisition and control modules in a high-performance racecar. The environment is characterized by intense electrical and magnetic noise, heat, vibrations, little power availability, and tight spaces. The physical layer used was the RS-485 standard. The cost of a network node was under \$7, with a halfinch square of board space (inserted in the cable itself). The power needed was between 10 and 20 mW.

The biggest developmental challenge was making the network hardware and protocol implementation sufficiently robust to keep the network running in the harsh environment. Fault-tolerant methods are employed to trace and checkpoint transactions to resume operation without data loss after network node faults. While Cyclic Redundancy Check (CRC) ensures corrupted packets are retransmitted, data integrity must be preserved even in the event that the node fails and is subsequently restarted by a watchdog timer (WDT).

A combination of polling and token passing ensures that each node can become master and control the network. A specially designated Hub node ensures fairness by preventing idling nodes from unnecessarily taking control of the network access.

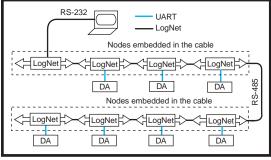

Although initially developed for a specific racecar application, the fault-tolerant, low-power, low-cost net-work can find much broader use in industrial and automotive applica-tions. Because of the small size, the network interface can be embedded in the network cable (see Figure 1).

# LOGNET HIGHLIGHTS

The cost, power, and size of the node efficiently carries event-driven (instrumentation, control) and constant data rate (telemetry) messages. There is a high reliability and fault tolerance for harsh environments.

A multilevel priority access scheme supports devices with widely varying data rates and required response times. It implements a client/server protocol with peer-to-peer capabilities by using master/slave and tokenpassing media access methods. Also, there is a token-passing mechanism where the Hub controls the token advance signal going to all nodes.

The efficient network firmware uses less than 2 KB for the network Hub and less than 1 KB for the other network nodes.

# LOGNET PROTOCOL LAYERS

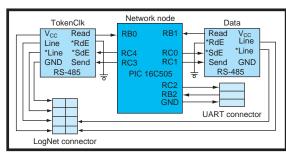

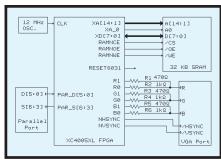

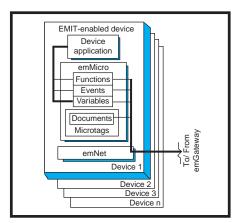

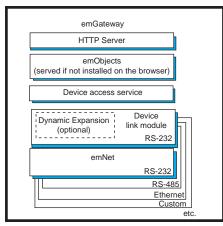

LogNet's physical layer consists of two RS-485 electrically-compliant twisted pair signals: Data and TokenClk. In Figure 1, each node has a RS-485 port and a UART (point-topoint) link to the companion module.

The basic concept of the data link layer is a virtual bus using a master/ slave methodology. The network uses a Hub that serves as the primary master and arbitrator, allowing for multilevel prioritized network access. The Hub also allows for simplified central diagnostics. Data is transferred through network transactions initiated by the current master and executed by the addressed slave either by responding with data or acknowledging data transfer.

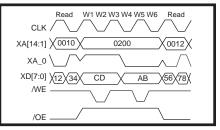

A network transaction is a sequence of one or more discrete framed packets where each packet is a string of characters. These packets are framed by being delimited with symbols and special two-character sequences. Each packet contains CRC data to detect corrupted transmissions.

Serial data is transferred asynchronously on the Data signal in a subframe, using a standard UART format synchronized with start and stop bits. The TokenClk signal is generated by the Hub and read by the other network nodes. TokenClk synchronizes token passing in the network's multimaster mode. In addition to that, TokenClk can be used by the Hub to force a current master to relinquish its master state, enforcing network access prioritization and determinacy.

The network transaction packets are divided into fields that define command opcode, the NID of destina-

tion node, control bits, and the message payload carried for the application layer, followed by a two-byte CRC. These packets are delimited by one- or two-byte symbols, beginning with a packet header and ending with a packet trailer. Request, response, and acknowledgement packet headers and trailers use unique symbols.

# **PACKET DEFINITIONS**

The three different packet types are request, response, and acknowledgement. Request packets initiate a network transaction and may contain network data as part of the data link layer protocol, an application message in the case of a write request, or the information necessary to a read operation. Response packets carry application messages or network data from a slave to the current master.

Acknowledgement packets are transmitted by the data recipient to complete the transaction reliably. Figure 2 shows the packet formats.

Network addresses (NIDs) consist of an 8-bit byte allowing addressing of up to 255 nodes. Request packets start with a destination NID byte, then a Command byte, followed by a CtrlLen byte. The Command byte specifies the operation to be performed. The CtrlLen byte uses two fields specifying control information and the number of bytes to be read or written. Zero to 32 data bytes follow, ending in a two-byte CRC. Longer application messages require multiple transactions.

Response packets start with a Slave End byte that uses two fields specifying the status of the transaction and the number of bytes read. Slave End is followed by 0 to 32 bytes of data, ending in a two-byte CRC. The Slave End byte also may indicate that the request packet was corrupted.

Slave End provides status that may include a request to the current master to initiate another transfer with

Figure 1—In a LogNet application, the Data Acquisition (DA) modules are connected via UART links to network nodes embedded in the cable.

four levels of priority: low, medium, high, and urgent. This status mechanism allows a slave that needs to transfer additional data to secure the network for a longer period of time. The Hub also may use this information to temporarily raise the network access priority of the current master.

Acknowledgement packets contain only an AckStatus byte and a twobyte CRC, and are issued to complete a transaction or to indicate that the previous write request or read response was corrupt (see Table 1).

# NETWORK TRANSACTIONS

Completing network transactions transfers data. The current master with a request packet initiates all network transactions. In the case of a read command, the addressed slave replies with a response packet. After the master successfully receives the read response, it issues an acknowledgement packet. In the case of a write, the addressed slave replies with an acknowledgement packet. Most of the commands in Table 1 that aren't labeled as read or write are write requests transmitting network data. The addressed slave acknowledges

> them. If any packet becomes corrupted or lost in transmission, the entire transaction is restarted.

Protocol guarantees delivery of one copy of each application message or network data in the order they are transmitted. Because a corrupted acknowledgement could cause retransmission of the original packet, duplication is avoided by using

| Command      | Description                                             |

|--------------|---------------------------------------------------------|

| Write NID    | Assign an NID to a node, addressed by Manufacture ID    |

| Read NID     | Read the NID of a node, addressed by Manufacture ID     |

| Read         | Read 1 to 32 bytes                                      |

| Write        | Write 1 to 32 bytes                                     |

| Read P       | Read 1 to 32 bytes, allow partial reads                 |

| Write P      | Write 1 to 32 bytes, allow partial writes               |

| Set TokenID  | Set the system in "Token" mode and the current Token ID |

| Cancel Token | Cancel "Token" mode                                     |

| Sync         | Synchronize a node (soft reset)                         |

| Quiet        | Suspend a node's activity (stand by)                    |

| Wake Up      | Resume the node's activity                              |

Table 1—Here's a list of the network protocol commands used for request packets.

| Framing<br>Header symbol Trailer symbol                                  |  |

|--------------------------------------------------------------------------|--|

| UC HC Packet UC TC                                                       |  |

| UC = Unique character<br>HC = Header character<br>TC = Trailer character |  |

| Request packets                                                          |  |

| Dest NID Command Ctr1Len 0 - 32 Bytes                                    |  |

| 2-byte CRC                                                               |  |

| Response packets                                                         |  |

| Slave End 0 - 32 Bytes 2-byte CRC                                        |  |

| Acknowledgement packets                                                  |  |

| Ack status 2-byte CRC                                                    |  |

|                                                                          |  |

Figure 2—LogNet uses media access protocol framing and three packet formats.

a duplicate transmission bit in the command byte.

# MEDIA ACCESS CONTROL

The two modes used by LogNet protocol to control media access are polling and token passing. They assume that one of the nodes is declared master while the rest are relegated to slave status.

The network initialization firmware running in the Hub is provided with a configuration file containing the unique manufacturer ID of each of the nodes. From this information, the Hub assigns consecutive NIDs to each node in the system. The application in the Hub can also set the network access priority of each node. After initializing the network, the Hub becomes its first master.

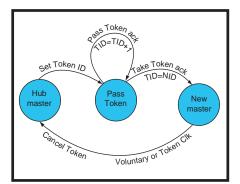

The token-passing mode allows for multiple masters. The Hub manages the token-passing protocol. Figure 3 shows the protocol's main states. The Hub sets the network in the tokenpassing mode by broadcasting a packet to all nodes to set the current Token ID. This mode is maintained until mastership of the network is accepted by one of the nodes taking the token.

While in the token-passing mode, the Hub generates the TokenClk signal. Each time a rising clock edge is received by the network nodes, they increment an internal Token ID counter. When the Token ID counter equals the NID of the node, the node either accepts the token and assumes control of the network by issuing a TakeToken packet or passes the token by issuing the PassToken packet.

When a node takes the token and becomes the new master, it initiates network transactions as in the polling mode until it voluntarily relinquishes or the Hub forces it to relinquish its master state. The Hub can activate the TokenClk line, causing the TID to increment and thus be different than the node's NID. This alerts the master to pass the token back to the Hub with a CancelToken packet. The Hub then restarts the token-passing mode using the SetTokenID packet and activates the TokenClk signal, allowing the token to be passed to the next possible network master within the priority scheme.

The Hub implements additional error-handling procedures to deal with lost or duplicated tokens, which happens when a node fails to pass a token or token-passing packets are corrupted.

# FAULT TOLERANCE

All data transfer transactions include acknowledge packets that report CRC errors. Corrupt packets are retransmitted a number of times (user defined). If packets are still corrupt, the current master sends a message to the Hub asking it to take control and run diagnostics to isolate the point of failure. The failing node (or nodes) is logically removed from the network.

Each node implements a watchdog timer routine that is called each time the node hangs. The routine checks the transaction queues and the current transaction status in order to resume and complete the transaction. If no internal registers are corrupted, the nodes participating in the transac-

**Figure 3**—This figure shows the token-passing mechanism. The Hub issues TokenClk, which makes all nodes increment the Token ID (TID). When a node notices a TID equal to its Node ID (NID), it tells the Hub to stop the TokenClk and acquire master status.

tion will see only a delay in finishing the transaction. If the node isn't able to safely resume the transaction, it terminates the transaction with an error acknowledgement. To safely resume suspended transactions, the nodes trace and checkpoint the progress of transactions.

The Hub sends a synchronization packet when the network is idle (and has master status) just to make sure all the nodes are up and working. If a node does not respond to a synchronization packet within a defined time interval, the Hub assumes that the node failed. Then, the failing node is removed from the network.

The Hub maintains a network activity timer. If the Hub has not seen any message for a period of time, it assumes the current master is idling or has failed and forces the node to relinquish the master status. If there is no response, the Hub assumes the current master failed in the worst possible way, and it drives the network. In this case, the Hub records the fault and cycles the power to the nodes, followed by network initialization and diagnostics.

# **ENSURING FAIRNESS**

Ensuring fairness in accessing the network is the goal of most protocols. LogNet provides the token-passing mechanism to give each node a chance to become master. Fairness also assumes the master will surrender its position, giving the chance to another node. The Hub can also enforce a time-slicing policy by asking the current master to surrender its position at the end of the transaction in progress if it held the position longer than the preset time slice.

# PHYSICAL IMPLEMENTATION

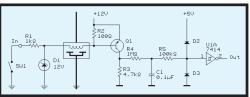

Figure 4 shows the implementation of a node using a Microchip PIC microprocessor. To reduce the power requirements, the chip's sleep mode is activated each time the node surrenders its master position. The chip is awakened by a change on an input pin. The power consumption in standby mode is less than 5  $\mu$ W and in operation is less than 10 mW (at 5 V). The power can be supplied by the

Figure 4—This is the network node implementation that you can insert right into the network cable.

companion embedded module or by the network cable.

Port B is used for reading in all three data lines: TokenClk Read (RB0), Network Data Read (RB1), and serial link RXd (RB2). Port C is used for output: Network Data Send (RC1), serial link TXd (RC2), and Network Data Send Enable (RC0). In addition, the master drives the Token Clock: TokenClk Send (RC3) and TokenClk Send Enable (RC4). The serial link is implemented as UART or SSP (see Figure 4 and Photo 1).

The interface node firmware uses less than 1k instructions and less than 60 8-bit registers, whereas the Hub uses almost 2k instructions. The data transfer rate is largely determined by the operating speed of the RS-485 and the clock speed of the microcontroller implementing the node. Peak data rates of up to 4 Mbps can be reached.

# APPLICATION EXAMPLE

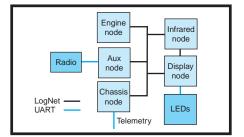

The first application of this network was with a Formula Atlanticseries racecar. The networked units were two data acquisition modules (Engine and Chassis), a steering wheel mounted LCD and warning LED lights, an infrared beam receiver, and an auxiliary unit for adjusting the brake bias, power shifting (shifting without lifting off the throttle), and voice messages (see Figure 5). The data transferred on the network included status of the steering wheel buttons, messages for the display and the voice unit, turning on or off the LED lights (engine alarm, lap time progress, etc.), wheel speed, engine RPM, and so on.

The Chassis module was designated as the Hub. It uses its UART link for data downloading to a PC and telemetry. Each node has an application using data transferred by its media access layer.

Broadcast messages are often used. For example, many processes in the system are indexed by time (beginning of a lap) and by the car's position on the track, which is calculated by multiplying the number

of wheel revolutions by the wheel circumference.

The Chassis node is connected to a wheel sensor that generates a signal for each wheel revolution and is in charge of maintaining the car's position data. Because other nodes needed to know the car's position, the Chassis node broadcasts a new wheel revolution message to other nodes on the network. Similarly, the node receiving and decoding the infrared beam that marks the beginning of a lap broadcasts a new lap message. The Engine node has the engine RPM data, which is useful to other nodes hence it also broadcasts on the network.

Many functions in a racecar are critical in terms of the well being of the car and driver. So, maintaining the operational network is critical.

The Engine node collects engine parameters (oil and fuel pressure, etc.) and compares them to preset limits. If one of the engine parameters is offlimit, the Engine node grabs the token to become master and sends a message to the Display node, which formats and displays the parameter in question on the LCD screen and flashes the alarm LEDs.

The Engine node also sends a message to the Auxiliary node, which composes a voice message ("Oil pressure too low") and feeds it into the car radio. Most racecars are not allowed

Figure 5—Here's an overview of the racecar system.

Photo 2—Talk about a quick application. This is the Formula Atlantic racecar that was used during LogNet development.

to have electronic driver aids such as ABS or traction control. But, it is useful to alert the driver that, while braking, the wheels lock up more than necessary or that the simultaneous application of throttle and brakes exceeds a set threshold and could cause premature brake fade. Or even worse, the throttle is slow in returning to idle, indicating a potentially disastrous throttle-stuck condition.

The operating environment can best be described as hostile. Keeping electronics, especially microprocessors, functioning is tough when competing with intense EMI and RFI noise.

In the early tests, getting closer than 3' from a car with the engine running caused the prototype system to freeze. After implementing the watchdog timer in all microprocessors and adding all known means of suppressing noise, we were able to install the system and start the engine without instant failure. Running the car on the track added another level of error detection and recovery. In the end, the firmware was implemented and debugged to deal with errors and error recovery before all the network main functions were installed.

Val's wife (who drives a Cosworthpowered Sports Racer in the ACRL pro-series) drove the LogNet-enabled car during development so we could reprogram the microprocessors between track sessions (see Photo 2). During development, an internal WDT counter (which counts how many times the watchdog timer restarts a node) revealed that the system occasionally froze. The radio push-totalk button status is transferred over the network, so the driver knew when the network stopped because she noticed that the crew didn't respond to her call. After the protocol's fault-tolerance was implemented, the system operated without losing data and the driver observed continuous operation of all functions.

The low-power consumption is also appre-

ciated by the battery, which uses a weak alternator so it doesn't rob the engine of too much power. Running a six-wire (two data-line pairs, power and ground) cable is a huge benefit given the extreme space and weight constraints in the racecar. Also, implementing the UART protocol for data download and telemetry is faulttolerant. Disconnecting the UART cable stops communications. Reconnecting the cable resumes communications with no data loss. The racecar application posed a challenge in terms of power, space, and a noisy environment that perhaps can be found in other embedded applications.

Val Popescu, the founder of ProDATA Microelectronics, spent more than 10 years as president of Metaflow Technologies, the company credited with inventing the modern version of outof-order execution architecture. Gary Gibson worked with Val at Metaflow and was in charge of engineering. Both Val and Gary switched careers from the high-end 32-bit multimillion-transistor microprocessors to low-end networks implemented with an 8-bit microcontroller. You may reach Val at val@prodatam.com.

# SOURCE

### **PIC16C505** Microchip Technology (888) 628-6247 (480) 786-7200

Fax: (480) 899-9210 www.microchip.com

# The Shocking Truth About EMC

George Novacek

# Part 2: Practical Application

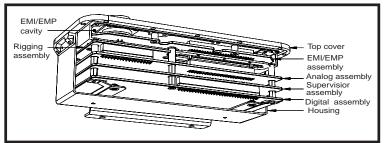

Having covered the principles of EMC in Part 1, this month George sets out to show us how to keep everything in mind when designing electronic equipment. If you design electronic equipment, here's a handy ounce of prevention. n overview of the aspects of electromagnetic interference and immunity was presented in Part 1 of this article. Part 2 will present practical ways of designing electronic equipment to successfully handle these aspects.

# GROUNDING AND POWER DIS-TRIBUTION

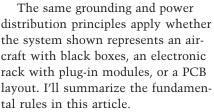

The importance of proper grounding can't be overstated. The principles are straightforward, but the implementation may cause headaches. Figure 1 shows the arrangement of a typical small system with three separate controllers.

Each module has a single point where all the internal grounds (power returns) converge. No power return can be shared with other modules, therefore, analog and digital circuits have separate grounds. This single point connects to the chassis.

EMI filters and transient protection devices return current to the chassis. Externally, power and power returns are not shared. This equally applies to the external I/O connections, which should have their own returns.

Chassis ground provides safety (EMI and lightning strike return), not for power or signal return. However, this rule is often violated. Cable shielding is terminated to the chassis.

And lastly, the internal grounds must be as low impedance as possible, preferably ground planes. Grounding (bonding) connection between the individual units and the chassis ground must be less than 3 m $\Omega$  and maintain low impedance well above 20 GHz. Numerous methods are used, such as woven copper straps and grounding fingers.

Figure 1 also illustrates the headache that driving external devices can cause. The problem is that you rarely have control over the selection of external devices and their installations. For example, cars use chassis for power return from solenoids, re-

lays, control switches, and such. Some loads may have their own power return, such as shown with the dotted line in

**Figure 1—**The wiring of a small system with distributed processing is shown here.

Figure 1. Whether a low-side or a high-side load is driven, it has a tendency to introduce unwanted current paths. You must carefully identify and control these paths or they will create ground loops and degrade the performance of the expensive EMI protection scheme.

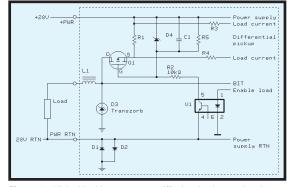

### POWER SUPPLY

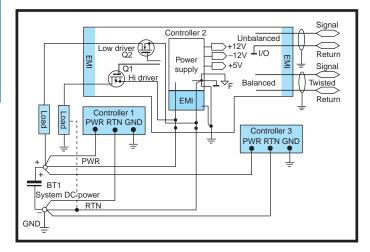

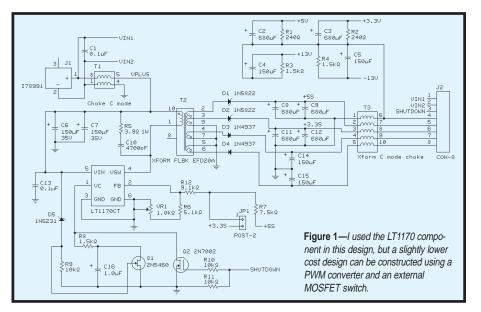

Let's start discussing the inner design by focusing on the power supply. Not long ago, with the abundance of three-terminal linear regulators, designers started treating power supplies as an afterthought. Yet, there is more to the efficient, reliable power supply than the regulator. Although getting an inexpensive, reliable linear or switching regulator to satisfy most requirements is nearly hassle-free, the power-supply module remains the critical part of the design. The power supply in Figure 2 will stand up to the toughest requirements.

At the core of this module resides a purchased switching regulator (I discovered it's seldom worth designing your own). In demanding applications, a dual-cavity design will be used. The box around the regulator and two feedthrough filters depicts this. The regulator is inside the clean cavity, with the conditioning circuits outside in the dirty cavity. Commonly, the regulator will be packaged in its own sardine can to minimize its radiated interference with internal circuits. In less-demanding applications, some parts can be eliminated, such as the clean cavity, filters F1 and F2, and the pre-regulator represented by Q1 and surrounding circuits.

I'll describe the circuits to clarify the design philosophy. First, the reason for two 28 VDC and corresponding return terminals lies in critical systems' requirement that a power interrupt of up to 1 s doesn't affect the unit's operation (remember the info from Part 1 for Category Z, *Circuit Cellar*, 117, p. 29). In many cases, the necessary storage capacitor would

never fit within the equipment envelope. Therefore, aircraft systems use two independent power buses, relying on the probability that an outage will not happen in both simultaneously. The buses are ORed through diodes D1 and D2 to prevent propagation of one bus fault into the other.

Although simple, this method's drawback makes it unacceptable in critical applications. If one of the diodes fails, the fault will remain undetected or dormant until its associated power bus goes, and then the entire system fails.

Notice that the power return flows to the switching regulator in the clean cavity without being anywhere connected to the chassis or internal ground. The switching regulator is fully isolated from its secondary, as is required in sensitive systems where no less than a 10-k $\Omega$  resistance between the chassis and the power return is permitted to minimize ground loop currents. For such systems, the isolated switcher is the only practical solution. In less demanding systems where DC resistance can be low as long as a sufficient impedance exists

at high frequencies, capacitor C6 is replaced with a short, connecting the return from the regulator to the ground. All the grounds and power returns converge there.

Diodes D3 and D4 connected between the power return and the chassis make sure the return will not swing more than one diode drop away from chassis ground when exposed to a strong electric or magnetic field, or lightning strike. When sizing diodes D1, D2, D3, and D4, remember that they will have to bear the full brunt of lightning transients, which can be 1600 A forward and several thousand volts in reverse bias. Five ohms is considered representative of the lightning source as seen by the electronics.

Transients on the 28-V power line are clamped by D5 to approximately 100 V. Depending on the level of threat the power supply must survive, D5 may have to be replaced with a gas discharge tube (spark gap). L1 can be replaced in less demanding systems with a small resistor. The series impedance is needed to limit the transient current through the clamp D5, but the voltage drop over a resistor may present an operational problem. Consider the lowest operating voltage, subtract the voltage drop across D1 (or D2), L1 (or a resistor in its place) plus Q1, and it may be difficult to select an off-the-shelf switcher that will work through the entire operating voltage range.

The following circuit comprising Q1, Q2, and Q3, is a series pass preregulator that helps the power supply smooth over the 80 V, 100 ms

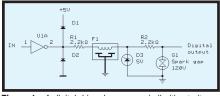

Figure 3—Analog signal drivers are pictured here.

Figure 4—A digital driver has many similarities to its analog counterpart.

long transient as required for Category Z equipment (similar to MIL-STD-704 military requirement). Q1 is maintained fully conductive for input voltages below 32 V and clamps everything above back to 32 V. Tranzorb D7 on its output, clamps remnant transients and protects the expensive switching power supply in case of a preregulator failure.

The preregulated supply voltage enters the clean cavity through two low-pass  $\pi$  feedthrough filters. Their primary purpose is to cut down interference generated by conducted emissions of the switching power supply. But, filter size is inversely proportional to its critical frequency. To keep emissions under control in a small envelope, a supply with a 500 kHz or greater switching frequency is needed. Good grounding and ample ground planes are indispensable.

Balun T1, in the clean cavity, minimizes common-mode interference generated by the switcher and conducted to the outside world. Using it will bring conducted EMI under control. Finally, the function block called "Power monitor and watchdog timer" can be built with one or several MAX chips. It consists of several voltage comparators, which shut down or reset the system when input or any output voltage goes outside their predetermined limits.

The watchdog timer is a standard feature of many monolithic system supervisors. It is reset continuously by the microprocessor as it executes code. If the micro freezes, theoretically the timer won't restart within its usual time interval of several milliseconds, and will attempt to revive the program by forcing reset. The feature is usually included for free, so there is no reason not to use it. However, the watchdog timer's reliability of operation is not acceptable for critical systems or as the sole monitor.

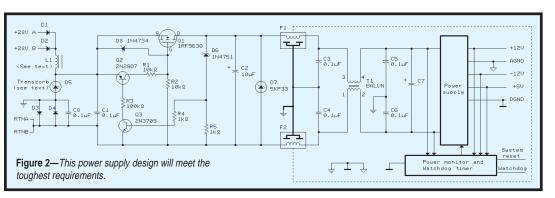

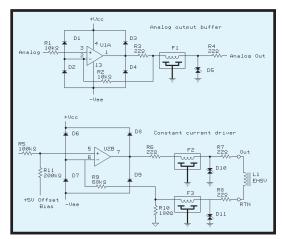

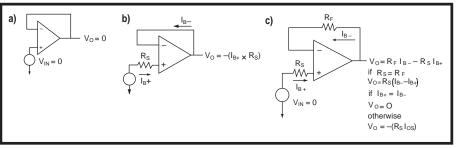

# ANALOG OUTPUT DRIVERS

A control system often drives analog loads. Figure 3 shows interfacing analog loads. The analog output buffer will work well where output impedance of approximately 22  $\Omega$  is acceptable. Reduce the series load and implement a two-stage protection (see Figure 4) for greater loads.

The output resistance is determined by R4, which limits the current into bidirectional tranzorb D5. Tranzorbs are like Zener diodes, but faster and capable of dissipating higher pulse loads. They are available as unidirectional, analogous to a single Zener, and bidirectional, which can be viewed as opposite-series connection of two Zeners.

An inductor can replace the signal voltage drop across R4 if it's too high, as long as the working bandwidth is retained. Resistor R3, also in the signal path and usually of the same value as R4, does not contribute to the voltage drop because it is compensated by the negative feedback introduced by R2. R4's purpose is to limit the current into the IC output drivers if the voltage exceeds (plus or minus) the supply rails. D1, D2, D3, and D4 make sure no pin voltage exceeds the supply rail by more than one diode drop. Filter F1 is a low-pass  $\pi$  filter, which in demanding systems is a feedthrough between the dirty and clean cavities.

The resistor described here limits the current that can flow through the transient protection device, whether it is a tranzorb or a spark gap. Note that the popular metal film resistors are unsuitable for this purpose because they can't withstand high voltage. Because the carbon resistors are nearly extinct, wire-wound devices are practically the only choice.

The constant current driver also shown in Figure 3 is typical of a balanced output driver using the same design elements as the unbalanced driver above it. The driver takes analog 0 to 5 V, centered at 2.5 V from a digital-to-analog converter (DAC) and puts out  $\pm 10$  mA current into a load from 0 to 1000  $\Omega$ . This would be a typical interface for an electrohydraulic servo valve (EHSV). Before leaving the subject of analog drivers, revisit Figure 1 and remember that the signal returns of the unbalanced outputs and unbalanced inputs need their own returns. They would be treated the same way as the RTN line in the Constant Current Driver (see Figure 3), except that D11 would be replaced with two opposite parallel diodes (such as D3 and D4 in Figure 1), and R10 would be replaced with a short to the appropriate signal ground.

# **DIGITAL OUTPUT DRIVERS**

There is not much difference in driving digital loads, as in driving analog loads. The elements of the circuit shown in Figure 4 are similar to the analog drivers in Figure 3.

Here, a spark gap is shown as part of the two-stage protection of the output line. Why are they necessary? It's a combination of the maximum threat that must be protected against, the energy a tranzorb can dissipate, and the maximum value of the series resistor that can be used based on the load requirements. In this case, I used 2.2- $\Omega$  series resistance. An inductor in place of R2 would adversely affect the signal bandwidth. Because the output line must survive a lightning transient of 1600 V/1600 A, the spark gap, which fires when the voltage reaches about 120 V and then clamps it and holds at approximately 24 V, handles the responsibility. The wiring resistance provides the current limit for the spark gap. The tranzorb in the second stage looks after the remnant pulse, with the filter cutting off the remaining narrow pulse resulting from the finite time the clamping devices need before they conduct.

Remember, once spark gaps fire, they keep conducting in the presence of a DC voltage greater than 24 V. This may present a design challenge when protecting a power supply.

**Figure 5**—Interfacing a panel indicator with the controller is more complicated than it appears.

Why use clamps (such as tranzorb D3 in Figure 4) and still use signal diodes D1 and D2 to protect the IC pin? In many applications, the tranzorbs are sized to allow full swing of the IC output voltage. In the example above, this would be 5 V. A 5-V tranzorb, due to tolerances and poor transfer characteristics, will clamp the incoming transient caused by ESD, lightning, and such to approximately 7 V or 1 V (depending on the polarity of the transient). This is high enough to damage the IC running at  $5 V_{cc}$ . You may decide to rely on the internal ESD protection existing in many of today's ICs. On the other hand, if the design robustness is important to you, for a few more pennies, add the two signal diodes.

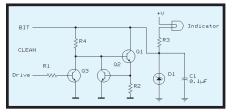

# **INDICATOR DRIVER**

So far, the design has been straightforward, more interesting circuits are coming up. Many controllers have remote indicators such as panel lamps. Driving them properly is complex despite apparent simplicity. Figure 5 shows a typical implementation of such an indicator circuit, with features applicable to all the driver circuits discussed here.

This is a low-side driver with several atypical twists. For standard applications, multiple monolithic driver packages with internal overcurrent protection and built-intest (BIT) are available. The external interface, R3, D1, and C1 are the same as in the previous circuits. They clamp the incoming transients to a safe level that is determined by D1. The low-pass filter isn't here, but in a two-cavity design, the reliable  $\pi$ feedthrough would be inserted between R3 and Q1. Placing the driver circuit in the dirty cavity (depending on the power return requirements) and filtering the low signal level BIT and Drive lines entering the clean cavity is another option.

R2 and Q2 perform current limiting for short circuit protection of the driver. The BIT signal can be used to disable the driver if an overcurrent condition occurs. Q1 must be able to dissipate the short-circuit power (full supply voltage × maximum current is equal to 0.55V/R2) indefinitely, or for the period of time it takes the microprocessor to energize Q3 and remove drive current from the base of Q1 if BIT is used to disconnect it. Or, Q2 may be replaced with a latch.

Note that this fault indicator must be

illuminated when the controller is not functioning, including when its power is off. The driver is energized through R4, thus the indicator lamp is illuminated by default. This is why bipolar transistors with merely 0.55-V base-emitter voltage are better suited than a MOSFET. The controller keeps Q1 de-energized like a dead-man's switch through Q3.

BIT monitors the status of the driver in response to the drive commands. Therefore, it detects problems like a burnt or missing lamp or short circuit.

The momentary overcurrent situation which occurs when driving an incandescent lamp is a common trap of this application. When the lamp is turned on, its onrush current exceeds (for a short period of time) 10 times the nominal current value. The BIT circuit and especially power-up diagnostics must allow sufficient time, approximately 100 ms, for the lamp current to settle down before reporting a problem or turning off the drive current. For Q1 to function properly, it must be rated to survive full short-circuit dissipation for that length of time.

Figure 7—This is a standard low-side driver with overcurrent protection.

Figure 6—High-side drivers are more difficult to implement than lowside drivers, yet they have some important advantages.

The next section will analyze power drivers and crucial design issues of power and return. The same considerations given to the power drivers must be given to all external load interfaces.

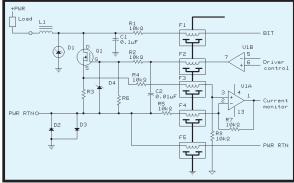

# **HIGH-SIDE DRIVER**

High-side drivers use a few more components than their low-side cousins, but are popular with system designers for two reasons (see Figure 6).

First, some systems (e.g., automotive) use a chassis for the load power return. Second, when wiring fails it is likely that the connection will break or the line will short to the chassis. This means MOSFET Q1 (short-circuit protected) can't energize the load, but often this is the preferred default in case of a failure. The same fault occurring to the low-side driver will cause the load to be energized continuously. This failure mode may not be acceptable for safety reasons.

The circuit in Figure 6 uses an optocoupler to drive power MOSFET Q1. The return drive current path would have to go through chassis ground in a system with an isolated switching power supply (see Figure 1).

This is possible, but not a good design practice as far as EMI is concerned. Alternatively, isolation through resistors >10 k $\Omega$ , especially when a non-isolated switcher is used, is a good solution. Isolation amplifiers such as the ones manufactured by Burr-Brown are options.

Similar to other circuits, the load works in series with choke L1 to limit the transient current through tranzorb D3.

R1 connected between the power bus and the source terminal of the power MOSFET monitors the load current for overload protection. As a result of the supply voltage variation between 16 to 32 V, voltage developed across R1 needs to be monitored in a differential manner to suppress the common-mode signal. In addition, an acoustic signal immunity test (a standard requirement) superimposes about 2-V RMS ripple of up to 50-kHz frequency on the positive voltage power bus. Resistors R3 and R4 should be at least 100 k $\Omega$  each to have minimal effect on the power isolation.

For high-power switching such as 28 V/30 A that some electric actuators require, the selection of P-channel MOSFETs is limited. Sometimes it is better to use an N-channel device and monolithic charge pump to generate the needed 10 V higher than the 28-V line to drive it.

# LOW-SIDE DRIVERS

Low-side drivers referenced to the ground are simpler to implement than high-side. The latter's disadvantage is an inability to disconnect the load during a wiring harness short. But, often that's acceptable.

Like high-side drivers, low-side drivers are complicated when maintaining the power isolation needed to prevent ground loops. In Figure 7, the required isolation is degraded only by  $10-k\Omega$  resistors R1, R2, R4, and R5.

The problem these circuits face is that the power return potential may be different from the common internal ground. The solution is simple when using a power MOSFET for Q1. Diodes D2 and D3 ensure the PWR RTN excursions around the ground do not exceed one diode drop. This has no effect on driving the Q1 gate, but would be difficult to handle if Q1 was a bipolar transistor. Make sure the load-current sensing performed by R3 is not affected by the return line noise. Use differential voltage pickup by amplifier U1A.

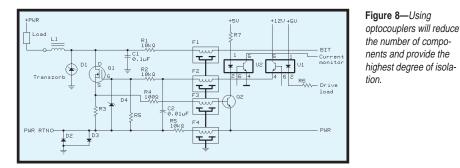

The power drivers usually are located inside the dirty cavity to limit the need for low-pass filters to the signal lines only. Figure 8 shows another approach to driver circuit by using optocouplers. This maintains complete isolation from the primary power bus. The BIT line can be interfaced through an optocoupler, as well.

An optocoupler also can perform the overcurrent monitoring. It can rarely be used alone because of the LED's high forward voltage. In Figure 8, Q2 fixes the problem. Most applications don't need current measurement, detection of exceedance of a threshold usually is enough. In addition to standard current transformers and shunt resistors, new current monitoring devices, such as the ones based on Hall-effect diodes appear daily.

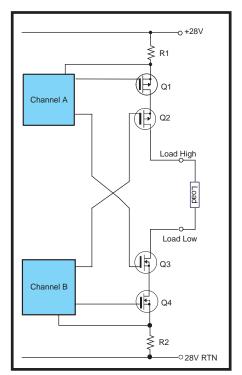

# **TOTEM-POLE DRIVERS**

Although not directly related to electromagnetic compatibility design, a review of output drivers wouldn't be complete without the totem-pole topology. These circuits comprise several high-side or low-side drivers described here as building blocks. Figure 9 illustrates the principle of the full totem-pole driver used in flight-control systems where the design requirement states that "no combination of two faults shall allow inadvertent energization, or prevent de-energization of an actuator."

Even with any two MOSFET drivers shorted, the system can de-energize the load. Controllers using these drivers are at least dual redundant, meaning two parallel processing channels are in action. Triple redundancy would require three series MOSFETs in each branch.

More often this topology is simplified to use only two low- or two highside transistors in series together with dual-redundant processing.

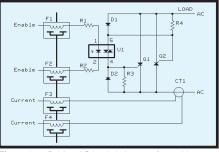

# CONTROLLING AC LOADS

With the increasing selection of power semiconductors such as thyristors, IGBTs, enhancement MOSFETs, and bipolar devices, relays are no longer the only choice for large AC loads. Assuming reader familiarity with the operation of thyristors, I'll concentrate on the EMC aspects.

Figure 10 shows an actual highpower switch in a safety-critical application. Focusing on the EMI issues, the major problem lies in suppression of emissions to the levels satisfying standards such as MIL-STD-461 or DO-160D. A zero-crossing trigger renders the best EMI performance.

This circuit is a reliable design, switching 200 V, 400 Hz, 3-phase 20 kVA to a furnace. Optocoupled triac U1 with internal zero-crossing detector (Motorola MOC 3083) is the reason behind its simplicity. The EMI

Figure 9—No two failures of the power semiconductors will prevent the load from being de-energized.

performance is on par with more conventional and presumably more precise (in terms of zero-cross triggering) circuits using pulse transformers. Its cost and complexity are lower. Because it drives a purely resistive load, it doesn't need a snubber, which would be a series RC network placed in parallel across the thyristors.

The current transformer CT1 performs load monitoring and overcurrent protections. The power circuit is located in the dirty cavity with low-pass filtered interface for control and current monitoring. With the thyristors rated at voltages and currents exceeding the lightning-induced threat, no clamp or other transient protection is needed.

Be prepared for the conducted emission of this circuit to be a problem in the 50- to 200-kHz range where it exceeds maximum levels allowed by MIL-STD-461 by approximately 12 dB. On the 200-V power line, this represents less than 20 mV of the unwanted RF signal, which is lower than the conducted interference levels commercial applications worry about. But, there is no practical solution to reduce this emission.

Thyristors need anode voltage before they can fire so that the latching current can flow and be maintained, therefore triggering at true zero-crossing is impossible. A delay of a few degrees of phase after zero-crossing is needed for sufficient voltage to build up across the device. This voltage is

Figure 11—A collection of input circuits is shown here.

**Figure 10**—Driving AC loads is best performed by optocoupled thyristors.

greater than the anode voltage required by the optotriac, so performance isn't sacrificed by using it. Still, the residual anode voltage of about 6 V peak across the thyristors contains sufficient harmonics to exceed allowed emission limits. A filter with critical frequency low enough for effective attenuation in the offending frequency range while carrying a 100-A load current is impractical to build within a reasonable envelope.

# RELAYS

As discussed, relays will be energized by low- or high-side drivers. Internal relays switching external signals should be placed inside the dirty cavity with tranzorbs to suppress contact sparking, MOVs, and RC networks to protect the contacts and reduce unwanted emissions. Usually, relay coils are equipped with a free-wheeling diode to suppress the back EMF generated by the collapsing magnetic field upon the coil deenergization. Unfortunately, the diode

also will significantly slow down the relay's response. A combination with a Zener diode, capacitor, or resistor will improve the response time at the cost of a larger EMF kickback.

# **INPUT CIRCUITS**

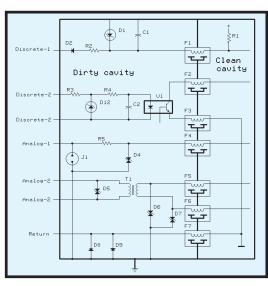

Figure 11 shows how the input circuits use the same principles for EMC and lightning protection as the output circuits discussed in this article. The circuits in Figure 11 provide adequate protection from EMI, lightning, and ESD at the highest threat levels. When dealing with the input lines, recall using signal diodes to protect IC pins by clamping their voltages to within one diode drop of their  $V_{CC}$  and  $V_{EE}$  for output circuits. Use a similar approach here.

Examples will clarify the process. The input line labeled Discrete 1 is a typical active-low input circuit (invert polarities for active-high). R2 provides transient current limiting for tranzorb D1. R1 is a pull-up resistor that will be needed even when the input source does not require one, to ensure known state when nothing is connected to the input. A standard requirement is that discrete lines have a minimum 3-V noise margin. To achieve that, R1, R2, and the following circuits must be carefully selected. Figure 12 shows the different situation when interfacing electromechanical switches.

Ideally, each discrete input should have its own return line, or they should join at the same connector pin, labeled Return in Figure 11. This is not always practical. Many systems use a chassis for return. This will not be a problem with discrete lines as long as the 3-V margin is maintained.

Although tranzorbs are excellent for dissipating high current pulses, depending on the size of R2, they may not withstand sustained short of the input line to, for example, 28 V. Some input sources may have their own pull-up that could turn into a power source for the de-energized controller. Hence, D2 allows the input current to flow in a single direction only. Make sure that the diode takes the reverse voltage and the forward current induced by the lightning transients, and also is fast enough for the signals.

Discrete 2 is an optoisolated interface that cannot be beaten for its simplicity, ruggedness, and isolation properties. Tranzorb D3 limits the maximum current U1 LED will be exposed to and protects it against reverse polarity. The optoisolator's excellent isolation properties guarantee that the input can be left completely floating if desired. Or, its return line can be tied to the chassis through the opposite-parallel diode combination such as D8 and D9 in Figure 11. When you need to interface an analog device such as an LVDT, the approach labeled Analog 1 may be the way to go. Because R5 can't be large enough to limit the transorb D4 current sufficiently, the two-stage protection is used. Analog 2 uses a transformer for isolation. Similar to the optocoupler interface, it can be left floating or tied to the chassis through opposite-parallel diodes. Both the optocoupler and the transformer input are hard to beat when large common-mode input swing or great circuit isolation is needed.

Figure 12 shows the most effective, yet simple interface for electromechanical switches and relay contacts. Mechanical contacts need a minimum current in the range of 10 mA (usually more for the tin-plated type), therefore the interface, comprised of Q1, R1, R2 and R3, is essentially a current-to-voltage converter. A seriesblocking diode can be added in series with R1, like in Figure 11, although it is rarely justified. The 1-k $\Omega$  R1 resistor (no metal film!) limits severe transients well below the peak pulse the tranzorbs can safely take.

R4 and C1 debounce the signal and pass it to a CMOS Schmitt Trigger circuit operating off the internal logic supply. Signal diodes D2 and D3 and R5 ensure the signal at the IC input doesn't exceed safe limits.

Before concluding the subject, I want to emphasize two important aspects of designing EMI/HIRF lightning protection for the I/O lines. First, performing rudimentary calculations presented in Part 1 determines the worst-case interference signal levels that can reach the system. As long as the high-frequency interference signals are reduced to less than one diode drop (set the limit to 100 mV at the highest), there is little chance they will interfere. Shielding, filtering,

Figure 12—Preferably, interfacing electromechanical switches is accomplished with current, rather than voltage, interface.

layout, and packaging achieve the goal. As long as the interference is below one diode drop, the internal circuits' operating bandwidth is limited and outside the interfering signals, the interference will be suppressed and not affect the operation. RF susceptibility usually is the result when the interference signals exceed the base-

emitter junction voltage of bipolar devices. The result is rectification, demodulation, and such playing havoc with the equipment.

Second, design of the transient suppression can have a similar negative effect. While designing the clamps to protect the microelectronics against damage, recognize that the working environment isn't static, but rather with pulses and bursts of RF. Once the clamping voltage is exceeded, the pulses or induced RF bursts will be rectified and result in a DC offset or a demodulated low-frequency signal that will be introduced into the system. Be careful selecting unipolar clamps. They may appear to be the correct choice for TTL signals, but their asymetrical characteristics will be responsible for rectifying interference signals at the controller input as low as one diode drop. This can be troublesome when considering the system's behavioral response to lightning. Repeated bursts of highfrequency oscillations are common.

There are several things that can bring such a situation under control. First, the clamps should be selected at the highest safe voltage to prevent rectification from occurring as much as possible. Ensure the discrete inputs have sufficient noise margin; the analog circuits need large, dynamic range coupled with the common-mode input range and common-mode voltage rejection. And, validate the input signal so that if it is obliterated by interference, the system recognizes it and takes appropriate action (e.g., shuts down). Optocouplers and transformers still are the most effecient tools for bringing EMC under control.

Figure 13—Here's a self-contained controller with a front panel holding connectors and controls. The metal tub that forms the dirty cavity is attached to the front panel from below. All connections between the clean and dirty cavities pass through feedthrough low-pass filters installed in the bottom of the tub.

### CABINETS

Well-designed packaging is an important step towards electromagnetic compatibility. Thanks to continuing miniaturization, multilayer PCBs, and SMT, many commercial products achieve unprecedented EMC performance without special packaging effort. But, when it comes to operation at e-fields exceeding 200 V/m and satisfying the most stringent emission requirements, the dual-cavity design still reigns supreme. Figures 13 shows an example of a dual-cavity cabinet.

I included a reference list regarding the art of electronic packaging design for interested readers.

This two-part article covered aspects of designing electronic equipment for electromagnetic compatibility. In today's environment of increasingly abundant electrical pollution, engineers have a responsibility to design equipment not only immune to such overabundance of interference, but also equipment that will not add any new problems.

George Novacek has 30 years of experience in circuit design and embedded controllers. He is currently the general manager of Messier-Dowty Electronics, a division of Messier-Dowty International, the world's largest manufacturer of landing-gear systems. You may reach him at gnovacek@nexicom.net.

# RESOURCES

- W. Boxleitner, *Electrostatic Discharge and Electronic Equipment*, IEE Press, 1989.

- F.A. Fisher and J.A. Plumer, *Lightning Protection of Aircraft,*

Lightning Technologies, Inc., Pittsfield, MA, 1990. G. Fuller, Understanding HIRF, Avionics Communications Inc., Leesburg, VA, 1995. O. Hartal, Electromagnetic Compatibility by Design, R&B Enterprises, West Conshohocken, PA, 1991.

M. I. Montrose, *EMC* and the Printed Circuit Board, IEEE Press, 1998.

- G. Novacek, *Testing 1, 2*, Circuit Cellar Online, www.chipcenter .com, July–Oct. 1999.

- R. Standler, Protection of Electronic Circuits from Over-voltages, John Wiley & Sons Inc., New York, NY, 1989.

- L. Tihanyi, *Electromagnetic Compatibility in Power Electronics*, IEEE Press, 1995.

- D.R.J. White and M. Mardiguian, Interference Control Technologies, Don White Consultants Inc., Gainesville, VA, 1986.

# SOURCES

**DO-160D** RTCA, Inc. (202) 833-9339 Fax: (202) 833-9434 www.rtca.org

W181 Peak Reducing EMI Solutions Cypress Semiconductor (408) 943-2600 Fax: (408) 943-6848 www.cypress.com

FOR MORE INFORMATION ON DESIGNING AND TESTING EQUIPMENT, CHECK OUT GEORGE NOVACEK'S FOUR-PART SERIES "TESTING 1, 2" IN THE CIRCUIT CELLAR ONLINE ARCHIVE

# Weather Data

# FEATURE ARTICLE

William Beals & Russell Chadwick

# Getting More Than One Wire's Worth

Russell and William rolled a weather station from Dallas and a Motorola 6808-based electronic interface display unit into an award-winning project in last year's design contest. And now, here's an inside look at how the project came together. he weather is a common conversation topic. Now, you can build a weather station that will provide plenty of weather data to discuss. Unlike commercial stations, our approach is less expensive and eliminates the need for a dedicated computer.

In addition to acquiring weather data and displaying it locally, we interfaced the weather unit to amateur radio so the weather data can be sent via airwaves and the Internet. This involves a new and growing part of amateur packet radio called Automatic Position Reporting System (APRS).

Weather data is what interests us here, but information like position data, velocity, and heading data, and telemetry are also carried via APRS signals. Digital repeaters (digipeaters) relay these information packets to extend coverage areas. Some digipeaters function as Internet gateways (I-gates) that relay data to a central server. The packets are collected and sent via the Internet to anyone logged onto the server. This configuration is deceptively simple, yet powerful.

A single I-gate can collect and relay weather information from dozens of weather stations, no matter how remote. If you have a Java-enabled web browser, visit www.aprs.net/usa1.html to see what the coverage looks like in your area. To see the weather data collected by amateur radio operators, go to www.findU.com/wx. To see our data, use calls n0xga for William (Denver, CO) and kb0tvj-5 for Russell (Boulder, CO). More information on this new aspect of ham radio can be found at www.tapr.org.

If you want your data to be available on the Internet, in addition to this project, you will need some other items. The first is an amateur radio license like the technician class license. It has no Morse code requirement, and with it you have access to all amateur bands above 30 MHz, including the 2-meter band (144– 148 MHz), which has most of the APRS activity. You can get more information on amateur radio licenses from www.arrl.org.

You will also need a TNC (Terminal Node Controller) and a VHF radio. The data side of the TNC connects to one of the COM ports of your computer, and the analog side connects to the microphone input and speaker output of the radio. The TNC transfers data back and forth between the computer's digital world and the radio's analog world.

# **BUILD VERSUS BUY**

Professional quality weather stations cost several thousand dollars, but there are citizen weather stations on the market priced from \$300 to \$700. However, we wanted to build a highquality unit that was also inexpensive. Now, there's a challenge! We decided to buy the sensors that measure the parameters (wind speed, wind direction, temperature, pressure, rain, and humidity). But, we built the data interface to acquire data from the sensors and then process and display the weather information.

The solution was around half the cost of the lower-end citizen weather station, and needs no PC. It is entirely digital and can run from a wall transformer or solar power. Only one DC voltage is needed to run the entire project. Because we were in control of the software, we used data processing algorithms to improve the quality of the measurements and reduce error.

# THE 1-WIRE UNIT

As we shopped around for a sensor unit, Dallas introduced a promotional weather sensor unit for \$79 to demonstrate one of their product lines. They have a family of digital sensors and components based on a bus technology called 1-Wire. The sensor unit will be available until at least August of 2000 and is described at www.ibutton.com/ weather/index.html.

The wind speed is measured with a rotating cup anemometer, which is assembled with a shaft connected to the center of an arm with small magnets on either end. Two magnets are used to balance and stabilize the arm, which turns 2400 rpm in 100-mph wind! The magnets pass above a reed switch and cause a switch cycle for each pass. The switch is connected to a 1-Wire counter chip mounted on the circuit board inside the housing. The software samples the counter value at regular intervals and converts the counts to wind speed.

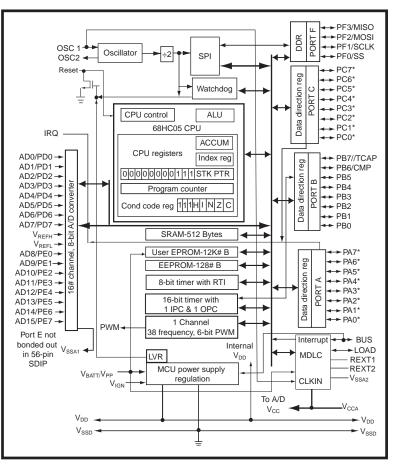

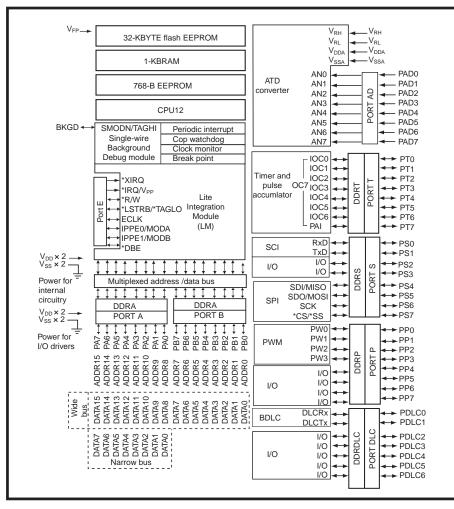

We tested the process in a calibrated wind tunnel to determine the conversion from count number to wind speed. Our tests showed that the anemometer responds to winds of about 1.5 mph.