# THE CONTRACT OF THE OWNER OWNER OF THE OWNER OF THE OWNER OWNE

EarthQuake Data Center

## THE MAGAZINE FOR COMPUTER APPLICATIONS #117 APRIL 2000 SIGNAL PROCESSING

Build a Fast Low-Frequency Meter

Walsh-Hadamard Encoders/Decoders

**Know Your Op-Amps**

**Designing for EMC**

# **CIRCUIT CELLAR**

Double your technical pleasure each month. After you read Circuit Cellar magazine, get a second shot of engineering adrenaline with Circuit Cellar Online, hosted by ChipCenter.

### — FEATURES —

### **Roaming About**

### Wireless Connectivity for Mobile PCs

### Vinit Nijhawan

With all of the advances in wireless technology, it's no wonder that wireless communications is one of the fastest growing industries on the planet. In this article, Vinit takes a look at some of the various public wireless network technologies available today.

### A Well-Lit Sound Check

### **Build a MIDI Adapter with a LED Indicator** Stuart Ball

Is your soundcard MPU401 or MIDI compatible? If you think it is, but aren't sure what that means, then you definitely want to listen up. Stuart explains some of the details of working with and understanding MIDI, and then shows you how to build a MIDI adapter (complete with LEDs) for a soundcard.

### 87C51 Programmer Adapter

### Noel Rios

Programming the 87C51 is easy when you have a dedicated or universal programmer, but such devices certainly aren't free. That's why Noel used an EPROM programmer, crystal, logic IC, and a few other parts to make this simple, inexpensive adapter for programming the 87C51.

### **Resource Links**

### • System Safety

• Metglas (Application of Amorphour Metals) Bob Paddock

### **Test Your EO**

**8 Additional Questions**

### - COLUMNS -

### Learning the Ropes **Design Downloading and Debugging**

Ingo Cyliax

Last time, Ingo designed a simple bi-colored LED project. Using CPLDs and FPGAs is much easier when you understand how they work, so this month he gives us some information on flash-memory based CPLDs and SRAM-based FPGAs before explaining how to download and debug your design (even if it is just a blinky LED project) in a Xilinx FPGA environment.

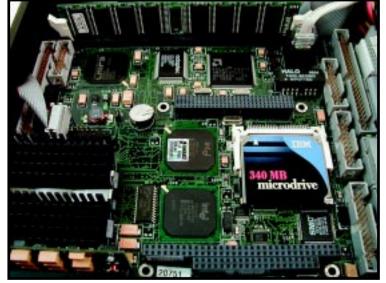

### Lessons from the Trenches **Embed This PC**

### Part 3: Emulator to Application Testing George Martin

Now that George has explained some of the requirements for embedding a '486, it's time to get things going and start testing. Before he's done with Part 3, you'll have a simple design, some startup code for the emulator, and a project.

### Silicon Update Online

### **Analog PLD Anyone?**

Tom Cantrell

We're in the middle of the digital revolution, but according to Tom, 1s and 0s will never overthrow the world as we know it. After all, the world Table of Contents for March 2000

# WWW.CIRCUITCELLAR.COM/ONLINE

Let us help keep your project on track or simplify your design decision. Put your tough technical questions to the ASK US team.

The ASK US research staff of engineers has been assembled to share expertise with others. The forum is a place where engineers can congregate to get some tough questions answered, or just browse through the archived Q&A's to broaden their own intelligence base.

|          | 12 Getting Your Signals Straight<br>Walsh-Hadamard Encoders and Decoders in MATLAB<br><i>Kizito Tshilumba Kasengulu</i> |            |                                                                                                 |                                                              |    |  |

|----------|-------------------------------------------------------------------------------------------------------------------------|------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----|--|

|          | 20 Building a RISC System in an FPGA<br>Part 2: Pipeline and Control Unit Design<br>Jan Gray                            |            |                                                                                                 |                                                              |    |  |

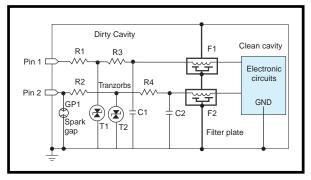

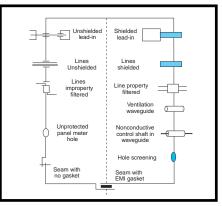

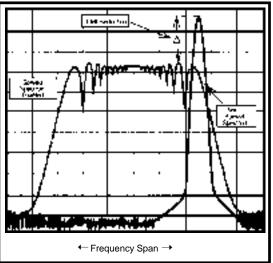

|          | 28 The Shocking Truth about EMC<br>Part 1: Design for Compatibility<br>George Novacek                                   |            |                                                                                                 |                                                              |    |  |

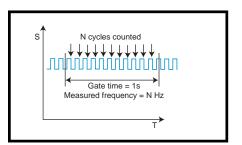

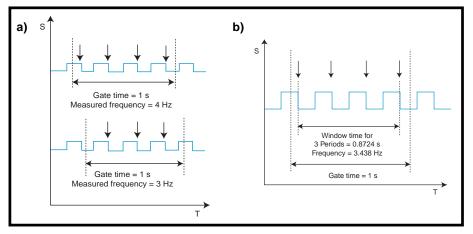

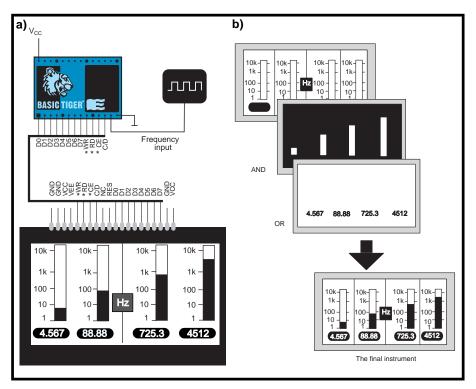

|          | 52 A Quick Meter Made<br>Fast Frequency Meter for Low Frequencies<br>Markus Desgronte                                   |            |                                                                                                 |                                                              |    |  |

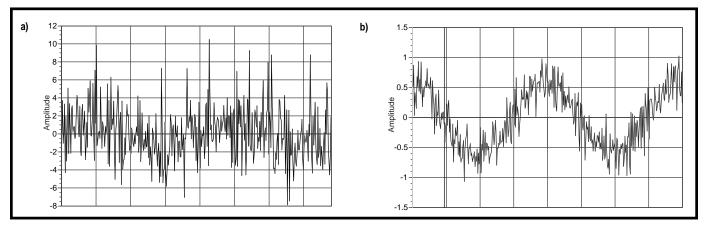

|          | 58                                                                                                                      |            | <b>About Correlation</b><br><i>n Tipton</i>                                                     |                                                              |    |  |

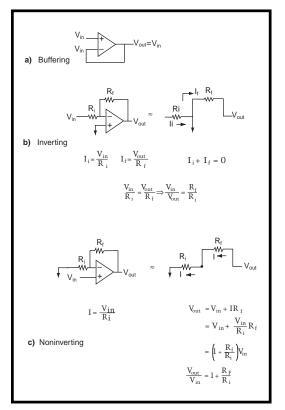

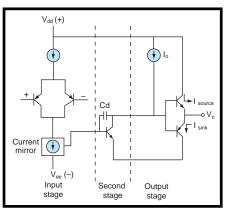

|          | 64                                                                                                                      | ٤          | <b>MicroSeries</b><br>Op-Amp Specifications<br>Part 1: Served Italian Style<br>Joe DiBartolomeo | <b>Task Manager</b><br>Rob Walker                            | 6  |  |

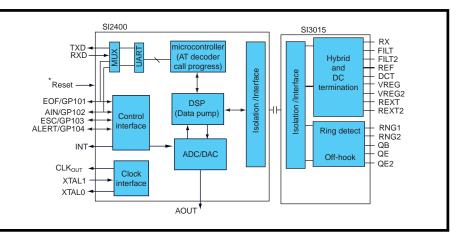

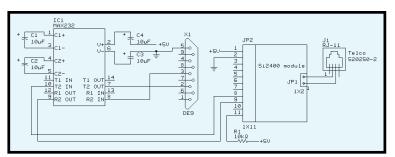

|          | 70                                                                                                                      |            | <b>From the Bench</b><br>Drop the Incredible Bulk                                               | Digital Becomes Analog                                       |    |  |

|          |                                                                                                                         |            | Using Capacitors as Isolation Components<br>Jeff Bachiochi                                      | New Product News<br>edited by Harv Weiner                    | 8  |  |

|          | 76                                                                                                                      | <b>±</b>   | <b>Silicon Update</b><br>A Winter Timer Tale<br><i>Tom Cantrell</i>                             | Test Your EQ                                                 | 83 |  |

|          | T                                                                                                                       |            |                                                                                                 | Advertiser's Index<br>May Preview                            | 95 |  |

|          |                                                                                                                         |            | SDA                                                                                             | Priority Interrupt<br>Steve Ciarcia<br>All Things Considered | 96 |  |

| <b>F</b> | EMBEDDED PC                                                                                                             |            |                                                                                                 |                                                              |    |  |

|          | )<br>Nouvea                                                                                                             | au PC      |                                                                                                 |                                                              |    |  |

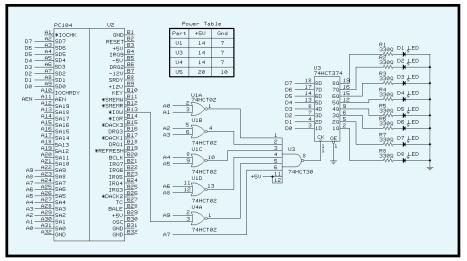

|          | 2 RPC                                                                                                                   | POS<br>Bui | I <b>l-Time PCs</b><br>ST It<br>Id a Power-On Self Test Card for PC/104<br>o Cyliax             | <u>'</u> /                                                   |    |  |

| 40       | 5 арс                                                                                                                   | Uno<br>Par | plied PCs<br>der the Covers<br>t 1: Get Embed(ded) with Windows NT 4.0<br>d Eady                |                                                              |    |  |

# TASK MANAGER

### **Digital Becomes Analog**

here's no question, we are living in an increasingly digital era. In January, Mark Balch finished up his three-part series on high-definition digital television and brought us up to speed on the analog-todigital conversion process. Jeff recently finished a series on digital filters in his From The Bench column, then there was Stuart Ball's digital sound board project, and the list goes on.

All of this emphasis on going digital has brought to attention some interesting issues. Namely, that digital engineers are being asked to fill in more and more analog gaps. As Joe DiBartolomeo found out when preparing this month's article on op-amp specifications, when digital designers find themselves faced with analog design issues, they focus on function, not form.

That mentality certainly doesn't make them inferior designers. It's just like taking a standardized test, you don't spend a lot of time on the questions you don't know or understand, you just circle the answer that looks like it might be right and go on. You take your time and make sure you ace the questions in your area of expertise.

Tom's on top of this issue, as you saw in his March Silicon Update Online article on the latest analog PLDs from Lattice Semiconductor. Like he said, the analog gap may be closing, but it certainly won't disappear because humans are analog.

Speaking of humans being analog, I had a chance to make a bit of a digital-to-analog conversion while at the ESC-Spring in Chicago last month. That is, instead of dashing off digital e-mail replies to readers and authors, I got to do some analog handshaking and spend some time talking to previous authors, future authors, and plenty of subscribers.

One of the things that came up while I was talking to different people at the show, was the issue of digital designers having to find their way through analog design. I heard some pretty interesting workarounds that digital designers had come up with. I also heard analog specialists discussing some of the bubble-gum-and-baling-wire solutions they had run across that were "obviously contrived by digital-oriented designers." Both sides have their politics and religion, that's for sure.

But, politics and religion is matter for the trade magazines, Circuit Cellar is about quality editorial and practical application articles. At least that's the impression I got from talking to readers while I was in Chicago. I talked to hardware designers who like the schematics, software designers who enjoy the code snippets and software downloads, and instructors who use Circuit Cellar in the classroom.

Sure, not everyone who came by the booth was familiar with Circuit Cellar, and not everyone who was familiar with us was 100% satisfied with everything we've done. But, I enjoyed talking to those people too, because it gave me an idea of the things we need to work on and improve. Try voicing your opinion to one of the trade magazines and you'll find out that the only input they want from you is green, with plenty of zeros.

I haven't seen any trade magazine demographics, but I've seen the stats on Circuit Cellar readers and I'd say that 100% of our readers are human. Until that changes, I guess we'll just keep shaking hands and taking your comments. After all, humans are analog.

EDITORIAL DIRECTOR/PUBLISHER Steve Ciarcia

MANAGING EDITOR Rob Walker

**TECHNICAL EDITORS** Jennifer Belmonte Rachel Hill Jennifer Huber

WEST COAST EDITOR Tom Cantrell

CONTRIBUTING EDITORS Mike Baptiste Ingo Cyliax Fred Eady George Martin Bob Perrin

NEW PRODUCTS EDITOR Harv Weiner

**PROJECT EDITORS** Steve Bedford Janice Hughes Elizabeth Laurençot James Soussounis David Tweed

ASSOCIATE PUBLISHER Sue Skolnick

**CIRCULATION MANAGER** Rose Mansella

CHIEF FINANCIAL OFFICER Jeannette Ciarcia

> CUSTOMER SERVICE Elaine Johnston

> > ART DIRECTOR KC Zienka

**GRAPHIC DESIGNER** Mary Turek

STAFF ENGINEERS Jeff Bachiochi John Gorsky

QUIZ MASTERS Tak Auyeung Benjamin Day Bob Perrin

EDITORIAL ADVISORY BOARD Ingo Cyliax Norman Jackson

David Prutchi

Cover photograph Ron Meadows-Meadows Marketing PRINTED IN THE UNITED STATES

### ADVERTISING

ADVERTISING SALES MANAGER Bobbi Yush (860) 872-3064 ADVERTISING COORDINATOR

Fax: (860) 871-0411 E-mail: bobbi.yush@circuitcellar.com

E-mail: val.luster@circuitcellar.com

Valerie Luster (860) 875-2199

ADVERTISING CLERK

Sally Collins

CONTACTING CIRCUIT CELLAR

Fax: (860) 871-0411

SUBSCRIPTIONS: INFORMATION: www.circuitcellar.com or subscribe@circuitcellar.com

TO SUBSCRIBE: (800) 269-6301 or via our editorial offices: (860) 875-2199 GENERAL INFORMATION

TELEPHONE: (860) 875-2199 FAX: (860) 871-0411

INTERNET: info@circuitcellar.com, editor@circuitcellar.com, or www.circuitcellar.com EDITORIAL OFFICES: Editor, Circuit Cellar, 4 Park St., Vernon, CT 06066

AUTHOR CONTACT: E-MAIL: Author addresses (when available) included at the end of each article.

For information on authorized reprints of articles

contact Jeannette Ciarcia (860) 875-2199 or e-mail jciarcia@circuitcellar.com.

CIRCUIT CELLAR®, THE MAGAZINE FOR COMPUTER APPLICATIONS (ISSN 1528-0608) and Circuit Cellar Online are published monthly by Circuit Cellar Incorporated, 4 Park Street, Suite 20, Vernon, CT 06066 (860) 875-2751. Periodical rates paid at Vernon CT and additional offices. One-year (12 issues) subscription rate USA and possessions \$21.95, Canada/Mexico \$31.95, all other countries \$49.95. Two-year (24 issues) subscription rate USA and possessions \$39, Canada/Mexico \$55, all other countries \$85. All subscription orders payable in U.S. funds only via VISA, MasterCard, international postal money order, or check drawn on U.S. bank.

Direct subscription orders and subscription-related questions to Circuit Cellar Subscriptions, P.O. Box 698, Holmes, PA 19043-9613 or call (800) 269-6301.

Postmaster: Send address changes to Circuit Cellar, Circulation Dept., P.O. Box 698, Holmes, PA 19043-9613

Circuit Celtar@ makes no warranties and assumes no responsibility or liability of any kind for errors in these programs or schematics or for the consequences of any such errors. Furthermore, because of possible variation in the quality and condition of materials and workmanship of re assembled projects, Circuit Cellar® disclaims any responsibility for the safe and proper function of reader-assembled projects based upon or from plans, descriptions, or information published by Circuit Cellar®.

The information provided by Circuit Cellar® is for educational purposes. Circuit Cellar® makes no claims or warrants that readers have a right to build things based upon these ideas under patent or other relevant intellectual property law in their jurisdiction, or that readers have a right to construct or operate any of the devices described herein under the relevant patent or other intellectual property law of the reader's jurisdiction. The reader assumes any risk of infringement liability for constructing or operating such devices.

Entire contents copyright @ 2000 by Circuit Cellar Incorporated. All rights reserved. Circuit Cellar and Circuit Cellar INK are registered trademarks of Circuit Cellar Inc. Reproduction of this publication in whole or in part without written consent from Circuit Cellar Inc. is prohibited.

### Edited by Harv Weiner

### PIXEL-COUNTING SENSOR

The **PresencePLUS Pixel-Counting Sensor** is a camera-based sensor that consists of a 512 x 384 CMOS pixel array with a programmable microprocessor, controller, lens, lighting, mounting bracket, and cable. The sensor captures a 256-level grayscale image of a specified area, converts the image to black and white pixels, and compares the designated-color pixel count with user-programmed upper and lower threshold values to render a pass or fail judgment of the target.

The PRC1 hand-held controller, used to program and monitor the PresencePLUS, displays programming options, monitoring options, and captured images on its LCD screen. Threshold values can be programmed, either manually or automatically, using one of the sensor's two TEACH modes. User programming designates which pixel color to count, white or black; the auto-exposure time, indexed or motion; and the light source behavior; off or strobed.

QUICK START is a one-step SETUP, TEACH, and RUN option for applications that do not require defining a specific region of interest, masking, or teaching bad product. In QUICK START, the pass and fail values are automatically set to 15% above maximum count and 15% below minimum count.

The sensor's three SPST solid-state output contacts may be individually programmed for either NPN (sinking) or PNP (sourcing). Integral circuitry protects the sensor against overload, short circuit, reverse polarity, and transient voltages. The device features an anodized aluminum housing with a painted finish and has an environmental rating of IP20, NEMA 1.

The PresencePLUS sells for under \$1700. Individual sensors list at \$995.

### Banner Engineering Corp. (612) 544-3164 • Fax: (612) 544-3213 www.baneng.com

### LCD DISPLAY

Apollo Display Technologies Inc. has introduced a high-contrast line of  $240 \times 128$  pixel monochrome, passive LCD's with onboard controllers and optional touchscreens. The line includes black and white FSTN transmissive and blue and white STN transmissive models, both with cold cathode backlighting. Also available is a transflective, sunlight readable version with LED backlighting.

These compact displays offer designers a simple and low-cost way to display icons, logos, bar charts, multiple fonts, and bit-map graphics with optional user input via an analog resistive touchscreen. Applications include bench top, rack or panel mounted instruments, POS terminals, and other applications requiring high information content in limited space.

The display includes  $240 \times 128$  pixels with  $0.50 \times 0.50$ -mm (0.020" × .020") pitch in a  $126.0 \times 70.0$ -mm (4.96" × 2.76") viewing area and outline dimensions of 170.0 x 105.0 x 14.0 mm (6.7" × 4.1" × 0.55"). Each model features a 5.0-V, 8-bit ASCII display interface with onboard, industry standard controller T6963C and 64-KB SRAM.

The touch screen is designed for finger, stylus, and signature capture touch requirements. It features an 8wire interface for accuracy, mounts directly to the display bezel, and offers 79% transmissivity with integral anti-glare film and hardcoat.

The displays price from \$99 and \$79 with and without touchscreen, respectively.

Apollo DisplayTechnologies, Inc. (631) 654-1143 Fax: (631) 654-1496 www.apollodisplays.com

### MULTI-AXIS MOTION PROCESSOR

The Navigator **MC2800** Series of Multiple Motor Type Motion Processors allows the control of both brushed and brushless servomotors in one chipset. The chipset supports sinusoidal commutation of 2- or 3-phase brushless motors, as well as positioning and velocity control of brushed servomotors. Users can select any axis to be brushed or brushless (for 2 and 4 axes). Applications include industrial automation and robotics, medical automation, materials handling, semiconductor manufacturing, test and laboratory equipment, and textiles.

The chipset consists of a 132-pin processor and a 100-pin logic and gives users the ability to off-load resource intensive motion control functions from the application's host processor. Its instruction set supports more than 130 commands to offer flexibility and versatility during application programming. User selectable profiling modes supported by the motion processor include Scurve, trapezoidal, velocity contouring, and electronic gearing. The MC2800 Series accepts input param-

eters such as position, velocity, and acceleration from the host, and generates a corresponding trajectory.

The MC2800 Series has a pre-programmed PID filter with feedforward velocity and acceleration, and a 32-bit position error. The motion processor outputs commutation signals based on either Hall sensors or the motor's encoder. Two or three separate motor signals per axis are sent by the motion processor, either in a 16-bit Digital-to-Analog Converter (DAC) or 10-bit, 20-kHz Pulse Width Modulation (PWM) compatible format. By di-

rectly outputting commutation signals from the chip, the MC2800 reduces torque ripple, oscillation, overshoot, and audible noise level.

The chipset is available in two (MC2820) and four axis (MC2840) configurations with prices starting at \$69 in OEM quantities.

Performance Motion Devices, Inc. (781) 674-9860 Fax: (781) 674-9861 www.pmdcorp.com

### SIGNAL PROCESSING SYSTEM

The **Model 6229** is the industry's first digital upconverter and D/A VIM-2 (Velocity Interface Mezzanine) module. It is ideal for radio transmission and can be attached to any VIM-compatibleTMS320C6x digital signal processor (DSP) board and digital receiver to build a complete, low-cost transmit and receive software radio system. Applications include radar test signal generation, electronic countermeasures, transmit functions for advanced software radio and satellite communications systems, and synthesized signal generation for test and measurement.

The digital upconverter and D/A module contain two complete upconverter channels. Both channels use the AD9856 Quadrature Digital Upconverter, which includes half-band and CIC interpolation filters, a programmable local oscillator, a complex mixer, and a 12-bit D/A converter.

The VIM modules are daughter cards designed to maximize I/O transfer rates to match the performance and speed of the Pentek 'C6x DSP boards. VIM modules are offered in several different sizes and formats with an extensive array of functionality.

Pentek's ReadyFlow Board Support Libraries of C-callable device functions are supplied with all VIM modules. Third-party and Pentek software development tools are available for a variety of platforms including PC's running Windows 95/98/NT, Digital Alphas running D-UNIX, HP workstations running HP-UX, and Sun SpARCstations running SunOS or Solaris.

Pricing for the Model 6229 starts at \$3,995.

Pentek, Inc. (201) 818-5900 Fax: (201) 818-5904 www.pentek.com

### MOTOR CONTROL MODULE

The CMI-5015-12 Motor Control Module is specifically designed for operating both fractional and integral horsepower three-phase motors. The module delivers currents of 30 A, with peaks up to 40 A off a single 4- to 12-V power supply. It is packaged in a miniature, hermetically sealed module, making it ideally suited for high performance battery operated three-phase Brushless Motor Control applications, such as robotics, electromechanical valve assemblies, batteryoperated motors, positioning systems, fans, and blower motors. The module is ideally suited for harsh environments where shock, vibration, and extreme temperature are present, and operates over the full military temperature range of -55°C to 125°C.

The CMI-50I5-12, plug and play module contains the latest ASIC technology for commutation, cross conduction protection, braking, under voltage lock out protection, temperature compensated reference, and cycle-by-cycle current limiting. Its high-efficient power stage is made up of high and low side drivers for driving the gates of low resistance N Channel power MOSFETS.

Coupled with a unique low loss current sensing circuit and internal bus capacitors, the need for large external components is eliminated. The CMI-5015-12 is designed with 60° electrical sensor phasing, but a 120° factory option is available. An internal DC/DC converter provides logic voltages allowing the module to operate off a single supply as low as 4 V while supplying maximum current to the output stage.

The CMI-50I5-12 sells for \$375 per 1,000.

Composite Modules (508) 226-6969 Fax: (508) 226-0938 www.cmodules.com

### **8051 DEVELOPMENT SUITE**

The **8051 Development Suite** includes a full-featured ANSI C compiler, a relocatable cross-assembler, an ad-

vanced overlay linker, a state of the art source level simulator, and a debug monitor. All of these integrate into Crossware's Embedded Development Studio environment to create a single vendor tool set, which can be used to develop and fully debug 8051 programs both with and without target hardware.

The C compiler features smart pointers that free the programmer from the task of telling the compiler where variables are located. It supports memory banking with up to 256 banks of code and 256 banks of RAM. It also features customizable common code merging, allowing the programmer to adjust the size of the program to fit the memory available. In addition, the Embedded Development Studio is able to drive the parallel compilation of all of the source files in a program, allowing the compiler to carry out cross-module optimizations.

The linker also is cross-module aware. As well as performing an overlay analysis to minimize memory usage, it will check the integrity of the entire program ensuring that variables, functions, and other objects are used consistently across modules. The simulator, also known as the 8051 Virtual Workshop, allows full source level debugging without any hardware. It can be rapidly extended to simulate additional devices allowing the simulation of complete target systems.

The debug monitor turns the Virtual Workshop into a full source level remote debugger. The Virtual Workshop communicates with it via a PC serial port and controls execution of the user's program breakpoints, single stepping, an so on. The debug monitor consumes less than 2 KB of program space and easily fits beneath the 0800h address partition of the Dallas DS5000. It consumes no internal ram resources, swapping itself to external ram while the users program is active. Full C source code, using the Virtual Workshop, is supplied together with tools and instructions that allow it to be modified and debugged without hardware.

Crossware + 44 (0)1763 853500 Fax: + 44 (0)1763 853330 www.crossware.com

# Getting Your Signals Straight

Kizito Tshilumba Kasengulu

# Walsh-Hadamard Encoders and Decoders in MATLAB

Not up to speed on Walsh-Hadamard encoders and decoders? No problem, Kizito was kind enough to give us some Hadamard code background before explaining how to implement these helpful encoders and decoders in MATLAB. amed after the French mathematician Jacques Hadamard, Hadamard codes belong to the category of block codes, where the encoder takes the original stream of bits, divides it in short sequences of a certain length, and outputs code words with a content and a length defined by the properties of the code.[1] They have interesting properties, which is why they are used in DSP for communications, image processing, and so forth.

Despite the fact that they can be linear (i.e., each component of the code word is a linear combination of the ones in the message) or non-linear, in most applications only linear codes are used. They are easy to generate and provide simple properties that can be expressed through the algebra of matrix and Hadamard Transforms.

### **DEFINING A HADAMARD MATRIX**

A mathematical definition is provided in this section (a demonstration of the theorem can be found in [2]). First, the definition: a Hadamard matrix of order n is a  $n \times n$  matrix of 1s and -1s, such that any pair of distinct rows or columns is orthogonal (i.e., the inner product is zero). And now, the theorem: if a Hadamard matrix of order n exists, then n is 1, 2, 4, or a multiple of 4.

The matrix  $H_8$  is a Hadamard matrix of order 8 (the character "–" for "–1"). You can verify that any pair of rows or columns is orthogonal.

$$H_8 = \begin{pmatrix} +1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 \\ +1 - + 1 - + 1 - + 1 - 1 \\ +1 + 1 - - + 1 + 1 - - + 1 \\ +1 - - + 1 + 1 - - - + 1 \\ +1 + 1 + 1 + 1 - - - - \\ +1 - + 1 - - + 1 - + 1 \\ +1 - - - + 1 - + 1 + 1 \\ +1 - - - + 1 - + 1 + 1 - \\ \end{pmatrix}$$

[1]

Two questions must now be answered. Does the arrangement of rows or columns (because it changes nothing, we will work only with rows for simplicity) make a difference in applications? And, how do we construct a matrix of a certain order (n) in agreement with the above theorem?

The answer to the first question is, yes. The order of rows leads to different matrices having different behaviors in applications. Many arrangements are possible [3], in this article I chose a widely used arrangement called natural order ( $H_8$  is naturally ordered).  $H_n$  is in natural order if its rows are not ordered with respect to the number of sign changes in each row.

Therefore, the response to the second question will concern naturally ordered matrix. The most used algorithms that allow the construction of a naturally ordered Hadamard matrix are named after Sylvester and Paley. At this stage, it's important to say that the Sylvester construction technique for a matrix of order  $n = 2^m$  (*m* being a positive integer) always leads to a linear code, while the Paley technique for n > 8 always leads to a nonlinear code.[2]

Because linear codes are used in this article, the Sylvester technique of order  $n = 2^m$  is chosen. Using this

| Message | Code word         |  |

|---------|-------------------|--|

| (1,1,0) | (0,0,1,1,1,1,0,0) |  |

| (0,0,1) | (0,1,0,1,0,1,0,1) |  |

| (1,0,1) | (0,1,0,1,1,0,1,0) |  |

| (0,1,0) | (0,0,1,1,0,0,1,1) |  |

**Table 1**—The encoder maps the message into a code word according to the Reed-Muller Algorithm.

Sylvester construction technique, the naturally ordered Hadamard matrix of order  $n = 2^m$  is obtained through:

$$H_{1} = \begin{bmatrix} 1 \end{bmatrix}$$

$$H_{2} = \begin{bmatrix} 1 & 1 \\ 1 & -1 \end{bmatrix}$$

$$H_{2n} = \begin{bmatrix} H_{n} & H_{n} \\ H_{n} & -H_{n} \end{bmatrix}$$

[2]

This article will deal with the naturally ordered Hadamard matrix of order  $n = 2^m$ , this leading to linear binary block codes of length  $n = 2^m$ and to their decoding with Fast Hadamard Transforms. All of this is of course in agreement with the above theorem. In closing this section, note that MATLAB software provides the function hadamard(n) that allows the creation of a naturally ordered Hadamard matrix of order *n*.

### WALSH FUNCTIONS

In the mathematical literature, two continuous functions S1(t) and S2(t) are said to be orthogonal over  $t_2$ - $t_1$  if:

$$\int_{t1}^{t2} S1(t)S2(t) = 0$$

[3]

If we have discrete functions or sequences, the integral can be replaced by a summation, and the orthogonality expresses that the inner product (scalar product) is zero. Among orthogonal continuous func-

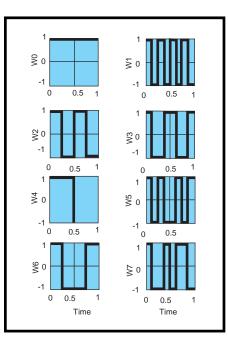

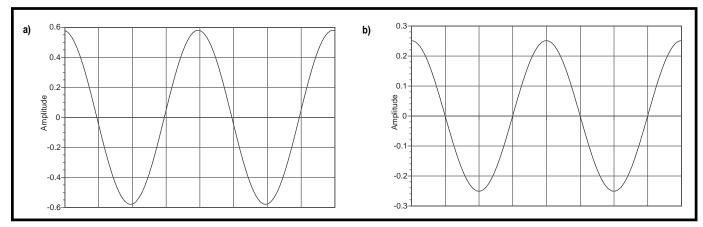

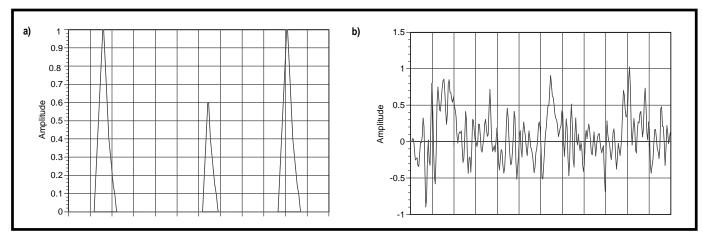

**Figure 1**—Here are the eight Walsh functions over 0 to 1, arranged in natural order from  $W_0$  to  $W_2$ .

tions, we can mention the wellknown *sin()* and *cos()*, Haar functions, Walsh functions, and so on.

Walsh functions were first published in 1924 by J.L. Walsh.[4] They are obtained by using square waveforms to produce the number of desired functions. Figure 1 shows eight Walsh functions over 0 to 1.

The Walsh functions in Figure 1 can be related to the rows of a Hadamard matrix of order 8 (see equation 1) because if you take eight samples (from 1/16 with interval 1/8) of each of the continuous Walsh func-

Listing 1—This is the code for the implementation of equations 6 and 7.

| function FWHT_Vector =<br>FWHT_8 ( Input_Vector _8 )<br>%                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>% function : FWHT_8 % Description : This function executes a Fast Walsh-Hadamard Transform with a natural order, this for vectors of length 8.</pre>                            |

| %<br>H_2=[ 1 -1 ;<br>1 -1 ;<br>]:                                                                                                                                                    |

| <pre>% The three stages in FWHT_8 F_8_1=kron(kron(eye(4),H_2),1); F_8_2=kron(kron(eye(2),H_2),eye(2)); F_8_3=kron(kron(eye(1),H_2),eye(4)); FHT_Vector_8=Input_Vector_8*F_8_1*</pre> |

| F_8_2*F_8_3 % performing the FWHT<br>end                                                                                                                                             |

tions, the resulting sequences are simply rows of the Hadamard matrix, now called Walsh-Hadamard matrix. In other words, a Walsh-Hadamard matrix is a Hadamard matrix where its rows describe samples of Walsh functions.

If the Hadamard matrix is in natural order, as are the Walsh functions, its first row is the sample of  $W_0$ , its second the sample of  $W_1$ , and so on. Note that the matrix of equation 1 is a naturally ordered Walsh-Hadamard matrix, and its rows are noted by index starting from 0 for the first row to 7 = 8 – 1 for the eighth row.

Naturally ordered Walsh-Hadamard matrices of order *n* have an index from 0 for the first row to n – 1 for the last. As it will be seen later, among the possible codes you can derive from them, you have linear binary block codes of length *n*. Remember that in this article  $n = 2^m (m$ positive integer), in accordance with the Sylvester construction technique and the earlier-mentioned theorem.

### FAST WALSH-HADAMARD TRANSFORMS

Just like a Fourier Transform is an expanded summation of the orthogonal functions sin() and cos(), a Walsh-Hadamard Transform also is a summation of the Walsh functions of a Hadamard matrix. f(n) being a sequence containing  $M = 2^m$  real numbers, its naturally ordered Walsh-Hadamard Transform *WHT* is defined as:

$$WHT(\mathbf{k}) = \sum_{n=0}^{\mathbf{M}-1} f(n)WH(\mathbf{k}, n)$$

<sup>[4]</sup>

where k = 0, 1, 2, ..., and M–1 and WH is the naturally ordered Walsh-Hadamard matrix of order M.

We also can write (equasion 4) in the general matrix form:

WHT =

$$(WHT_0, WHT_1, \dots WHT_{2^m - 1})$$

=  $f(\mathbf{n})WH_{2^m}$  [5]

From equation 4, observe that the Walsh-Hadamard Transform makes only sums and substractions (they will be taken as sums) of the elements of the inputted vector. For an input vector of length M you have M - 1 additions in M steps, that is, M(M-1) operations.

Fast Walsh-Hadamard Transforms allow a gain in time by having Madditions in  $\log_2 M$  steps (i.e.,  $M \log_2 M$ operations). Among the proposed algorithms, I chose the one of reference [5] because it leads to the result by using a simple method. This method uses a factorisation of the matrix WH so the application has fewer steps compared to the ordinary case. This factorization is:

$$WH_{2m} = F^{(1)}_{2m} F^{(2)}_{2m} \dots F^{(m)}_{2m}$$

[6]

where:

$$\mathbf{F}_{2}^{i}m = \mathbf{I}_{2}m - i \otimes \mathbf{W}\mathbf{H}_{2} \otimes \mathbf{I}_{2}^{i-i}$$

<sup>[7]</sup>

and  $i = 1, 2, 3, ..., I_n$  is a n × n identity matrix,  $WH_2$  is the matrix H<sub>2</sub> of equation 2 and multiplied by the Kronecker product. Therefore, for an input vector of length 2<sup>m</sup>, you have *m* steps instead of 2<sup>m</sup>. Listing 1 gives a short MATLAB function (*FWHT\_8(Input\_Vec-tor\_8)*) written to calculate the naturally ordered Fast Walsh-Hadamard Transform of length 8 by using the matrix factorisation method described here.

### IN THE WORLD OF BITS

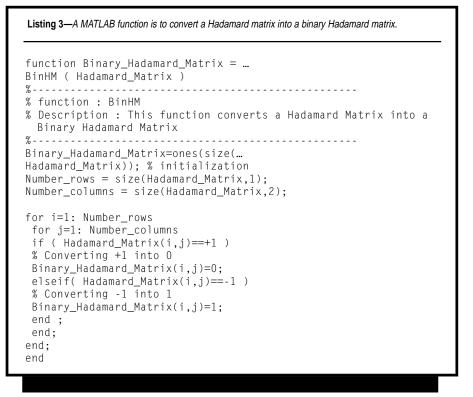

After defining the real matrix, in order to pass from the real world to the world of binary, you have the transformation:

$$+1 \longrightarrow 0$$

$-1 \longrightarrow 1$  [8]

Listings 2 and 3 contain the functions *Conv(Binary\_Sequence)* and *BinHM(Hadamard\_ Matrix)*, which allow you to convert a binary sequence into a real vector, and a real Hadamard matrix into a binary Hadamard matrix, respectively.

Despite the fact that there are many Walsh-Hadamard code definitions, in this article, the codes words are simply the rows of the binary Walsh-Hadamard matrix of order *n* and their complements.

So, in this article, a Walsh-Hadamard code has a length of n and comprises 2n code words. In addition, Listing 2—This is how a test Walsh-Hadamard Transform is calculated in the real world. This function is used to cross from the binary world to the real world.

```

function Vector = Conv( Binary_Sequence )

9

% function : Conv

% Description : This function converts a Binary Sequence into a

Vector containing +1s or -1s

Vector=[];

for i=1:length(Binary Sequence)

if ( Binary_Sequence(i)==0 )

%--- Converting 0 into +1

Vector=[ Vector 1 ];

elseif( Binary_Sequence(i)==1 )

%--- Converting 1 into -1

Vector=[ Vector -1 ];

end ;

end;

end

```

this code is said to be non-cyclic because every code word does not have a shifted version inside the code. In other words, saying that the linear codes studied in this article are noncyclic codes means that, for every code word, you can't find a right or left p-shifted version that also will be a code word.

There are two other code definitions for Walsh-Hadamard codes.[2] The first code is comprised of the rows of the binary Walsh-Hadamard matrix of order *n* left-most column (then this code has a length of n - 1and comprises *n* code words). The second code is comprised of this first code along with the complements of the rows (then, here the code has a length of n - 1, but with 2n code words). The code definition here is commonly used and is sufficient for a good understanding of the subject.

Also, keep in mind that the Hamming distance (d) between two sequences of equal length is the number of coordinates in which they differ. The minimum distance  $(d_{min})$  of a block code is the minimum Hamming distance between all distinct pairs of code words.

A code with  $d_{min}$  can detect all error patterns of weight (the number of nonzero coordinates in a sequence) less than or equal to,  $d_{min} - 1$ . It can correct all error patterns of weight less than or equal to:

$$floor\_function\left(\frac{d_{min}-1}{2}\right) \qquad \qquad [9]$$

This correction capability must be taken as minimal because it can be proven that some block codes have a higher capability. You can verify that this Walsh-Hadamard code of length  $n = 2^m (2n \text{ codes words of length } n)$ has a minimum distance of:

### $\frac{n}{2}$

Assuming code words have the same probability to be transmitted, a maximum likelihood hard decision decoder (MLHDD) outputs the code word closest in Hamming distance to the received sequence.

Because the Hamming distance between a code word and its complement always has a value of n, encoders and decoders will work only with the n code words that are defined by the rows of the binary Walsh-Hadamard matrix. The MLHDD will output a code word having a minimal Hamming distance of  $d_x$  to the received sequence and  $n + d_x$  between the complement of the code word and the received sequence.

### WALSH-HADAMARD ENCODERS

The goal of the encoder is to map a message sequence into a code word of  $n = 2^m$  bits. The reader must remember that this code word is a row or a

complement of a row in the binary Walsh-Hadamard matrix of order  $n = 2^m$ . As is often the case, the encoder I used here will select only among the rows of the matrix. A message of length *m* will be encoded into a code word of length  $n = 2^m$ .

Among the algorithm used for a message of length m to select a Walsh-Hadamard code word of length  $n = 2^m$ , the Reed-Muller encoding algorithm is commonly used to give an efficient and easy-to-implement technique.

Because the goal here is not to study Reed-Muller codes, only the main steps are given (note that Reed-Muller codes are linear block codes). [6] The generator matrix for the first order Reed-Muller code R(1,3) of length  $8 = 2^3$  is defined as:

$$\mathbf{G} = \begin{bmatrix} 1 & 1 & 1 & 1 & 1 & 1 & 1 & 1 \\ 0 & 0 & 0 & 0 & 1 & 1 & 1 & 1 \\ 0 & 0 & 1 & 1 & 0 & 0 & 1 & 1 \\ 0 & 1 & 0 & 1 & 0 & 1 & 0 & 1 \end{bmatrix} = \begin{bmatrix} \mathbf{U} \\ \mathbf{V3} \\ \mathbf{V2} \\ \mathbf{V1} \end{bmatrix}$$

[10]

- -

г

The above Reed-Muller matrix is comprised of a vector U of 1s in its first row and the remaining rows are constructed so that they describe a digital counter from left to right. This method can be generalized to obtain a greater matrix generator for first order Reed-Muller codes R(1,m). Considering a message  $(m_0, m_1, m_2, ..., m_{m-1})$  has to pass through an encoder, Reed-Muller codes and Walsh-Hadamard codes are related so the chosen code word *c* is:

$$c = m_{m-1}V_1 + m_{m-2}V_2 + \dots m_1V_{m-1} + m_0V_m$$

[11]

Therefore, the result obtained by the above linear combination of the  $V_i$ vectors is a row in the binary Walsh-Hadamard matrix of order  $n = 2^m$ .

Another way to avoid the direct use of Reed-Muller generator matrix is to observe that the index (remember that indexes start from zero) of the chosen row has a binary or radix-2 form  $m_0m_1m_2...m_{m-1}$ . Consequently, for a message  $(m_0, m_1, m_2,...m_{m-1})$ , the index of the row to choose is the decimal form of  $m_0m_1m_2...m_{m-1}$ . It is important to note that this affirmation is true in the case of a naturally ordered matrix.

Listing 4 is a MATLAB program that implements a Walsh-Hadamard Encoder of length 8. This encoder use a first order Reed-Muller encoding algorithm. In the section Simulation Results, you can see that for a message (0,0,1), the selected code word is (0,1,0,1,0,1,0,1). You can verify that the index of this row is the decimal form of 001 (i.e., 1). In the same way, the code word for the message (1,1,0) is the row having the index value 6 (6 is the decimal form of 110).

### MAXIMUM LIKELIHOOD DECODERS

This article deals with hard decision decoding (i.e., the decoding that gives the closet code word in Hamming distance). By observing equation 4, we find that for each k, the right side of the equation is simply the correlation between the vectors f(n)and WH(k,:), meaning that the Hadamard Transform performs a correlation between the received sequence (f(n)) and all possible code words inside the matrix.

Under the assumption of equal probability of transmission, a Maximum Likelihood Decoder is related to a correlation decoder, because the code word that minimizes the Hamming distance maximizes the correlation (assuming that this correlation is positive).

So, the maximum likelihood code word is the row in *WH* that corresponds to the greatest value in the Fast Walsh-Hadamard Transform vector. If this value is negative, this row is simply the furthest code word, then its complement (addition with a sequence of 1s) is the maximum likelihood code word. In relation to what I said earlier, you now see that it's sufficient to compute correlations with only mcode words (the m code words inside WH). In brief, the encoder selects one of the m rows of WH, while the decoder outputs one of the 2m code words by using only the m rows of WH in its calculus.

### LIKELIHOOD DECODER IN MATLAB

Listing 5 is a MATLAB implementation for the case of a code of length 8 (16 =  $8 \times 2$  code words). The function FWHT 8(Input Vector 8) computes the Fast Walsh-Hadamard Transform with natural order, as described earlier, and puts the result in the vector FWHT\_Vector. The MATLAB function *hadamard(n)* has been used for the creation of the naturally ordered Walsh-Hadamard matrix of order 8 (see the comments for more details). In the Simulation Results section, you can see that, for a corrupted received sequence (1,0,0,0,0,0,1,1), the maximum likelihood code word is (1,1,0,0,0,0,1,1).

### SIMULATION RESULTS

This section gives some simulation results of the running of our MATLAB code and allows you to verify all of the theories I have covered. For clar-

Listing 4—The input message is taken from the user prompt and the code word is calculated by using the Reed-Muller Algorithm.

```

% - -

% Program : WH_Encoder_Length_8

% Description : This program implements a Walsh-Hadamard Encoder

based on the first order Reed-Muller R(1,3)Encoding Algorithm.

% Author : Kizito Tshilumba Kasengulu

%_____

clear

m=input('Input the binary message (length 3) : ');

%--- The Reed-Muller Generator Matrix

Reed_Muller=[

1 1 1 1 1 1 1 1;

0 0 0 0 1 1 1 1 ;

00110011;

0 1 0 1 0 1 0 1;

]:

%---The encoder outputs a code word c of length 8.

%---xor(x,y) is the Exclusive OR Operator acting as the binary

addition of x and y

c=xor(xor(m(3)*Reed_Muller(4,:),...

m(2)*Reed_Muller(3,:)),...

m(1)*Reed_Muller(2,:))

```

| Received              | Maximum likelihood |  |

|-----------------------|--------------------|--|

| sequence              | code word          |  |

| (0,1,0,1,0,1,0,0)     | (0,1,0,1,0,1,0,1)  |  |

| (1,0,0,0,0,0,1,1)     | (1,1,0,0,0,0,1,1)  |  |

| $(0,0,1,1,1,1,1,1)^*$ | (1,1,1,1,1,1,1,1)* |  |

| $(1,1,0,0,0,0,0,0)^*$ | (0,0,0,0,0,0,0,0)* |  |

Table 2—As a result of noise, the received sequence is a corrupted version of the transmitted one. The decoder outputs the code word that is the most likely to have been transmitted.

ity, I chose to present simulations for the encoder and the decoder separately. Table 1 shows some simulations for the encoder and Table 2 shows the results of decoder simulations.

So, the decoding of a sequence and its complement agree with the theory

because the outputs are complementary (illustrated by the asterisks in Table 2).

### END SIGNAL

This article has proven that it is possible to derive non-cyclic linear block codes from Walsh-Hadamard matrix. The derivation lead to codes with length  $n = 2^m$  and 2n code words. Simulations with the MATLAB programs allow you to observe the working of encoders and decoders. It's also possible to verify the characteristics of the code mentioned in the text. In spite of the fact that the MATLAB programming was limited to n = 8 and m = 3, they can be generalized for any values of n and m with  $n = 2^m$ .

Listing 5—This decoder takes the received sequence (from the point of view of the decoder) from a user prompt. It outputs the code word that is the closest in Hamming distance. % Program : WH\_Decoder\_Length\_8 % Description : This program implements a Walsh-Hadamard Maximum Likelihood Decoder based on a naturally ordered Fast Walsh-Hadamard Transform. This decoder is designed for codes of length 8 and use Hard Decision. % Author : Kizito Tshilumba Kasengulu %\_\_\_\_\_ clear Received\_Sequence=input('Input the ... received sequence (length 8) : ') %---Converting the Received\_Sequence ( 1s or Os ) into a Vector (+1s or -1s) in using our function Conv (see listing 4) Received\_Vector=Conv(Received\_Sequence) ; %---Performing the naturally ordered Fast Walsh-Hadamard Transform of the Received\_Vector of length 8 by using our function FWHT\_8 ( see listing 3 ) FWHT\_Vector = FWHT\_8( Received\_Vector ); %--- Calculating the greatest magnitude in FWHT\_Vector and retaining its coordinate [Greatest,Coordinate]=max(... abs(FWHT\_Vector )); %--- Creating a Hadamard matrix of order 8 by calling the Matlab function hadamard(8) and converting it into a Binary Hadamard Matrix by using our function BinHM Binary\_Hadamard\_Matrix\_8=BinHM(... hadamard(8)); %--- Calculating the Maximum Likelihood Code Word if ( FHT\_Vector(Coordinate) ) > 0 Maximum\_Likelihood\_Code\_Word=... Binary\_Hadamard\_Matrix\_8(Coordinate,:) else %--- Sum of the two vectors by using xor(x,y) Maximum\_Likelihood\_Code\_Word=xor(... ones(1,8), Binary\_Hadamard\_Matrix\_8(... Coordinate,:)) end ;

Kizito Tshilumba Kasengulu is a TDMA software engineer at NSI Communications in Montreal, Canada. You may reach him at kkasengulu@nsicomm.com.

### REFERENCES

- J. Hadamard, *Résolution d'une Question Relative aux Determinants*, Bulletin on Science and Mathematics, vol. 17, pp. 240- 248, 1893.

- [2] F.J. MacWilliams and N.J.A. Sloane, *The Theory of Error Correcting Codes*, Amsterdam, North-Holland, 1977.

- [3] Y.A. Geadeh and M.J.G.

Corinthios, Natural, Dyadic, and Sequency Order Algorithms and Processors for the Walsh-Hadamard Transform, IEEE Transactions on Computers; vol.

C-26, pp. 435–442, May 1977.

- [4] J.L. Walsh, "A Closed Set of Orthogonal Functions", Am J. Math., vol. 55, pp. 5–24, January 1923.

- [5] M.H. Lee and M. Kaveh, Fast Hadamard Transform Based on a Simple Matrix Factorization,

IEEE Transactions on Acoustic, Speech, Signal Processing; vol.

ASSP-34, no. 6, pp. 1666–1667,

1986.

- [6] S.B. Wicker, Error Control Systems for Digital Communications and Storage, Prentice Hall, Englewood Cliffs, NJ, 1995.

### SOURCE

### MATLAB The MathWorks, Inc. (508) 647-7000 Fax: (508) 647-7001 www.mathworks.com

### HAVE YOU HEARD??? CIRCUIT CELLAR ONLINE IS COMING TO CD-ROM!

WATCH WWW.CIRCUITCELLAR.COM FOR DETAILS

# Building a RISC System in an FPGA

### FEATURE ARTICLE

Jan Gray

### Part 2: Pipeline and Control Unit Design

In Part 1, Jan introduced his plan to build a pipelined 16bit RISC processor and System-on-a-Chip in an FPGA. This month, he explores the CPU pipeline and designs the control unit. Listen up, because next month, he'll tie it all together. ast month, I discussed the instruction set and the datapath of an xr16 16-bit RISC processor. Now, I'll explain how the control unit pushes the datapath's buttons.

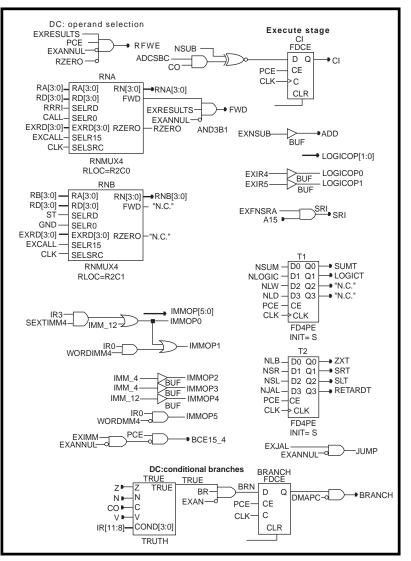

Figure 2 in Part 1 (*Circuit Cellar*, 116) showed the CTRL16 control unit schematic symbol in context. Inputs include the RDY signal from the memory controller, the next instruction word INSN<sub>15:0</sub> from memory, and the zero, negative, carry, and overflow outputs from the datapath.

The control unit outputs manage the datapath. These outputs include pipeline control clock enables, register and operand selectors, ALU controls, and result multiplexer output enables. Before designing the control circuitry, first consider how the pipeline behaves in both good and bad times.

### PIPELINED EXECUTION

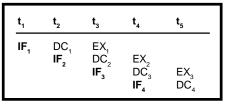

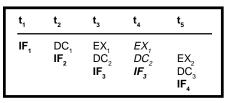

To increase instruction throughput, the xr16 has a three-stage pipeline—instruction fetch (IF), decode and operand fetch (DC), and execute (EX).

In the IF stage, it reads memory at the current PC address, captures the resulting instruction word in the instruction register IR, and increments PC for the next cycle. In the DC stage, the instruction is decoded, and its operands are read from the register file or extracted from an immediate field in the IR. In the EX stage, the function units act upon the operands. One result is driven through three-state buffers onto the result bus and is written back into the register file as the cycle ends.

Consider executing a series of instructions, assume no memory wait states. In every pipeline cycle, fetch a new instruction and write back its result two cycles later. You simultaneously prepare the next instruction address PC+2, fetch instruction  $I_{PC}$ , decode instruction  $I_{PC-2'}$  and execute instruction  $I_{PC-4}$ .

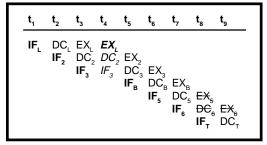

Table 1 shows a normal pipelined execution of four instructions. That's the simple case, but there are several pipeline complications to consider data hazards, memory wait states, load/store instructions, jumps and branches, interrupts, and direct memory access (DMA).

What happens when an instruction uses the result of the preceding instruction?

Ι,

Ι,

Referring to time  $t_3$  of Table 1, EX<sub>1</sub> computes r1=r1&7, while DC<sub>2</sub> fetches the old value of r1. In  $t_4$ , EX<sub>2</sub> incorrectly adds 1 to this stale r1.

This is a data hazard, and there are several ways to address it. The assembler can reorder instructions or insert nops to avoid the problem. Or, the control unit can detect the hazard and stall the pipeline one cycle, in order to write-back the result to the register file before fetching it as a source register. However, these techniques hurt performance.

**Table 1**—Here the processor fetches instruction  $I_1$  at time  $t_1$  and computes its result in  $t_2$ , while  $I_2$  starts in  $t_2$  and ends in  $t_2$ . Memory accesses are in boldface.

**Listing 1**—This C code produces assembly code that includes a load  $I_L$  and a branch  $I_g$ . Each causes pipeline headaches.

```

if ((p->flags & 7) == 1)

p - x = p - y;

lw r6,2(r1Ø)

I :

;load r6 with p->flags

I^{L}:

I^{2}:

andi r6,7

;is (p->flags & 7)

addi r0,r6,-1

:==1?

I<sup>3</sup>:

bne T

I<sup>B</sup>:

;yes: load r6 with p->y

lw r6,6(r10)

. . .

```

Instead, you do result forwarding, also known as register file bypass. The datapath DC stage includes FWD, a 16-bit 2-1 multiplexer (mux) of AREG (register file port A), and the result bus. Most of the time, FWD passes AREG to the A operand register, but when the control unit detects the hazard (DC source register equals EX destination register), it asserts its FWD output signal, and the A register receives the  $I_1$  result just in time for EX<sub>2</sub> in  $t_4$ .

Unlike most pipelined CPUs, the xr16 only forwards results to the A operand—a speed/area tradeoff. The assembler handles any rare port B data hazards by swapping A and B operands, if possible, or inserting nops if not.

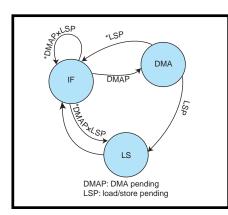

### MEMORY ACCESSES

The processor has a single memory port for reading instructions and loading and storing data. Most memory accesses are for fetching instructions. The processor is also the DMA engine, and a video refresh DMA cycle occurs once every eight clocks or so. Therefore, in any given clock cycle, the processor executes either an instruction fetch memory cycle, a DMA memory cycle, or a load/store memory cycle.

Memory transactions are pipelined. In each memory cycle, the processor drives the next memory cycle's address and control signals and awaits RDY, indicating the access has been completed. So, what happens when memory is not ready?

The simplest thing to do is to stop the pipeline for that cycle. CTRL deasserts all pipeline register clock enables PCE, ACE, and so forth. The pipeline registers do not clock, and this extends all pipeline stages by one cycle. In Table 2, memory is not ready during the fetch of instruction  $I_3$  in  $t_3$ , and so  $t_4$  repeats  $t_3$ . (Repeated pipe stages are italicized.)

$I_L$  in Listing 1 is a load word instruction. Loads and stores need a second memory access, causing pipeline havoc (see Table 3). In  $t_4$  you must run a load data access instead of an instruction fetch. You must stall the pipeline to squeeze in this access.

Then, although you fetched  $I_3$  in  $t_3$ , you must not latch it into the instruction register (IR) as  $t_3$  ends, because neither  $EX_L$  nor  $DC_2$  are finished at this point. In particular,  $DC_2$  must await the load result in order to forward it to A, because  $I_2$ uses r6—the result of  $I_1$ !

Finally, if (in  $t_3$ ) you don't save the just-fetched  $I_3$  somewhere, you'll lose it, because in  $t_4$ , the memory port is busy with the load cycle. If you lose it, you'll have to re-fetch it no sooner than  $t_5$ , with the result that even a nowait load requires three cycles, which is unacceptable.

To fix this problem, the control unit has a 16-bit NEXTIR register and an IR source multiplexer (IRMUX). In  $t_{3'}$  it captures  $I_3$  in NEXTIR, and then in  $t_4$ , IR is loaded from NEXTIR instead of from the memory port (which is busy with the load). NEXTIR ensures a two-cycle load or store, at a cost of eight CLBs.

As with instruction fetch accesses, load/store memory accesses may have to wait on slow memory. For example, had RDY not been asserted during  $t_{a'}$  the pipeline would have stalled another cycle to wait for  $\mathrm{EX}_{\mathrm{L}}$  access to complete.

### BRANCHING OUT

Next, consider the effect of jumps (call and jal) and taken branches. By the time you execute the jump or taken branch  $I_J$  during  $EX_J$  (updating PC), you'll have decoded  $I_{J+1}$  and fetched  $I_{J+2}$ . These instructions in the branch shadow (and their side effects) must be annulled.

Continuing the Table 3 example from time  $t_{5'}$  and assuming the branch is taken at  $t_{7'}$  you must annul the EX<sub>5</sub> stage of I<sub>5</sub>, and the DC<sub>6</sub> and EX<sub>6</sub> stages of I<sub>6</sub>. (Annulled stages are struck through). Execution continues at instruction I<sub>T</sub>. T<sub>9</sub> is not an EX<sub>5</sub> load cycle, because the I<sub>5</sub> load is annulled.

Because you always annul the two branch shadow instructions, jumps and taken branches take three cycles. Jumps also save the return address in the destination register. This return address is obtained from the datapath's RET register, which holds the address of the instruction in the DC pipeline stage.

### **INTERRUPTS**

When an interrupt request occurs, you must jump to the interrupt handler, preserve the interrupt return address, retire the current pipeline, execute the handler, and later return to the interrupted instruction.

When INTREQ is asserted, you simply override the fetched instruction with int, that is, jal r14,10(r0) via the IRMUX. This jumps to the interrupt handler at 0x0010 and leaves the return address in r14, which is reserved for this purpose. When the handler has completed, it executes iret, (i.e, jal r0,0(r14)) and exection resumes with the interrupted instruction.

**Table 2**—During  $t_{3^{*}}$  the instruction fetch memory access of  $I_{3}$  is not RDY, so the pipeline registers do not clock, and the pipeline stalls until RDY is asserted in  $t_{4^{*}}$ . Repeated pipeline stages are italicized.

**Table 3**—Pipelined execution of the load instruction  $I_{l}$ ,  $I_{2}$ ,  $I_{3}$ , the branch  $I_{gr}$  the annulled  $I_{5}$  and  $I_{gr}$  and the branch target  $I_{T}$ . During  $t_{4}$  you stall the pipeline for the  $I_{L}$  load/store memory cycle. The branch  $I_{g}$  executed in  $t_{7}$  causes  $I_{5}$  and  $I_{6}$  to be annulled in  $t_{8}$  and  $t_{r}$ . Annulled instructions are struck through.

There are two pipeline issues here. First, you must not interrupt an interlocked instruction sequence (any add, sub, shift, or imm followed by another instruction). If an interlocked instruction is in the DC stage, the interrupt is deferred one cycle.

Secondly, the int must not be inserted in a branch or jump shadow, lest it be annulled. If a branch or jump is in the DC stage, or if a taken branch or jump is in the EX stage, the interrupt is deferred. The simplicity of the process pays off once again. The time to take an interrupt and then return from a null interrupt handler is only six cycles.

You might be wondering about the interrupt priorities, non-maskable interrupts, nested interrupts, and interrupt vectors. These artifacts of the fixed-pinout era need not be hardwired into our FPGA CPU.

They are best done by collaboration with an on-chip interrupt controller and the interrupt handler software.

The last pipeline issue is DMA. The PC/address unit doubles as a DMA engine. Using a  $16 \times 16$  RAM as a PC register file, you can fetch either an instruction (AN  $\leftarrow$  PC<sub>0</sub> += 2) or a DMA word (AN  $\leftarrow$  PC<sub>1</sub> += 2) per memory cycle.

After an instruction is fetched, if DMAREQ has been asserted, you insert one DMA memory cycle. This PC register file costs eight CLBs for the RAM, but saves 16 CLBs (otherwise necessary for a separate 16bit DMA address counter and a 16-bit 2-1 address mux), and shaves a couple of nanoseconds from the system's critical path. It's a nice example of a problem-specific optimization you can build with a customizable processor.

To recap, each instruction takes three pipeline cycles to move through the instruction fetch, operand fetch and decode, and execute pipeline stages. Each pipeline cycle requires up to three memory access cycles (mandatory instruction fetch, optional DMA, and optional EX stage load or store). Each memory access cycle requires one or more clock cycles.

### CONTROL UNIT DESIGN

Now that you understand the pipeline, you are ready to design the control unit. (For more information on RISC pipelines, see *Computer Organization and Design: The Hardware*/

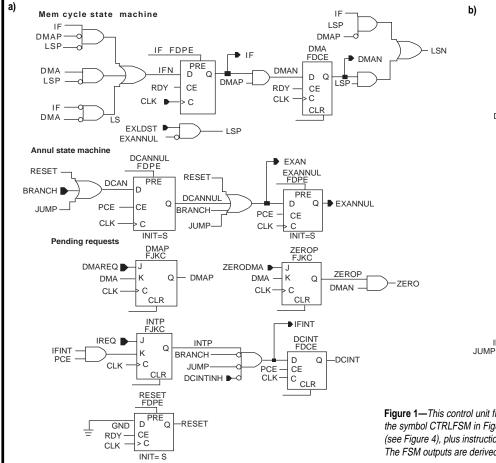

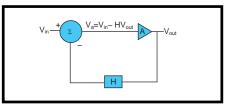

Figure 1—This control unit finite state machine schematic implements the symbol CTRLFSM in Figure 2. It consists of the memory cycle FSM (see Figure 4), plus instruction annulment and pending request registers. The FSM outputs are derived from the machines current and next states.

| RNA                    | When                                                                               |

|------------------------|------------------------------------------------------------------------------------|

| RA                     | DC: add sub addi<br>lw lb sw sb jal                                                |

| RD                     | DC: all rr, ri format                                                              |

| 0                      | DC: call                                                                           |

| EXRD                   | EX: all but call                                                                   |

| 15                     | EX: call                                                                           |

| RNB                    | When                                                                               |

| RB<br>RD<br>EXRD<br>15 | DC: add sub, <i>all rr fmt</i><br>DC: sw sb<br>EX: <i>all but call</i><br>EX: call |

**Table 4**—*RNA* and *RNB* control the A and B ports of the register file. While CLK is high, they select which registers to read, based upon register fields of the instruction in the DC stage. While CLK is low, they select which register to write, based upon the instruction in the EX stage.

Software Interface, by Patterson and Hennessy.) [1] First, some important naming conventions. Some control unit signal names have prefixes and suffixes to recognize their function or context (most signal names sans prefix are DC stage signals):

- Nsig: not signal—signal inverted

- DCsig: a DC stage signal

- EXsig: an EX stage signal

- *sig*N: signal in "next cycle"—input to a flip-flop whose output is *sig*

- *sig*CE: flip-flop clock enable

- *sig*T: active low 3-state buffer output enable

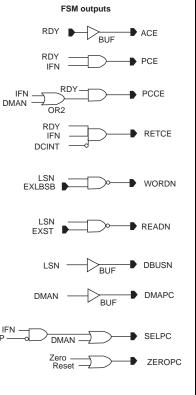

Each instruction flows through the three stages (IF, DC, and EX) of the control unit (see Figure 2) pipeline. In the *IF* stage, when the instruction fetch read completes, the new instruction at  $INSN_{150}$  is latched into IR.

In the *DC stage*, DECODE decodes IR to derive internal control signals. In the first half clock cycle, CTRL drives  $\text{RNA}_{3:0}$  and  $\text{RNB}_{3:0}$  with the source registers to read, and drives FWD and  $\text{IMM}_{5:0}$  to select the A and B operands. If the instruction is a branch, CTRL determines if it is taken. Then as the pipeline advances, the instruction passes into EXIR.

In the *EX stage*, CTRL drives ALU and result mux controls. If the instruction is a load/store, it inserts a memory access. In the last half cycle, RNA and RNB both drive the destination register number to store the result into the register file.

Let's consider each part of the control finite state machine (see Figure 1). The control FSM has three states:

- IF: current memory access is an instruction fetch cycle

- DMA: current access is a DMA cycle

- LS: current access is a load/store

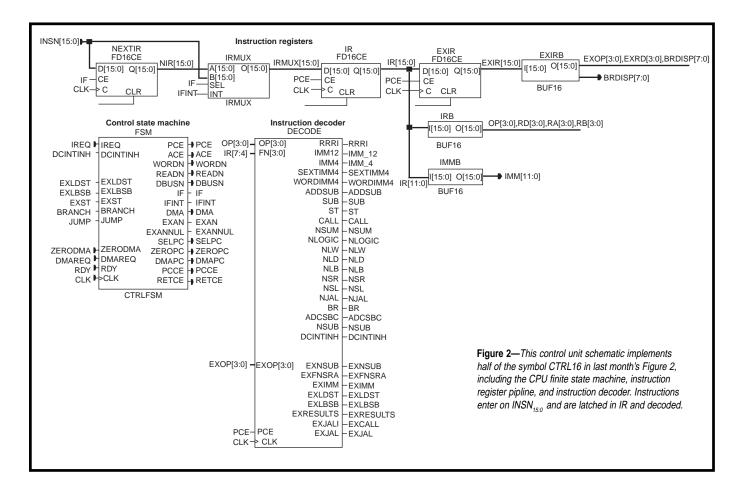

Figure 4 shows the state transition diagram. The FSM clocks when one memory transaction completes and another begins (on RDY). CTRLFSM also has several other bits of state:

- DCANNUL: annul DC stage

- EXANNUL: annul EX stage

- DCINT: int in DC stage

- DMAP: DMA transfer pending

- INTP: interrupt pending

DCANNUL and EXANNUL are set after executing a jump or taken branch. They suppress any effects of

the two instructions in the branch shadow, including register file write-back and load/store memory accesses. So, an annulled add still fetches and adds its operands, but its results are not retired to the register file.

DCINT is set in the pipeline cycle following the insertion of the int instruction. It inhibits clocking of RET for one cycle, so that the int picks up the return address of the interrupted instruction rather than the instruction after that.

The highest fan-out control signal is PCE, the pipeline clock enable. Most datapath registers are enabled by PCE. It indicates that all pipe stages are ready and the pipeline can advance. PCE is asserted when RDY signals completion of the last memory cycle in the current pipeline cycle. If memory isn't ready, PCE isn't asserted, and the pipeline stalls for one cycle.

The control FSM also takes care of managing the memory interface via the following signals:

| Enable | Instruction                            | Source                   |

|--------|----------------------------------------|--------------------------|

| SUMT   | add sub addi<br>adc sbc adci sbci      | SUM <sub>15:0</sub>      |

| LOGICT | and or xor andn<br>andi ori xori andni | LOGIC <sub>15:0</sub>    |

| SLT    | slli                                   | A <sub>14:0</sub>    0   |

| SRT    | srli srai                              | SRI    A <sub>15:1</sub> |

| ZXT    | lb                                     | 0,15:8                   |

| RETADT | jal call                               | RETAD <sub>15:0</sub>    |

| none   | sw sb br* imm                          |                          |

**Table 5**—Here's a look at the result multiplexer output enable controls.The instruction determines which enable is asserted and which functionunit drives  $RESULT_{rs:\sigma}$

- RDY: memory cycle complete (input from the memory controller)

- READN: next memory cycle is a read transaction—true except for stores

- WORDN: next cycle is 16-bit data true except for byte loads/stores

- DBUSN: next cycle is a load/store, and it needs the on-chip data bus

- ACE (address clock enable): the next address AN<sub>15:0</sub> (a datapath output) and the above control outputs are all valid, so start a new memory transaction in the next clock cycle.

ACE equals RDY, because if memory is ready, the CPU is always eager to start another memory transaction.

There are no IF stage control outputs. Internal to the control unit, three signals control IF stage resources. Those three signals are:

- PCE: enable IR and EXIR clocking

- IF: asserted in an instruction fetch memory cycle

- IFINT: force the next instruction to be int = jal r14,10(r0) = 0xAE01

If a DMA or load/store access is pending, IF enables NEXTIR to capture the previously fetched instruction (take a look back at time  $t_3$  in Table 3). Otherwise, the instruction fetch is the only memory access in the pipe stage. So, IF is then asserted with PCE, and IRMUX selects the INSN<sub>15:0</sub> input as the next instruction to complete.

### DECODE STAGE

The greater part of the control unit operates in the DC stage. It must decode the new instruction, control the register file, the A and B operand multiplexers, and prepare most EX stage control signals.

The instruction register IR latches the new instruction word as the DC stage begins. The buffers IRB and IMMB break out the instruction fields OP, RD, and so forth—IR<sub>15:12</sub> is renamed OP<sub>3:0</sub> and so on (the tools optimize away these buffers).

The instruction decoder DECODE is simple. It is a set of 30 ROM 16x1s, gate expressions, and a handful of flip-flops. Each ROM inputs OP<sub>3:0</sub> or EXOP<sub>3:0</sub> and outputs some decoded signal. The decoder is relatively compact because

xr16 has a simple instruction set, and its 4-bit opcodes are a good match for the FPGA's 4 LUTs.

The register file control signals, shared by both the DC and EX stages, are RNA<sub>3:0</sub>: port A register number; RNB<sub>3:0</sub>: port B register number; and RFWE: register file write enable.

With CLK high, CTRL drives RNA and RNB with the DC stage instruction's source register numbers. With CLK low, CTRL drives RNA and RNB with the EX stage destination register number.

RFWE is asserted with PCE when there is a result to write back. It is false for instructions, which produces no result (immediate prefix, branch, or store) for annulled instructions, and for destination r0.

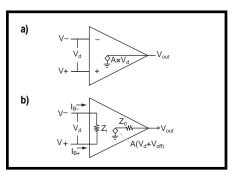

Figure 3—The remainder of the control unit schematic implements the DC stage operand selection logic including register file, immediate operand control, branch logic, EX stage ALU, and result mux controls.

The muxes RNA and RNB produce RNA<sub>3.0</sub> and RNB<sub>3.0</sub>, as shown in Table 4, as selected by decode outputs RRRI, CALL, ST, EXCALL, and CLK. Call is irregular. It computes r15 = pc, pc = r0 + imm12 << 4, and the registers r15 and r0 are implicit.

The FWD signal causes RESULT to be forwarded into A, overriding AREG. CTRL asserts FWD when the EX stage destination register equals the DC stage source register A (detected within RNA), unless the EX stage instruction is annulled or its destination is r0.

Last month, I discussed IMMED, the BREG/immediate operand mux. IMMOP<sub>5:0</sub> controls IMMED, based upon the decoder outputs WORDIMM, SEXTIMM4, IMM\_12, and IMM\_4. the branch instruction enters the EX stage, the BRANCH control output is asserted. This directs PCINCR to take the branch by adding 2×disp8 to the PC.

$B_{3:0}$  is clock enabled

on PCE, but B<sub>15.4</sub> uses

B15\_4CE. B15\_4CE is

prefix establishes B<sub>15:4'</sub>

PCE, unless the EX

stage instruction is

imm. Thus, the imm

and the subsequent

immediate operand

instruction provides

Now, turning to

conditional branches,

instruction is a branch,

if the DC stage

then the EX stage

instruction must be

add, sub, or addi,

condition inputs Z

(zero), N (negative),

CO (carry-out), and V

Late in the DC

evaluates whether or

condition COND is

true with respect to

so, and if the branch

BRANCH flip-flop is

set. Therefore, as the

pipeline advances and

instruction is not

annulled, the

the condition inputs. If

not the branch

stage, the TRUE macro

which drives the

control unit's

(overflow).

$B_{3:0}$  only.

### THE EXECUTE STAGE

Now, let's discuss the EX stage ALU, result mux, and address unit controls. The ALU and shift control outputs are:

- ADD: set unless the instruction is sub or sbc

- CI: carry-in. 0 for add and 1 for sub, unless it's adc or sbc where we XOR in the previous carry-out

- LOGICOP<sub>1:0</sub>: select and, or, xor, or andn. LOGICOP<sub>1:0</sub> is simply EXIR<sub>5:4</sub> (i.e., EX stage copy of FN<sub>1:0</sub>)

- SRI: shift right input—0 for srli

| Next cycle              | Next address                                                                                                                             | Outputs                                     |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| IF<br>IF branch         | $\begin{array}{l} AN \leftarrow PC_{_0} \texttt{+=} \texttt{2} \\ AN \leftarrow PC_{_0} \texttt{+=} \texttt{2} \times disp8 \end{array}$ | SELPC PCCE<br>BRANCH SELPC PCCE             |

| IF jal call             | $AN \gets PC_{_0} = SUM$                                                                                                                 | PCCE                                        |

| IF <i>reset</i>         | $AN \leftarrow PC_0 = 0$                                                                                                                 | SELPC ZEROPC PCCE                           |

| LS load/store           | $AN \gets SUM$                                                                                                                           | _                                           |

| DMA<br>DMA <i>reset</i> | $\begin{array}{l} AN \leftarrow PC_1 \texttt{+=} \texttt{2} \\ AN \leftarrow PC_1 \texttt{=} \texttt{0} \end{array}$                     | SELPC DMAPC PCCE<br>SELPC ZEROPC DMAPC PCCE |

**Table 6**—Here's a look at the result multiplexer output enable controls. The instruction determines which enable to assert and thus determines which function unit drives the RESULT bus.

and  $\boldsymbol{A}_{\scriptscriptstyle 15}$  for srai (shift right arithmetic)

slxi and srxi (shift extended left/ right for multi-word shift support) are not yet implemented. Be my guest!

The result mux control outputs SUMT, LOGICT, SLT, SRT, SXT, and RETADT are active low RESULT bus 3-state output enables. Each cycle, all EX stage function units produce results. One asserted *T* enables its unit's 3-state buffers to drive the RESULT bus, as shown in Table 5.

ZXT zeroes  $\text{RESULT}_{15:8}$  during 1b. As you'll see next month, the system drives  $\text{RESULT}_{7:0}$  with the byte load result.

The following outputs control the address unit:

- BRANCH: if set, add 2×disp8 to PC, otherwise add +2

- SELPC: if set, next address is PCNEXT<sub>15:0'</sub> otherwise SUM<sub>15:0</sub>

- ZEROPC: if set, next address is 0

Figure 4—Each memory cycle is an instruction fetch unless there is a DMA transfer pending or the EX stage instruction is a load or store. The FSM clocks when one memory transaction completes and another begins (on RDY).

- PCCE (PC clock enable): update PC<sub>i</sub>

- DMAPC: if set, fetch and update PC<sub>1</sub> (DMA address), otherwise PC<sub>0</sub> (PC)

Depending on the next memory cycle and the current EX stage instruction, the control unit selects the next address by asserting certain combinations of control outputs (see Table 6).

### WRAP-UP

This month, we considered pipelined processor design issues and explored the detailed implementation of our xr16 control unit—and lived! The CPU design is complete. The final article in this series tackles the design of this System-on-a-Chip.

Jan Gray is a software developer whose products include a leading C++ compiler. He has been building FPGA processors and systems since 1994, and he now designs for Gray Research LLC. You may reach him at jan@fpgacpu.org.

### SOFTWARE

Visit the *Circuit Cellar* web site for more information, including specifications, source code, schematics, and links to related sites.

### REFERENCE

D. Patterson and J. Hennessy, Computer Organization and Design: The Hardware/Software Interface, Morgan Kaufmann, San Mateo, CA, 1994.

# The Shocking Truth about EMC

George Novacek

### Part 1: Design for Compatibility

Designing for electromagnetic compatibility shouldn't just be an afterthought. As George shows us, if you wait until EMC causes a problem, you just might find yourself doing quite a bit of redesigning. Listen up and save yourself the trouble. he tremendous growth in electromagnetic compatibility (EMC) importance has affected all of us. Aerospace engineers have seen their requirements skyrocket while designers of communications and commercial electronics, especially those in the European countries, have had dozens of stringent new requirements imposed on them.

With the greater sophistication of simple appliances, we increasingly rely on flawless performance of electronics. With the profusion of cellular phones, pagers, and ever-escalating computer clock speeds leading the pack, we generate a huge amount of electromagnetic garbage, all of which seems to choke and confuse every electronic device within its reach.

Electromagnetic compatibility has, for many years, been viewed as black magic. Designers shied away from it, hoping that by copying previous successful designs, the problems would go away. And, quite often they did.

Unfortunately, this approach no longer works. The quest for better performance, lower cost, smaller size, and shorter time to market forces designers to understand the problems before they can find the remedy. In this article, I'll look at taking control of and taming the EMC beast. I'll discuss some fundamental principles of designing electronic equipment in compliance with the regulatory requirements. Even if no government certification is required, it is our duty as engineers to make sure our products work under adverse conditions. At the very least, it's a matter of professional pride.

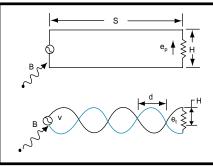

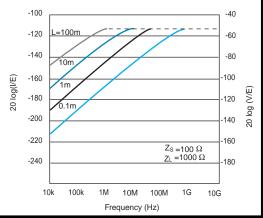

It would be impractical and outside the scope of this article to write a cookbook to satisfy every conceivable situation. Rather, I'll concentrate on the principles, methods, and their application to critical level aerospace requirements as reflected in the DO-160D or MIL-STD-461D standards. It's up to you to transpose these principles to your design environments, which are probably less demanding (e.g., aerospace insists on 200 V/m immunity, but commercial equipment rarely encounters more than 20 V/m). Those interested in deeper technical details can consult the references.

### FIRST THINGS FIRST

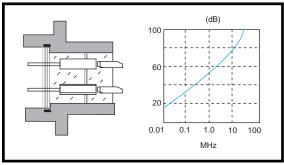

The first step in destroying its black-magic reputation, is to treat EMC as any other design problem. Once you define it, you need to form a plan of attack.