# **SERVICE MANUAL**

# Zenith Local Area Network Interface Card (NET-100-1)

**Z-100 Series Computers**

585-49-02

The purpose of this page is to make sure that all service bulletins are entered in this manual. When a service bulletin is received, annotate the manual and list the information in the record below.

### **Record of Service Bulletins**

| SERVICE<br>BULLETIN<br>NUMBER | DATE<br>OF<br>ISSUE | CHANGED<br>PAGE(S) | PURPOSE OF SERVICE<br>BULLETIN | INITIALS |

|-------------------------------|---------------------|--------------------|--------------------------------|----------|

|                               |                     |                    |                                |          |

|                               |                     |                    |                                |          |

|                               |                     |                    |                                |          |

|                               |                     |                    |                                |          |

|                               |                     |                    |                                |          |

|                               |                     |                    |                                |          |

|                               |                     |                    |                                |          |

|                               |                     |                    |                                |          |

#### LIMITED RIGHTS LEGEND

Contractor is Zenith Data Systems Corporation of St. Joseph, Michigan 49085. The entire document is subject to Limited Rights data provisions.

Copyright © 1982, 1983 Standard Microsystems Corporation, Copyright © 1984 Zenith Data Systems Corporation, all rights reserved. Printed in the United States of America

# **Contents**

| Figures               | v                                      |

|-----------------------|----------------------------------------|

| •                     | v                                      |

|                       | vi                                     |

|                       | vii                                    |

| Specifications        | ······································ |

| Chapter 1             | Introduction                           |

|                       |                                        |

|                       |                                        |

|                       |                                        |

|                       |                                        |

|                       |                                        |

|                       |                                        |

|                       |                                        |

|                       | 1-8                                    |

| Charter 0 Ha          | rdware and Host Computer Requirements  |

|                       |                                        |

|                       |                                        |

| S-100 Bus Pin         |                                        |

| Chapter 3             | Disassembly                            |

| Introduction          |                                        |

|                       |                                        |

| Charter 4             | Configuration                          |

| Chapter 4             | Configuration 4-1                      |

| Introduction          | 4-1                                    |

| Typical Configuration | 4-3                                    |

|                       |                                        |

|                       |                                        |

| Switches              | 4-0                                    |

| Chapter 5             | Installation                           |

| Introduction          |                                        |

|                       | 5-1                                    |

|                       | llation 5-2                            |

| Charter 6             | Initial Tests                          |

| Chapter 6             | 6-1                                    |

|                       |                                        |

|                       | 6-2                                    |

|                       |                                        |

| memory rest           | 6-3                                    |

| Chapter 7             | Reassembly                             |

| Introduction          |                                        |

| Reassembly            | 7-1                                    |

## Contents

| Chapter 8                                | Theory of Operation                     |

|------------------------------------------|-----------------------------------------|

| Introduction                             |                                         |

| Bus Buffers                              |                                         |

| Multiplexers (MUX)                       |                                         |

| System Decode and Control                |                                         |

| Wait Generation                          |                                         |

| Read Only Memory (ROM)                   |                                         |

| Random Access Memory (RAM)               |                                         |

| Network Controller                       |                                         |

| ID Number                                |                                         |

| Active Hub                               |                                         |

| Active Hub                               |                                         |

| Chapter 9                                | Circuit Description                     |

| Introduction                             | Q.1                                     |

| Bus Buffers                              |                                         |

|                                          |                                         |

| Multiplexers                             |                                         |

| COM9026 Interface (U116)                 |                                         |

| System Decode and Control                |                                         |

| 16-bit Addressing                        |                                         |

| 8-bit Addressing                         |                                         |

| Interrupt                                |                                         |

| Phantom                                  |                                         |

| Wait Generation                          |                                         |

| ROM Circuitry                            |                                         |

| RAM Interface                            |                                         |

| Network Controller                       |                                         |

| ID Number                                |                                         |

| Active Hub                               |                                         |

|                                          |                                         |

| Chapter 10                               | Service Instructions                    |

| Introduction                             | 10-1                                    |

| Troubleshooting                          | 10-1                                    |

|                                          |                                         |

| Chapter 11                               | Parts List                              |

| Introduction                             |                                         |

| Replacement Parts                        |                                         |

| NET-100-1 Network Card                   | *************************************** |

| Network Chassis Adapter                  | 44.0                                    |

| Semiconductor Identification             | 11-0                                    |

| Semiconductor Identification             | 11-8                                    |

| Part Number Index                        |                                         |

| PAL Equations                            |                                         |

| Chapter 12                               | Data Sheets                             |

|                                          | Data Sneets                             |

| Introduction                             | 12-1                                    |

| Data Sheets — COM9026 Local Area Network | Controller (LANC) 12-2                  |

| - COMPUSE LOCAL AREA Network             | Transceiver (LANT) 12-16                |

## Contents

### Appendix A

### **ID Node Number Lockup Table**

## **Figures**

| 1-1  | ZLAN Topology                         |

|------|---------------------------------------|

| 1-2  | Dalsy Chain Configuration             |

| 1-3  | Tree Configuration 1-5                |

| 1-4  | Logical Network                       |

| 3-1  | Disassembly, All-in-One Model         |

| 3-2  | Disassembly, Low-Profile Model        |

| 4-1  | Typical Configuration                 |

| 4-2  | Configuration Jumpers 4-3             |

| 4-3  | Configuration Switches 4-5            |

| 5-1  | NET 100-1 Card Installation 5-1       |

| 5-2  | Network Chassis Adapter Installation  |

| 7-1  | Reassembly, All-in-One Model          |

| 7-2  | Reassembly, Low-Profile Model         |

| 8-1  | NET-100-1 Block Diagram               |

| 9-1  | Interrupt Jumpers9-3                  |

| 9-2  | Timing Diagram 9-4                    |

| 9-3  | ROM Insertion                         |

| 11-1 | Component View NET 100-1 Card         |

| 11-2 | Network Chassis Adapter Exploded View |

|      |                                       |

## **Tables**

| 9-1  | ROM Jumper Configuration9-7 |

|------|-----------------------------|

| 10-1 | Troubleshooting             |

## **Abbreviations**

ACK Acknowledgment

ADIE Address/Data Input Enable

AS Address Strobe

BINP Bus Input

BMEMR Bus Memory

BOUT Bus Output

BSYNC Bus Synchronization

CE Chip Enable CLK Clock

CR Carriage Return

DBIN Data Bus Input

DID Destination Identification Number

DIP Dual Inline Pack

DIS Disable

EN Enable

EOT End Of Time

ESDS Electrostatic Sensitive Devices

ET Extended Timeout LED Light Emitting Diode

IDDAT ID Data In IDLD ID Load I/O Input/Output

ILE Interface Latch Enable

IM Interface Module

IOADRS Input Output Address

IOREQ Input Output Request

ID Identification Number

INTR Interrupt

LANC Local Area Network Controller

LANT Local Area Network Transceiver

MASM Macroassembler

MEMADRS Memory Address

MEMREQ Memory Request

MUX Multiplexer

NAK No Acknowledgment NID Next Identification Number

OE Output Enable

### **Abbreviations**

PAL Programmable Array Logic

PR Preset Lines

PRSFF Preset Flip-Flop

PULS Pulse

RAM Random Access Memory

RDY Ready REQ Request

ROM Read Only Memory

ROMSEL ROM Select RX Receive

SID Source Identification Number

TX Transmit WE Write Enable

ZLAN Zenith Local Area Network

# **Specifications**

Buffer RAM Size . . . . . . . . . . . . . . . . .  $2K \times 8 (6116-4)$

$4K \times 1 (2732-2)$

8K × 8 (2764-2)

16K × 8 (27128-2)

Jumper selectable 8-bit or 16-bit addressing

Memory Addressing . . . . . . . . . . . . . . . . Jumper selectable 16-bit or 24-bit addressing

Maximum Distance Between Units . . . . . 2000 feet

Maximum Nodes Per System . . . . . . . . 255

Jumper selectable VI0\*-VI7\*, NMI, and INT\*

Local Area Network Controller . . . . . . SMC COM9026

Local Area Network Interface . . . . . . . Zenith Hybrid EGA059102A

RAM/I/O Access Time . . . . . . . . . . . . . . . . 880 ns maximum

ROM Access Time . . . . . . . . . . . . . . . . . 220 ns maximum

Cable Interface . . . . . . . . . . . . . . . . . . RG62A Coax, 93 Ohms BNC Connector

S-100, IEEE Standard 696

8-11 volts DC

Typical 1.6A, Maximum 2.0A

- 12 volts DC at .03A

# Chapter 1 Introduction

This chapter introduces the NET-100-1 Card, Zenith Local Area Network (ZLAN) operation, parts supplied, and the tools required for installation.

### NET-100-1 Card

The NET-100-1 Card is a local area networking card compatible with Data point's ARCNET System. It will allow the Z-100 Computer to interface with up to 255 similarly configured computers, at a maximum distance of 2000 feet. An active 4-port hub is incorporated on the NET-100-1 Card. A local area network can be set up by daisy chaining or with the hub, using the appropriate software. This card is supplied fully populated, and may be placed in any vacant card slot in the computer.

The active hub requires all units in a path or tree to be powered up for the system to communicate properly.

The card can be configured in many ways with the available switches and jumpers. This capability is especially useful for configuring the memory on the card around system memory. Yet, the card can be used as supplied, fully configured except for the ID number. The ID number is a switch set to the desired ID number. Refer to appendix A for number selection and conversion.

All of the information needed to use the features of the NET-100-1 Card is contained within this manual. Please read it carefully before attempting to use the NET-100-1 Card.

## **Network Operation**

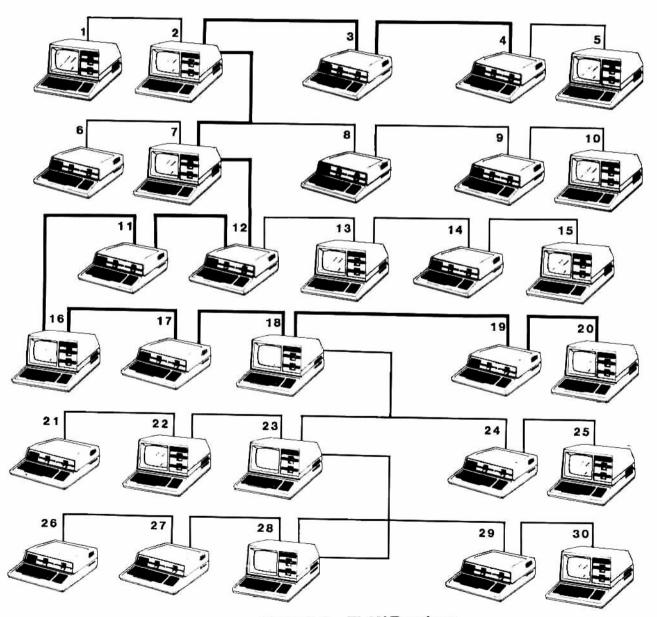

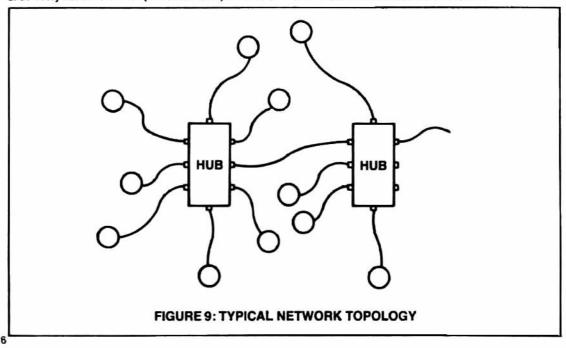

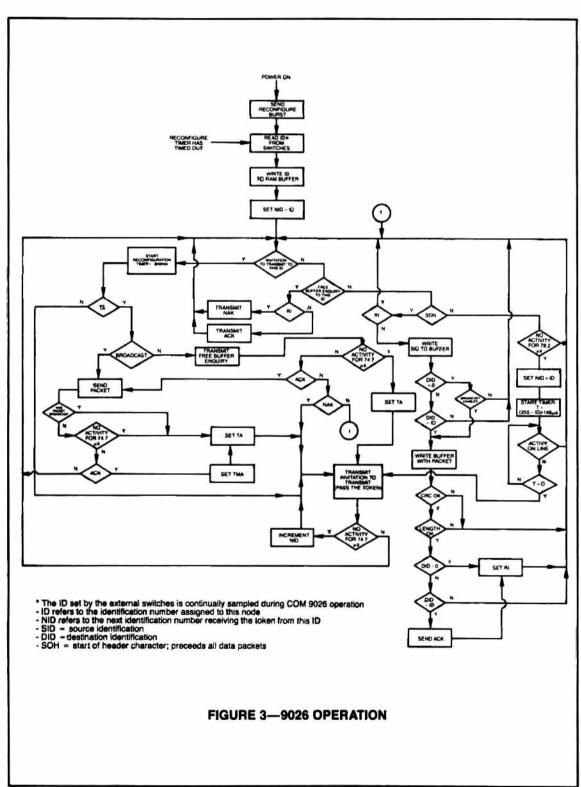

ZLAN consists of a token-passing scheme, where each node (unit) passes to the next active higher ID number an invitation to transmit. Up to 255 unique node numbers may be assigned to a ZLAN network (refer to Figure 1-1).

Figure 1-1. ZLAN Topology

Refer to Figure 1-1 for the following example.

**EXAMPLE:** Node 4 desires to communicate to node 20. The interconnecting nodes must be powered on because the board has an **active\***hub.

Nodes: 2, 3, 4, 7, 11, 12, 16, 17, 18, 19, and 20.

The network can be configured in two ways. Each has advantages and disadvantages which depend on the system to be installed. For the highest efficiency network, determine which configuration is best for the system.

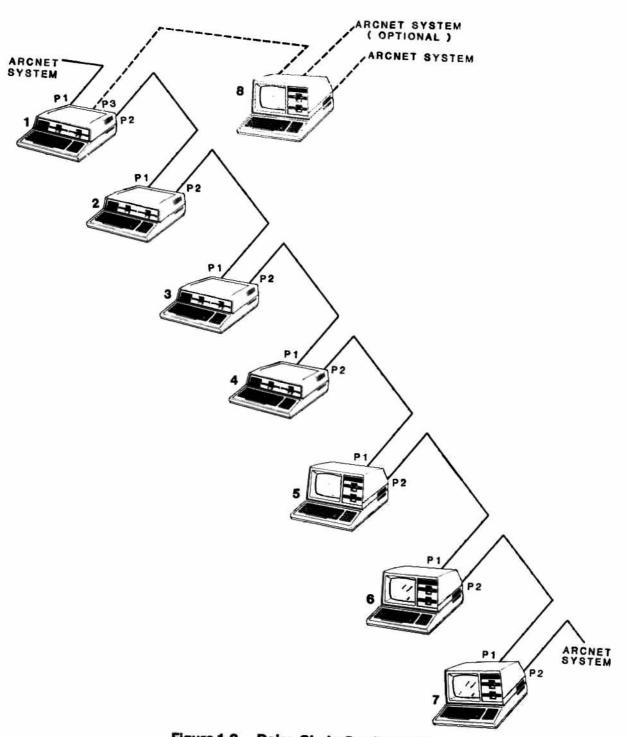

Figure 1-2 shows a daisy chain configuration. The main advantage of this configuration is that a unit may be easily inserted into the system, keeping cable runs at a minimum. The disadvantage of this system is that all units must be powered on for communications to occur.

For example, a network system is set in a company where 5 of 20 units are, at times, inaccessible to the other users. Using a daisy-chain configuration, the entire system will not be able to communicate if any unit is powered down. Without access to 5 computers, those physical lines must be bypassed, (if this is even possible) for the network to communicate. This is an undesirable situation which can be avoided by using the tree configuration.

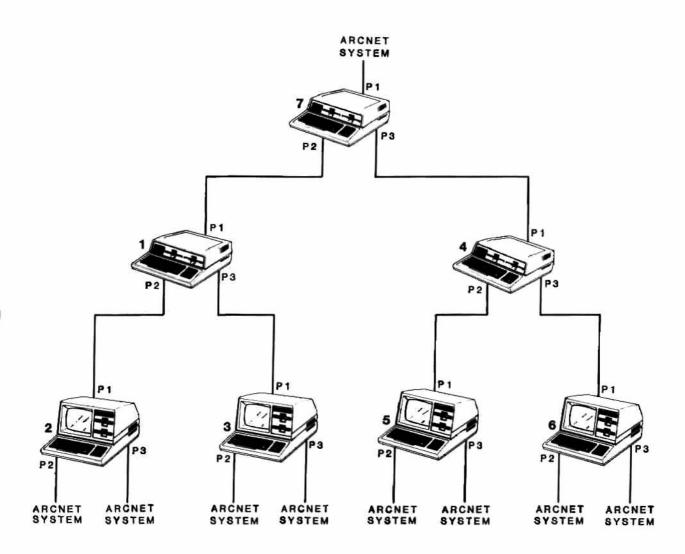

Figure 1-3 shows a basic tree configuration. Set up in branches, this configuration does not require all systems to be powered on for communication to occur, just the individual branch must be active. The main disadvantage is that the tree configuration does require prethought on wiring. Possible future sites should be taken into consideration while connecting the system, when using the tree configuration.

In the tree configuration, the unaccessible 5 computers can be set in a separate branch, allowing the network to communicate without these units powered on.

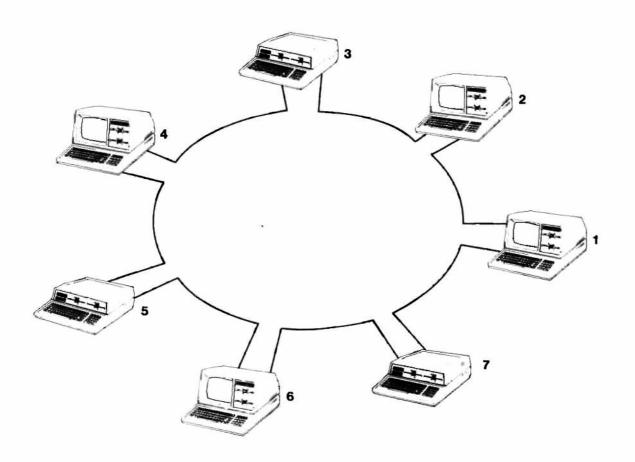

Although these configurations may look unique, the logical network is the same, as shown in Figure 1-4. **Do not** connect the network in this manner. Use only a daisy chain or tree configuration.

### Introduction

Figure 1-2. Dalsy Chain Configuration

Figure 1-3. Tree Configuration

Figure 1-4. Logical Network

## **Network Reconfiguration**

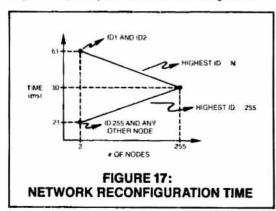

At network reconfiguration time, all ID numbers, up to 255, are polled. Each node will remember the next ID number (NID) the token was passed to. In this way, the token will be passed only to active ID numbers, preventing wasted time. Every time a node is powered up in the network, a network reconfiguration will occur. The network reconfiguration (consisting of eight marks and one space repeated 765 times) will destroy the token and prevent another node from taking control of the network.

When a node is powered down or disconnected, there is no need for a network reconfiguration. When the preceding node does not receive a response from its invitation to transmit, it will increment the NID it has stored and send another invitation to transmit. The node will continue to increment the NID and retransmit until a response is received from an active node.

### **Packet Transfer**

#### **Transmit**

When a node receives the token and it has a packet or message it wants to send, it looks at the destination ID (DID) and sends a free buffer inquiry to that ID (if the DID is 0, it signifies a broadcast to all nodes). If the DID responds with an acknowledge (ACK), the node will send the packet. If there is no acknowledgment (NAK) or ACK is not received after 74 microseconds, the node will pass the token to the NID.

#### Receive

The node receiving a free buffer inquiry checks the receiver inhibited flag. If the flag is set, an NAK is sent to the source ID (SID); if not, an ACK is sent.

### Introduction

When a packet is transmitted, the receiving node first writes the SID into its receive buffer. Next, it will look at the DID. If the DID is neither 0 nor its ID number, the node will ignore the rest of the packet.

If the DID corresponds to the receiving node's ID number, the node will send an ACK to the SID, set the receiver inhibited flag, and write the packet into its receiver buffer. For a broadcast (DID=0), the node will store the packet in its receive buffer if broadcast reception is enabled. If not enabled, the node will ignore the rest of the packet.

## **Parts Supplied**

The following parts are supplied in this interface card package:

- NET-100-1 Card

- NET-100-1 Chassis Adapter

- (2) 6-BT × .375" Screws

- NET-100-1 USER'S MANUAL

The following accessories are optional:

- HCA-60 25 foot coax cable.

- HCA-61 100 foot coax cable.

### **Tools Required**

The only tools required for the installation of the NET-100-1 Card are a small flat blade screwdriver and a small Phillips screwdriver.

# **Hardware and Host Computer Requirements**

### Introduction

The NET-100-1 Card uses the S-100 Bus Interface, IEEE Standard 696. Therefore, computers used with this card must meet the same standard. Listed below are the S-100 Bus pins used, signal, type, and their active level.

### S-100 Bus Pin

| PIN NO. | SIGNAL/TYPE           | ACTIVE LEVEL                |  |

|---------|-----------------------|-----------------------------|--|

| 4       | VIO* (S)              | L O.C. (Low open collector) |  |

| 5       | VI1* (S)              | L O.C.                      |  |

| 6       | VI2* (S)              | L O.C.                      |  |

| 7       | VI3* (S)              | L O.C.                      |  |

| 8       | VI4* (S)              | L O.C.                      |  |

| 9       | VI5* (S)              | L O.C.                      |  |

| 10      | VI6* (S)              | L O.C.                      |  |

| 11      | VI7* (S)              | L O.C.                      |  |

| 12      | NMI* (S)              | L O.C.                      |  |

| 15      | A18 (M)               | н                           |  |

| 16      | A16 (M)               | н                           |  |

| 17      | A17 (M)               | н                           |  |

| 20      | GND (B)               | 0 Volts Line                |  |

| 24      | OI (B)                | Н                           |  |

| 29      | A5 (M)                | н                           |  |

| 30      | A4 (M)                | н                           |  |

| 31      | A3 (M)                | Н                           |  |

| 32      | A15 (M)               | н                           |  |

| 33      | A12 (M)               | н                           |  |

| 34      | A9 (M)                | н                           |  |

| 35      | DO1 (M) /DATA1 (M/S)  | н                           |  |

| 36      | DO0 (M) /DATA0 (M/S)  | н                           |  |

| 37      | A10 (M)               | н                           |  |

| 38      | DO4 (M) /DATA4 (M/S)  | н                           |  |

| 39      | D05 (M) /DATA5 (M/S)  | н                           |  |

| 40      | DO6 (M) /DATA6 (M/S)  | н                           |  |

| 41      | DI2 (M) /DATA10 (M/S) | н                           |  |

# Hardware and Host Computer Requirements

| PIN NO. | SIGNAL/TYPE           | ACTIVE LEVEL |

|---------|-----------------------|--------------|

| 42      | DI3 (M) /DATA11 (M/S) | Н            |

| 43      | DI7 (M) /DATA15 (M/S) | Н            |

| 45      | sOUT (M)              | н            |

| 46      | sINP (M)              | н            |

| 47      | sMEMR (M)             | н            |

| 50      | GND (B)               | 0 Volts Line |

| 51      | +8 Volts (B)          |              |

| 52      | -16 Voits (B)         |              |

| 53      | GND (B)               | 0 Volts Line |

| 59      | A19 (M)               | Н            |

| 61      | A20 (M)               | н            |

| 62      | A21 (M)               | н            |

| 63      | A22 (M)               | н            |

| 64      | A23 (M)               | Н            |

| 67      | PHANTOM* (M/S)        | L O.C.       |

| 70      | GND (B)               | 0 Volts Line |

| 72      | RDY (S)               | H O.C.       |

| 73      | INT* (S)              | L O.C.       |

| 75      | RESET* (B)            | L O.C.       |

| 76      | pSYNC (M)             | Н            |

| 77      | pWR* (M)              | ï            |

| 78      | pDBIN (M)             | H            |

| 79      | A0 (M)                | H            |

| 80      | A1 (M)                | H            |

| 81      | A2 (M)                | н            |

| 82      | A6 (M)                | H            |

| 83      | A7 (M)                | Ĥ            |

| 84      | A8 (M)                | Ä            |

| 85      | A13 (M)               | H            |

| 86      | A14 (M)               | н            |

| 87      | A11 (M)               | H            |

| 88      | DO2 (M) /DATA2 (M/S)  | н            |

| 89      | DO3 (M) /DATA3 (M/S)  | н            |

| 90      | DO7 (M) /DATA7 (M/S)  | Ĥ            |

| 91      | DI4 (S) /DATA12 (M/S) | н            |

| 92      | DIS (S) /DATA13 (M/S) | H            |

| 93      | DI6 (S) /DATA14 (M/S) | н<br>н       |

| 94      | DI1 (S) /DATA9 (M/S)  | н            |

| 95      | DIO (S) /DATA8 (M/S)  | Ĥ            |

| 96      | sWO* (M)              | ï'           |

| 100     | GND (B)               | 0 Volts Line |

|         |                       |              |

# Chapter 3 Disassembly

### Introduction

This chapter provides the information to remove the top of the Z-100 Computer for NET-100-1 Card installation.

**WARNING:** Dangerous DC voltages are present inside the computer. Be sure the line cord is disconnected.

## Disassembly

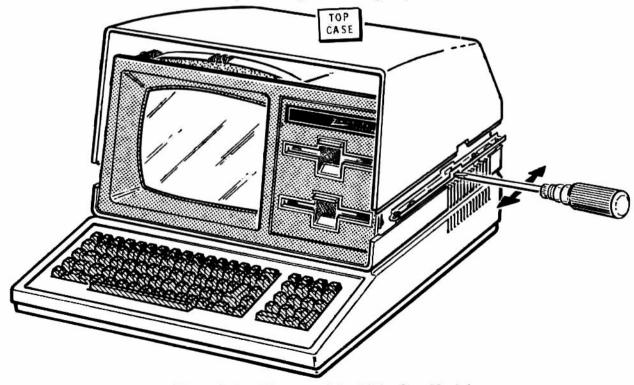

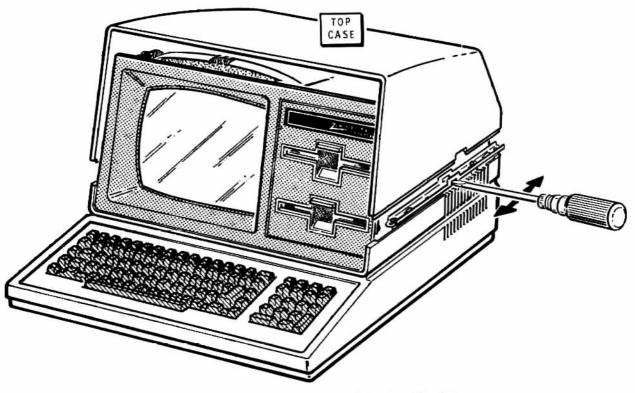

All-in-One Model — Refer to Figure 3-1 and complete the following steps.

- 1. Unplug the line cord from the AC outlet.

- 2. Using a small flat blade screwdriver, move the metal slides all the way to the front and then 1/4" to the back as shown.

- 3. Carefully lift the top case straight up and set it to one side.

Figure 3-1. Disassembly, All-in-One Model

### Disassembly

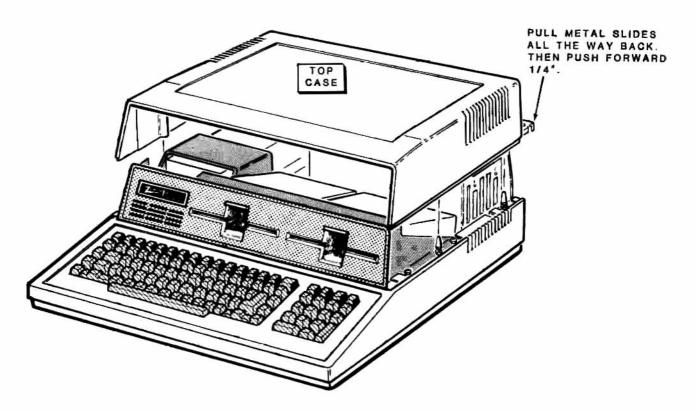

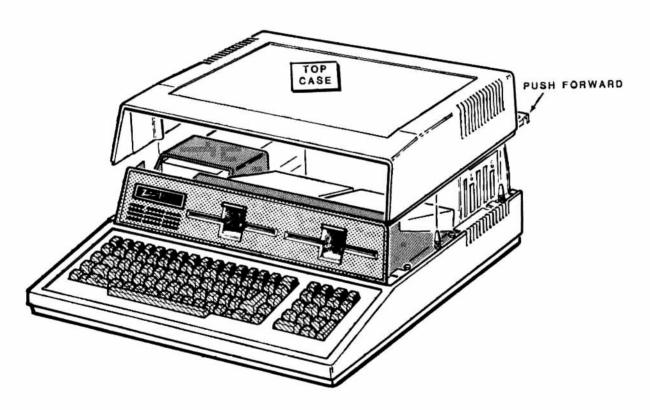

**Low-Profile Model** — Refer to Figure 3-2 and complete the following steps.

- Unplug the line cord from the AC outlet.

- 2. Pull the metal slides all the way to the back, and then push the metal slides 1/4" to the front, as shown.

- 3. Carefuly lift the top case straight up and set it to one side.

Figure 3-2. Disassembly, Low-Profile Model

# Chapter 4 Configuration

### Introduction

This chapter describes the typical factory configuration used with the Z-100 Computer. Detailed configuration information is furnished for Z-100 users who desire to modify or customize their configuration, and non-Zenith Data System microcomputers with S-100 Bus compatiblity.

## **Typical Configuration**

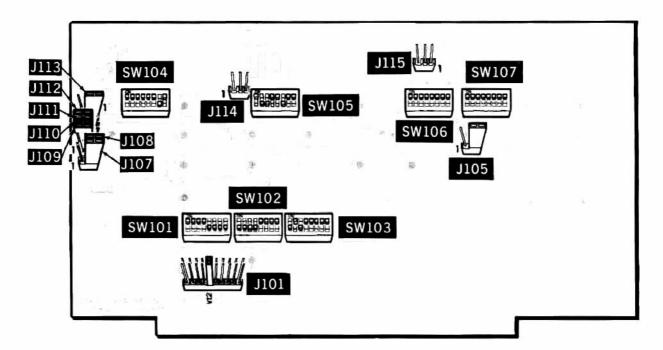

The following is the typical board configuration which is preset at the factory. Refer to Figure 4-1 while reading this section.

**CAUTION:** This product contains ESDS (electrostatic sensitive) devices. Exercise normal caution in handling these devices to prevent static discharge damage.

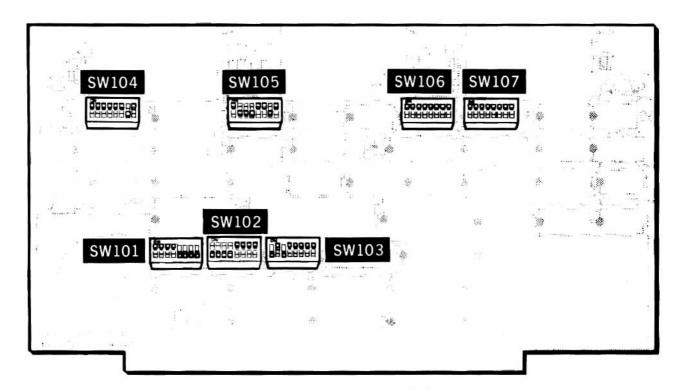

Figure 4-1. Typical Configuration

### Configuration

- Programming jumper across J101, pin 5 (VI2\* interrupt).

- Programming jumper on J105, pins 2 and 3 (right) (8-bit I/O addressing).

- Programming jumper on J107 and J108, pins 2 and 3 (right), and J109, J110, and J111, pins 1 and 2 (left) (test points on COM9026 chip).

- Programming jumper on J112, pins 1 and 2 (left), and J113, pins 2 and 3 (right) (2764-2 ROM).

- DIP (Dual Inline Pack) Switch SW101 positions 0 3 to the ON (0) position and all others to the OFF (1) position to select 0F0000H for the RAM address.

- DIP Switch SW102 positions 0, 1, 2 and 3 to the OFF (1) position and all others to the ON (0) position to select 0F4000H for the ROM address.

- DIP Switch SW103 positions 0 and 2 to the OFF (1) position and all others to the ON (0) position to select 00A0H for the I/O address.

- Dip Switch SW104 position 6 to the OFF(1) position and all other positions to the ON (0) position.

- DIP Switch SW105 is the ID number switch. Set this to the ID number you desire. (Each unit in the system must have a unique ID number.) For example, for ID number 100 (64H), set positions 1, 2 and 5 to the OFF (1) position and all others to the ON (0) position, as shown. Refer to appendix A for cross reference to other ID numbers and their respective positions.

POSITION 0 1 2 3 4 5 6 7 ON/OFF ON OFF OFF ON ON OFF ON ON

**NOTE:** To insure proper setting refer to memory test in Chapter 6.

- Dip Switch SW106 all positions to the ON (0) position.

- Dip Switch SW107 all positions to the ON (0) position.

## **Detailed Configuration Data**

The following information is furnished to configure the NET-100-1 Card for non-Zenith Data System S-100 Bus compatible microcomputers, as well as for the Z-100 user who desires to make modifications or effect a customized configuration.

**CAUTION:** This product contains ESDS (electrostatic sensitive devices). Exercise normal caution in handling these devices to prevent static discharge damage.

Refer to Figure 4-2 for the locations of the jumpers.

Figure 4-2. Configuration Jumpers

### Configuration

### **Jumpers**

J101 — Selects the interrupt on the S100 Bus. Only one of the following should be jumpered.

NMI\*

INT\*

VIO\*

VI1\*

VI2\*

VI3\*

VI4\*

VI5\*

V16\*

V17\*

J105 — For 16-bit addressing pins 1 and 2 are jumpered; for 8-bit addressing, pins 2 and 3 are jumpered.

J107 (T2) — Jumper pins 2 and 3 for normal COM9026 operation. When pins 1 and 2 are jumpered, chip level testing can be performed.

J108 (T1) — Jumper pins 2 and 3 for normal COM9026 operation. When pins 1 and 2 are jumpered, chip level testing can be performed.

J109 (ECHO) — Jumper pins 1 and 2 for normal COM9026 operation. When pins 2 and 3 are jumpered, COM9026 will retransmit all messages less than 254 bytes.

J110, J111 — These two jumpers specify the time-out durations as follows:

| ET2 | ET1 | RESPONSE<br>TIME (us) | RECONFIGURATION<br>TIME (ns) |

|-----|-----|-----------------------|------------------------------|

| 1   | 1   | 74.7                  | 840                          |

| 1   | 0   | 283.4                 | 1680                         |

| 0   | 1   | 561.8                 | 1680                         |

| 0   | 0   | 1118.6                | 1680                         |

J112 — When using a 27128 ROM, jumper pins 2 and 3. For other size ROM's, jumper pins 1 and 2.

J113 — When using a 2732 ROM, jumper pins 1 and 2. For 2764 or 27128, jumper pins 2 and 3.

J114 — When pins 2 and 3 are jumpered, the EPROM will not cause PHANTOM\* to be active. When pins 1 and 2 are jumpered, PHANTOM\* will be active when the ROM is selected.

J115 — When using a 2732 ROM, jumper pins 2 and 3. For a 27128, jumper pins 1 and 2. For a 2764, no jumper is required.

#### **Switches**

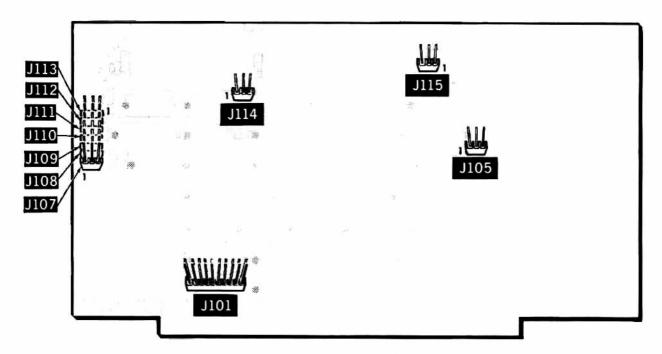

Refer to Figure 4-3 for the location of the switches. In the following configurations, OFF equates to a logic "1", and ON to a logic "0".

Figure 4-3. Configuration Switches

### Configuration

**SW101** — This switch, in conjunction with SW106, selects the memory address location for the RAM. For example, to select the address 0F000 (HEX), SW101 would have the following configuration:

POSITION 0 1 2 3 4 5 6 7

ADDRESS BIT A23 A22 A21 A20 A19 A18 A17 A16

ON/OFF ON ON ON ON OFF OFF OFF

**SW102** — This switch, in conjunction with SW104, selects the location of the ROM. For example, to select the address 0F4000 (Hex), SW104 would have the following configuration:

POSITION 0 1 2 3 4 5 6 7

ADDRESS BIT A16 A17 A18 A19 A20 A21 A22 A23

ON/OFF OFF OFF OFF ON ON ON ON

**SW103** — This switch, in conjunction with SW107, selects the I/O address location. For example, to select 00A0 (HEX), SW107 would have the following configuration:

7 POSITION 1 2 3 5 6 ADDRESS BIT A5 NC A7 A6 A4 **A3** A2 A1 OFF ON OFF ON ON ON ON ON/OFF X

**SW104** — This switch, in conjunction with SW102, selects the location of the ROM, 0F4000; SW104 would have the following configuration:

POSITION ADDRESS BIT NC NC NC NC NC A15 A14 A13 ON/OFF X Х Х Х X ON OFF ON

**SW105** — This switch selects the ID node number. There should be a unique node number for every unit in the network. When position 7 is set OFF and all other positions ON, the ID node number is 1. When position 6 is set OFF and all other positions ON, the node number is 2, etc. The following settings will select ID node number 114 (72H):

POSITION 0 1 2 3 4 5 6 7 ON/OFF ON OFF OFF ON ON OFF ON

**NOTE:** This 114 number is different from the typical configuration to provide another example of ID number selection.

NOTE: To insure proper setting refer to memory test in Chapter 6.

**SW106** — This switch, in conjunction with SW101, selects the MEMADRS location, 0F0000H.

POSITION 1 2 3 5 7 ADDRESS BIT A15 A14 A13 A12 A11 NC NC NC ON/OFF ON ON ON ON X ON X

**SW107** — This switch, in conjunction with SW103, selects the IOADRS location.

**POSITION** 0 2 3 5 1 A12 A13 A14 A15 ADDRESS BIT A9 A10 A11 **A8** ON/OFF ON ON ON ON ON ON ON ON

# Chapter 5 Installation

### Introduction

This chapter provides the necessary information to install the NET-100-1 Card and Network Interface.

### **NET-100-1 Card Installation**

**CAUTION:** This product contains ESDS (electrostatic sensitive devices). Exercise extreme care in handling these devices to prevent damage.

Refer to Figure 5-1 and complete the following steps.

- Select a vacant card slot in the card cage assembly.

- 2. Disconnect 8 inch disk drive cable (134-1264), if used.

Figure 5-1. NET 100-1 Card Installation

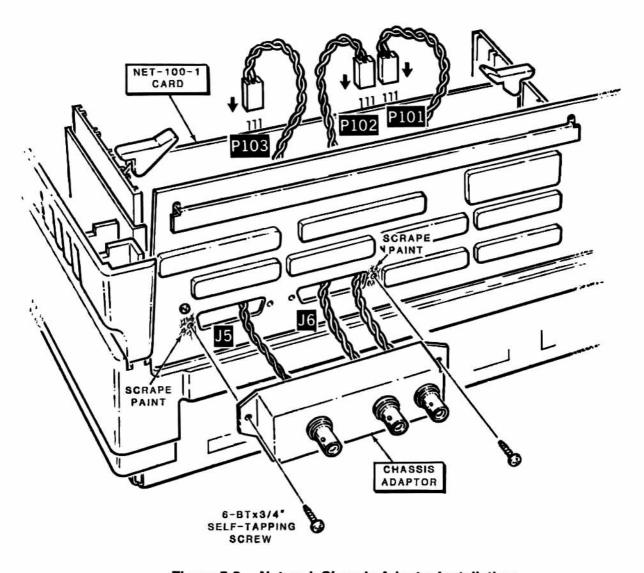

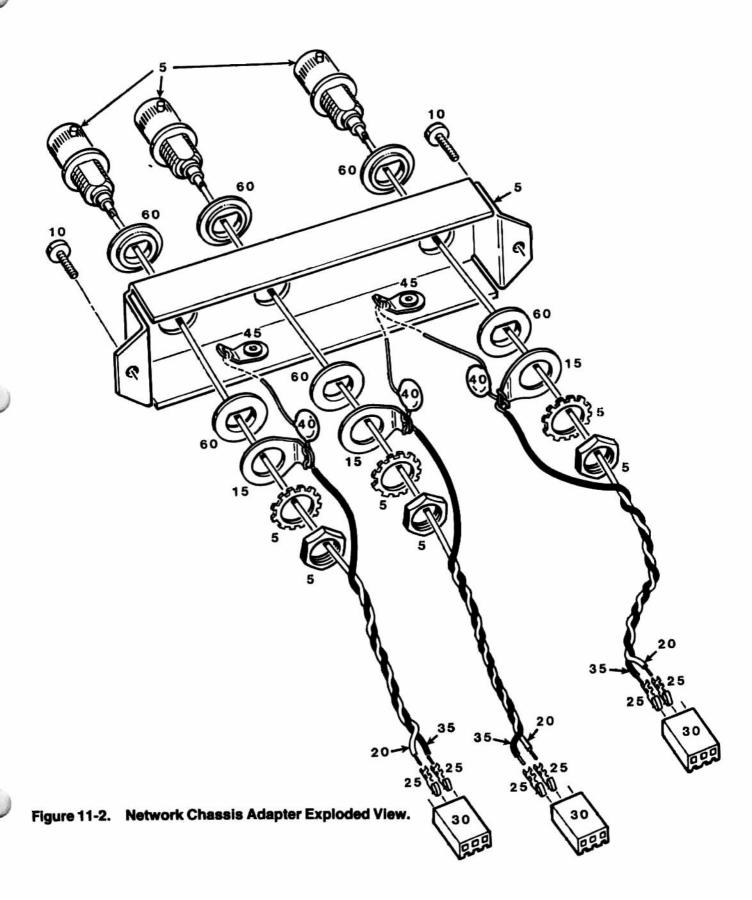

## **Network Chassis Adapter Installation**

Refer to Figure 5-2 and complete the steps below.

Figure 5-2. Network Chassis Adapter Installation

- Choose two of the adjacent unused 25 D-pin connectors on the back panel. We suggest J5 and J6 connectors. Remove the hole plug buttons which cover these holes and discard them.

- Carefully sand or scratch the paint off the back panel from the two outermost screw holes.

- Place chassis adapter over these holes and feed the cables through the holes to the inside of the unit.

- 4. Using two HE 250-1434 (6-BT × .375) self-tapping screws, fasten the chassis adapter to the rear panel.

- 5. Connect the cables fed to the inside of the unit to the NET- 100 board connectors P101, P102, and P103. The connector has three pins, but only two contacts are used. The outer pins contain the same signal and the contact may be installed either way, as long as the middle pin makes contact with the middle connector.

This completes the installation of the network chassis adapter. To connect nodes together, RG62 coaxial cable can be run through ceilings, on floors, or along the walls. For shorter delays and less cabling, keep long runs to a minimum.

**CAUTION:** Since other installations may use similar cable and connectors, be sure the correct connectors and cabling are connected to the Network Chassis Adapter. Damage to this board may result if improper connections are made.

# Chapter 6 Initial Tests

### Introduction

This chapter contains three initial tests to make sure the NET-100-1 Card is properly operating and interfaced to the system. The three tests are RAM, I/O, and Memory.

NOTE: These tests are interrupted by pressing the CTRL and RESET keys simultaneously.

### **RAM Test**

The following is a test routine to determine if the RAM is operating properly. Using a work processor program or EDLIN, enter the following under file RAM.ASM.

| NET_MEM_ADRS  | EQU     | 0F000H                                          |

|---------------|---------|-------------------------------------------------|

|               |         |                                                 |

| DGROUP        | GROUP   | DSEG, STACK                                     |

| CCROUP        | GROUP   | CSEG                                            |

|               | ASSUME  | CS: CGROUP, DS: DGROUP, SS: DGROUP, ES: NOTHING |

| DSEG          | SEGMENT |                                                 |

| DATA_BUFFER_0 | DB      | 0, 0, 0FFH                                      |

| DSEG          | ENDS    |                                                 |

| STSEG         | SEGMENT | STACK                                           |

|               | DB      | 256 DUP (?)                                     |

| STSEG         | ENDS    |                                                 |

| CSEG          | SEGMENT |                                                 |

| INIT_MEMTST:  |         |                                                 |

|               | PUSH    | AX                                              |

|               | PUSH    | BX                                              |

|               | PUSH    | CX                                              |

|               | PUSH    | DX                                              |

|               | MOV     | AX, DGROUP                                      |

|               | MOV     | DS, AX                                          |

| INIT_BUFFER:  |         |                                                 |

|               | VOM     | AX, NET_MENLADRS                                |

|               | MOV     | ES, AX                                          |

|               | MOV     | BX, 0                                           |

|               | MOV     | AL, O                                           |

|               |         |                                                 |

### **Initial Tests**

| LOOP: |      |          |              |

|-------|------|----------|--------------|

|       |      | MOV      | ES: [BX], AL |

|       |      | JMP      | LOOP         |

|       |      | POP      | DX           |

|       |      | POP      | CX           |

|       |      | POP      | BX           |

|       |      | POP      | AX           |

|       |      | RET      |              |

| CSEG  |      | ENDS     |              |

|       |      | END      |              |

| Туре  | MASM | RAM. ASM |              |

| Type  | LINK | RAM      |              |

| Type  | RAM  |          |              |

LED D105 should light while this test is being performed. If LED D105 does not light, refer to Chapter 10, Service Instructions.

### I/O Test

The following is a test routine to determine if the I/O network is operating properly. Using a word processor program or EDLIN, enter the following under file IO.ASM.

| NET_IO_ADRS | EQU     | HOA000                                          |

|-------------|---------|-------------------------------------------------|

| DCROUP      | GROUP   | DSEG, STACK                                     |

| CGROUP      | GROUP   | CSEG                                            |

|             | ASSUME  | CS: CGROUP, DS: DGROUP, SS: DGROUP, ES: NOTHING |

| STSEG       | SEGMENT | STACK                                           |

|             | DB      | 256 DUP (?)                                     |

| STSEG       | ENDS    |                                                 |

| CSEG        | SEGMENT |                                                 |

| INIT_NET:   |         |                                                 |

|             | PUSH    | AX                                              |

|             | PUSH    | BX                                              |

|             | PUSH    | cx                                              |

|             | PUSH    | D <b>X</b>                                      |

|             | MOV     | AX, DGROUP                                      |

|             | MOV     | DS, AX                                          |

|             |         |                                                 |

#### LOOP\_TRANSMIT: LOOP\_TA\_0: DX, NET\_IO\_ADRS MOV IN AL. DX AND AL, 01 CMP AL, 0 JE LOOP\_TA\_0 DX, NET\_IO\_ADRS + 1 MOV MOV AL, 003H JMP LOOP\_TRANSMIT POP DX CX POP BX POP POP AX RET CSEG ENDS END Type MASM IO. ASM Type LINK 10 Type 10

LED D102 should light while this test is being performed. If LED D102 does not light, refer to Chapter 10, Service Instructions.

## **Memory Test**

The purpose of this test is to determine if the RAM and its interface to the system are operating properly. If a difficulty is encountered while this test is being performed, refer to Chapter 10, Service Instructions.

- Turn on the computer and monitor.

- After the prompt type EF000:0 (the monitor will show Examine F000:0) RETURN.

The following should be displayed on the monitor: F000:0000 D1 = **RETURN**

### **Initial Tests**

Now F000:0001 64 = should be displayed, or the ID node number set by SW105 in Hex. This number will differ depending on the ID number your board is set for. **RETURN**

When the memory location is given on the screen, type the number listed below. After every entry hit a carriage return to advance to the next memory location.

| ONSCREEN   | TYPE |

|------------|------|

| F000: 0002 | 1    |

| F000: 0003 | 2    |

| F000: 0004 | 3    |

| F000: 0005 | ų    |

| F000: 0006 | Ś    |

| F000: 0007 | 6    |

| F000:0008  | 1    |

| F000:0009  | 0    |

| F000:000A  | 9    |

| F000:000B  | A    |

| F000: 000C | В    |

| F000:000D  | C    |

| F000:000E  | D    |

| F000: 000F | E    |

| F000: 0010 | E.   |

|            |      |

- Hit the DELETE key to get the prompt back.

- 5 Type DF000: 0-10 RETURN.

The following should be displayed, indicating that the RAM can be written to and read from.

F000: 0000 D1 64 01 02 03 04 05 06 ; 07 08 09 0A 0B 0C 0D 0E F000: 0010 0F

NOTE: F000:0001 should read the ID node number in hex set by SW105.

# Chapter 7 Reassembly

### Introduction

This chapter contains the information required to install the top of the Z-100 Computer after NET-100-1 Card installation, configuration, and tests.

# Reassembly

All-in-One Model — Refer to Figure 7-1. Connect cable (134-1264), if using 8-inch disk drive. Replace the top case by bringing it straight down into its position. Using a small flat blade screwdriver, slide the latches all the way to the front.

This completes the reassembly of the all-in-one model.

Figure 7-1. Reassembly, All-in-One Model

# Reassembly

**Low-Profile Model** — Refer to Figure 7-2. Connect cable (134-1264), if using 8-inch disk drive. Replace the top case by bringing it straight down into its position. Push the latches all the way to the front.

This completes the reassembly of the low-profile model.

Figure 7-2. Reassembly, Low-Profile Model

# Chapter 8 Theory of Operation

## Introduction

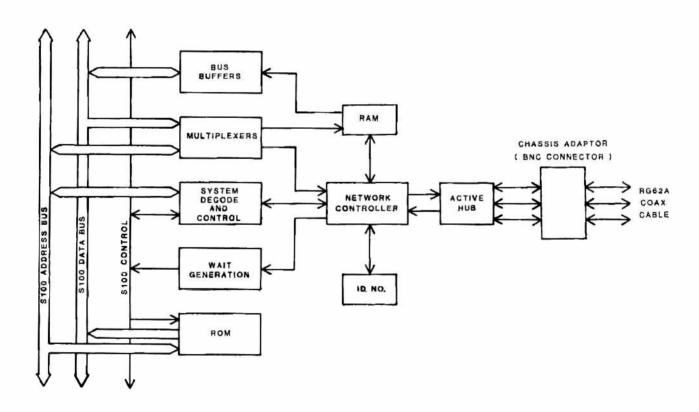

This chapter provides a brief explanation of the theory of operation of the NET-100 Card. If a more detailed theory of operation is desired, refer to Chapter 9, Circuit Description. Refer to the block diagram, Figure 8-1, as you read the following description.

Figure 8-1. NET-100-1 Block Diagram

## Theory of Operation

The NET-100-1 Card is divided into nine main sections.

- Bus Buffers

- Multiplexers

- System Decode and Control

- Wait Generation

- Read Only Memory (ROM)

- Random Access Memory (RAM)

- Network Controller

- ID Number

- Active Hub

The following paragraphs describe each of these sections.

#### **Bus Buffers**

The bus buffers are receivers and drivers for the S-100 address, data, and control signals.

#### Multiplexers (MUX)

The address/data multiplexers pass the 8-bit address onto the internal IAD0-IAD7 bus line to the network controller. The 8-bit data is then passed to the controller in the same way.

#### System Decode and Control

The system decode and control circuits contain all the logic necessary to control memory and I/O accesses, 8 and 16-bit data transfers, interrupts, and phantom assertion.

#### **Wait Generation**

The wait generation circuitry receives the network control wait signal and transforms it to the S-100 ready signal.

#### Read Only Memory (ROM)

The ROM allows the capability of booting in a non-disk environment. The support circuitry provides a 24-bit, switch selectable location in memory (phantom control optional through a jumper). The board does not come equipped with the ROM installed.

#### Random Access Memory (RAM)

The 2K  $\times$  8 RAM can be accessed by both the network controller and the system processor. The RAM location in memory is 24-bit, switch selectable on 2K boundaries.

#### **Network Controller**

The network controller provides the necessary interface between the S-100 Bus and the network. It controls waits, interrupts, and data to and from the system.

#### **ID Number**

The ID number is a unique number from 1 to 255 given to every node (unit) in the network. Physically set by an onboard switch, it serves to identify where a message is generated, where the message is being sent, and the priority that unit has.

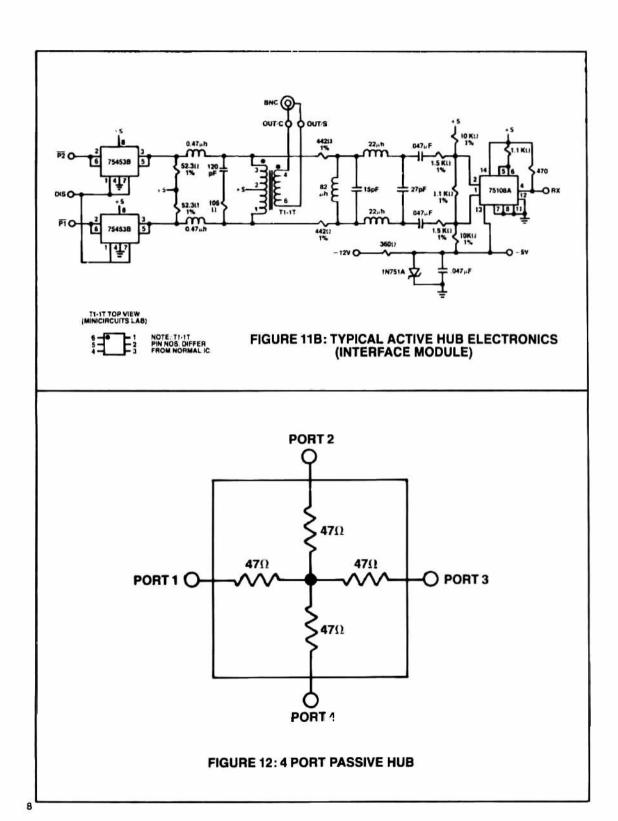

#### **Active Hub**

The active hub decodes and encodes the incoming and outgoing messages. The hub allows implementation of a small network without any external hardware through the available three ports. The fourth port is dedicated to the network controller; no external connection may be made to it.

# Chapter 9 Circuit Description

#### Introduction

This chapter provides a detailed circuit description of the NET-100-1 Card. Refer to the schematic diagrams for the following discussion.

#### **Bus Buffers**

U101, U102, U108, and U111 are the address bus buffers. U103 is the buffer for the data out (DO0-DO7) bus (data received from the S-100 Bus). U104 is a buffer for the data in (DI0-DI7) bus (data going out to the S-100 Bus). U104 is enabled by DBIN and REQ. U108 and U127 are buffers for the control signals.

## **Multiplexers**

The multiplexers U112 and U118 select data transfers between the bus and the RAM or the network controller.

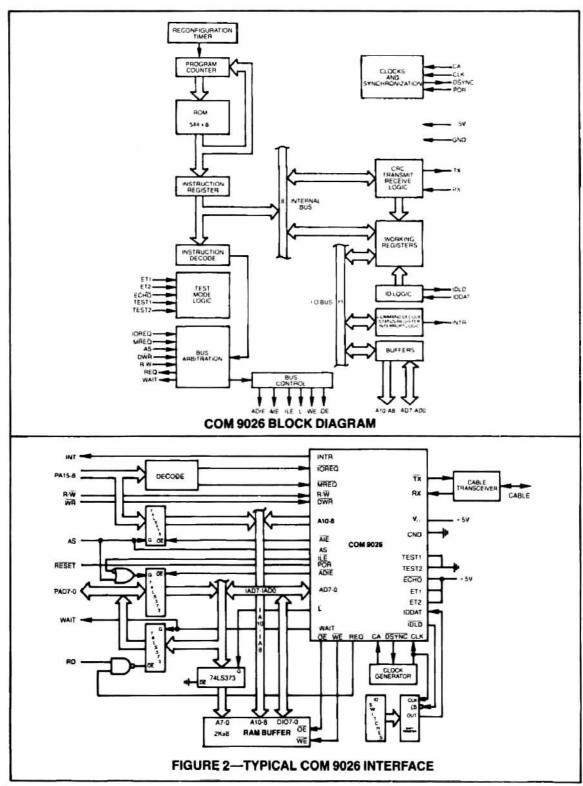

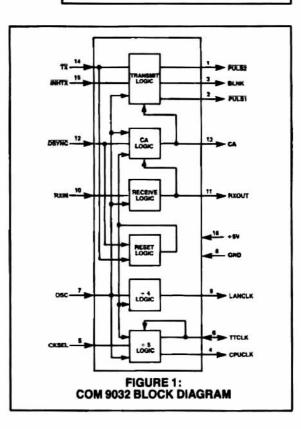

# COM9026 Interface (U116)

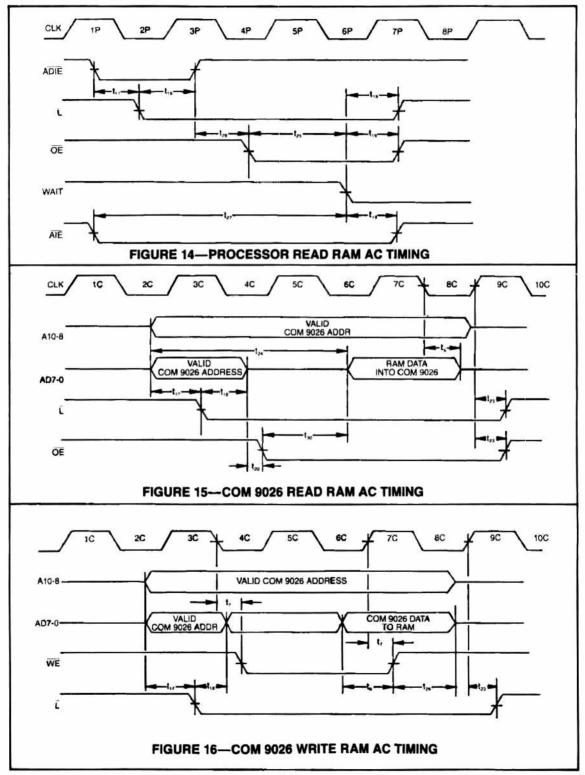

First, output data to U116 through multiplexers U112 and U118 will be discussed. ADIE\* (Address/Data Input Enable) from U116 pulses low, enabling the multiplexers through pin 15. Pin 1 on U112 and U118 are high since ILE\* (Interface Latch Enable) is high. ILE\* determines whether data or address bits are enabled onto the IADO-IAD7 internal bus. While high, ILE\* selects the B inputs (the address lines) of U112 and U118. After the address has been enabled to U116, ILE\* and ADIE\* pulse low, selecting the A inputs of U112 and U118, allowing U116 to latch the data on IADO-IAD7.

An input access for data from U116 is very similar. The address is passed to U116 in the same manner as previously discussed. At this point, U116 outputs its data onto the IAD0-IAD7 bus. U104 then latches the data for output onto the DI0-DI7 S-100 Bus.

## System Decode and Control

The memory access circuitry consists of U101, U105, U111, U134, SW101, and SW106. U105 and U134 are comparators which check the address on the bus, with the address set by SW101 and SW106. If the address checks, the outputs of U105-19 (MEMADRS2\*) and U134-19 (MEMADRS1\*) are low.

#### 16-Bit Addressing

The I/O access circuitry consists of U110, U135, SW103, and SW107. When J105 pins 1 and 2 are jumpered together, the address on the bus is compared with the address set by SW107 and SW103. Listed below are the settings for I/O address switches selecting 00A0H. Note that OFF equates to a logic "1" and ON to a logic "0".

#### SW107

| POSITION    | 0         | 1  | 2   | 3   | 4   | 5   | 6   | 7   |

|-------------|-----------|----|-----|-----|-----|-----|-----|-----|

| ADDRESS BIT | <b>A8</b> | A9 | A10 | A11 | A12 | A13 | A14 | A15 |

| ON/OFF      | ON        | ON | ON  | ON  | ON  | ON  | ON  | ON  |

#### SW103

| POSITION    | 0          | 1  | 2   | 3  | 4  | 5  | 6         | 7  |

|-------------|------------|----|-----|----|----|----|-----------|----|

| ADDRESS BIT | <b>A</b> 7 | A6 | A5  | A4 | A3 | A2 | <b>A1</b> | A0 |

| ONOFF       | OFF        | ON | OFF | ON | ON | ON | ON        | ON |

#### 8-Bit Addressing

When J105 pins 2 and 3 are jumpered, only the address set by SW103 is compared. Although SW107 is not compared, the 8-bit addressing operates similarly to the 16-bit operation.

U107 is a 16L8 Programmable Array Logic (PAL). The PAL generates MREQ\* (pin 13) and IOREQ\* (pin 12) from IOADRS\*, MEMADRS1\* and MEMADRS2\*, as shown by the PAL equations located in Chapter 12. MREQ\* controls LED D105 through buffer U108. When active (low), the LED will light. LED D102 operates the same way, being controlled by IOREQ\*. The S-100 Bus generates AS (Address Strobe) through U107, enabling U116 to sample MREQ\* and IOREQ\*.

#### Interrupt

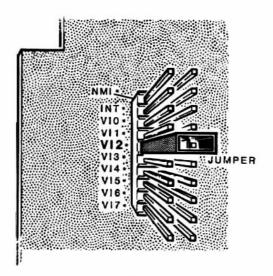

One output from U107 is the INTR\* line, U107-17. When U116 asserts its interrupt line (INTR 9026), U107 will force INTR\* low, causing LED D103 to turn on after being buffered by U138. INTR\* is connected to J101, a series of jumpers (refer to Figure 9-1). For use in the Z-100, VI2\* is jumpered, although it is possible to jumper INT\*, NMI\* and VI0-VI7\*. For the system to operate properly, only one jumper at a time can be used on J101.

Figure 9-1. Interrupt Jumpers

#### **Phantom**

The other two outputs from U107, PHANTOM1\* (pin 18) and PHANTOM2\* (pin 15) are tied together. When MEMADRS1\*, MEMADRS2\* and a write cycle occur, PHANTOM2\* goes low. In this way, the NET-100-1 board maps over ROM (Read Only Memory) space in the main system.

### **Wait Generation**

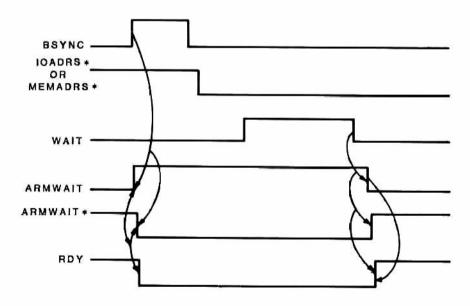

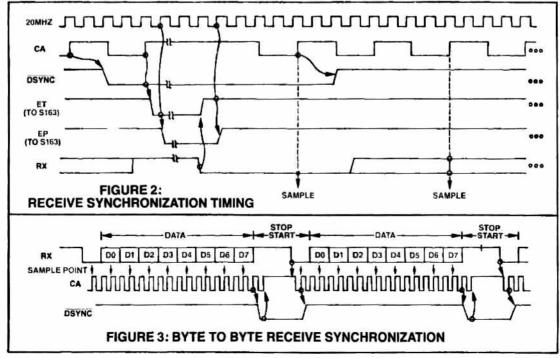

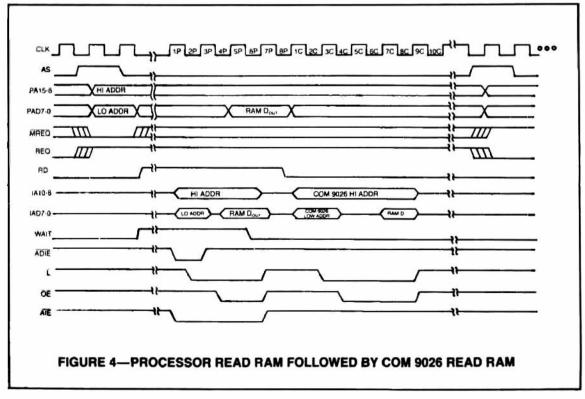

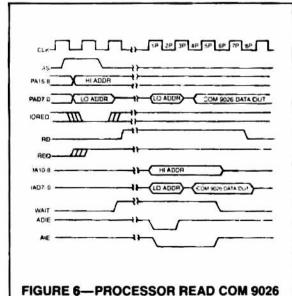

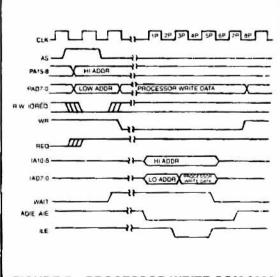

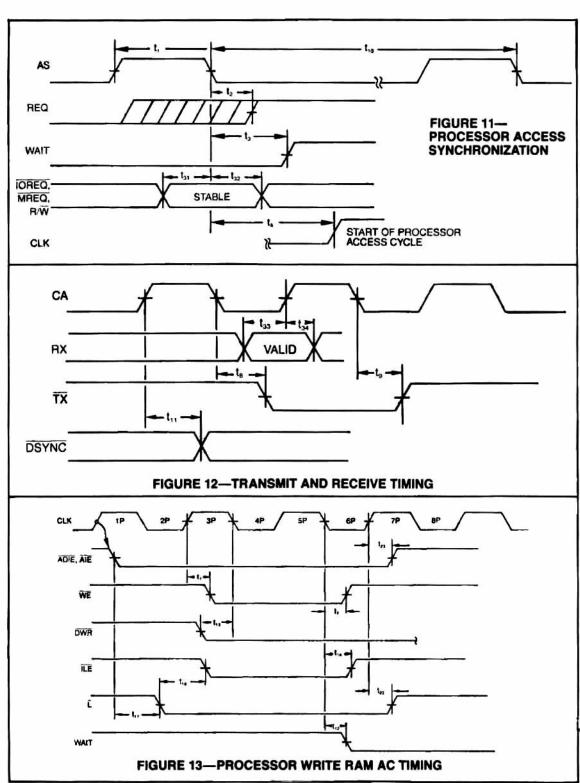

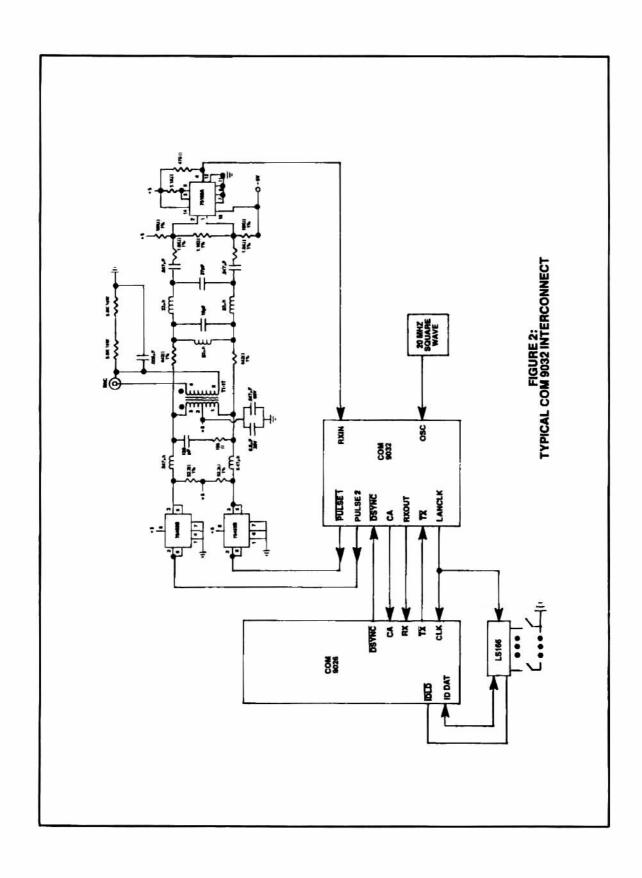

At the beginning of every bus cycle (refer to Figure 9-2), the BSYNC pulse is fed to the preset lines (PR) pins 4 and 10 of flip-flop U139, forcing the Q output (pin 9) high and the Q\* output (pin 8) low. The outputs remain in this state until the clock toggles the low in at U139-2.

Figure 9-2. Timing Diagram

U139-8 (ARMWAIT\*) is connected to U121-8. The other input of the NOR gate (U121-9) is IOADRS\*. The output U121-10 is high if this board and I/O have been selected. When this occurs and bus status line BINP or BOUT (generated by U136-3) is high, U131-3 (RDY) is low, causing wait states to be inserted in that bus cycle until ARMWAIT\* goes high.

U139-9 (ARMWAIT) is connected to U142-13. The other input to this gate is MEMADRS. When both MEMADRS1\* and MEMADRS2\* are low, U121-4 goes high, causing MEMADRS to be selected, and U142-11 to be high. U131-6 (RDY)is low if U142-11 and U131-4 (BINP or BOUT or BMEMR) are high.

In effect, when I/O or memory accesses occur on the NET-100-1 board, RDY is forced low. When U116 is ready, the WAIT signal becomes inactive, going low. WAIT is inverted at U133-11, clocking a low to the D input (pin 12) of U139. U139 is clocked by  $\Phi^*$ , synchronizing WAIT to the S-100 Bus timing. ARMWAIT goes low, forcing RDY high and ending the wait state.

# **ROM Circuitry**

The ROM circuitry is independent from the network controller circuitry. It does not generate any wait states, nor does it rely on the wait states from the network controller to operate properly. After onboard buffering, the ROM circuitry operates as if it were a separate board within the unit.

U106, U108, U109, U130, U131, U133, U136, U140, SW102, and SW104 comprise the circuitry for the ROM (U117). U106 and U130 are comparators which check the address set by SW102 and SW104. When the address at SW102 is the same as that from the address bus, the output U106-19 goes low. U106-19 is connected to the input of U130. If both addresses check, ROMSEL\* goes low, enabling the ROM via U117-20 (CE\*).

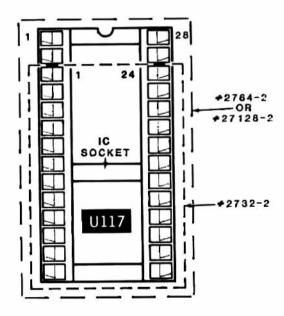

The addresses A0-A12, required for U117, are taken from the buffered address bus. Depending on the memory type used, A13 may also be connected through J115, pins 1 and 2. Figure 9-3 illustrates the ROM insertion for the memory type used and Table 9-1 lists the jumper configuration for the selected ROM.

Figure 9-3. ROM Insertion

Table 9-1. ROM Jumper Configuration

| TYPE    | JUMPER | PINS JUMPERED |

|---------|--------|---------------|

| 2732-2  | J112   | 1,2           |

|         | J113   | 1,2           |

|         | J115   | 2,3           |

| 2764-2  | J112   | 1,2           |

|         | J113   | 2,3           |

|         | J115   | no jumper     |

| 27128-2 | J112   | 2,3           |

|         | J113   | 2,3           |

|         | J115   | 1,2           |

The following switch settings of SW102 and SW104 correspond to address 0F4000H using a 2764 ROM:

#### SW102

| POSITION    | 0   | 1   | 2   | 3   | 4   | 5   | 6   | 7   |

|-------------|-----|-----|-----|-----|-----|-----|-----|-----|

| ADDRESS BIT | A16 | A17 | A18 | A19 | A20 | A21 | A22 | A23 |

| ON/OFF      | OFF | OFF | OFF | OFF | ON  | ON  | ON  | ON  |

#### SW104

| POSITION    | 0  | 1  | 2  | 3  | 4  | 5   | 6   | 7   |

|-------------|----|----|----|----|----|-----|-----|-----|

| ADDRESS BIT | NC | NC | NC | NC | NC | A15 | A14 | A13 |

| ON/OFF      | X  | X  | X  | X  | X  | ON  | OFF | ON  |

When a ROM read occurs from this board (DBIN and MEMR high), U133-3 (OE\*) is low. OE\* will enable the outputs (D0-D7) of U117 to U109. When U136 pins 9 (ROMSEL\*) and 10 (OE\*) are low, U109 pins 1 and 19 are low, allowing data to pass from the ROM to the DI0-DI7 of the S-100 Bus. A ROM read from this board results in ROMSEL and BMEMR being high, and the buffered output of U131, pin 11 being low, causing the LED D104 to light.

U131, an open collector NAND gate, is low when ROMSEL and MEMR go high. J114 is an optional jumper to allow this signal PHANTOM\* to be asserted when the ROM is selected, allowing the ROM to be mapped over existing memory space. When configuring the Z-100, this jumper need not be used.

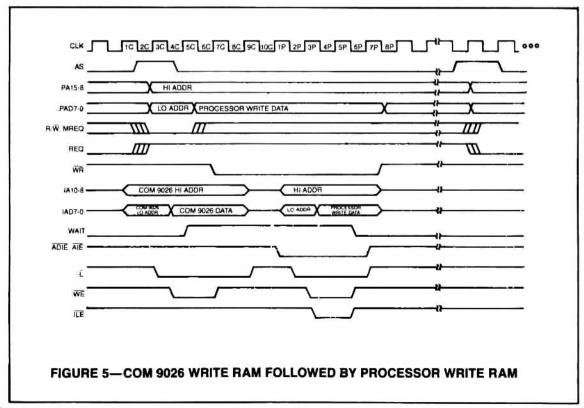

#### **RAM Interface**

U116 controls the timing for any RAM access, whether it is by the network controller or the system processor. When the address set by SW101 and SW106 equates with the address on the bus, the outputs of U105 (MEMADRS2\*) and U134 (MEMADRS1\*) go low. MEMADR1\* and MEMADR2\* outputs in coordination with the other inputs on the U107 (PAL) cause MREQ\* to become active. The following switches are set to select 0F0000H, as used by the Z-100:

#### SW101

| POSITION    | 0   | 1   | 2   | 3   | 4   | 5   | 6   | 7   |

|-------------|-----|-----|-----|-----|-----|-----|-----|-----|

| ADDRESS BIT | A23 | A22 | A21 | A20 | A19 | A18 | A17 | A16 |

| ON/OFF      | ON  | ON  | ON  | ON  | OFF | OFF | OFF | OFF |

#### SW106

| POSITION    | 0   | 1   | 2   | 3   | 4   | 5  | 6  | 7  |

|-------------|-----|-----|-----|-----|-----|----|----|----|

| ADDRESS BIT | A15 | A14 | A13 | A12 | A11 | NC | NC | NC |

| ON/OFF      | ON  | ON  | ON  | ON  | ON  | X  | X  | X  |

After U116 receives MREQ\*, it generates latch (L\*), an active low pulse, enabling U122 to transfer the stable address on the internal IAD0-IAD7 bus to the RAM (U115). For a write cycle, U116 pulses ILE\* low, enabling data to be multiplexed to the IAD0-IAD7 bus. WE\* generated by U116 allows the latched data to be stored in U115. For a read cycle, the RAM sends data to the system processor or the network controller via the IAD0-IAD7 bus after U116 generates the OE\* pulse to the RAM.

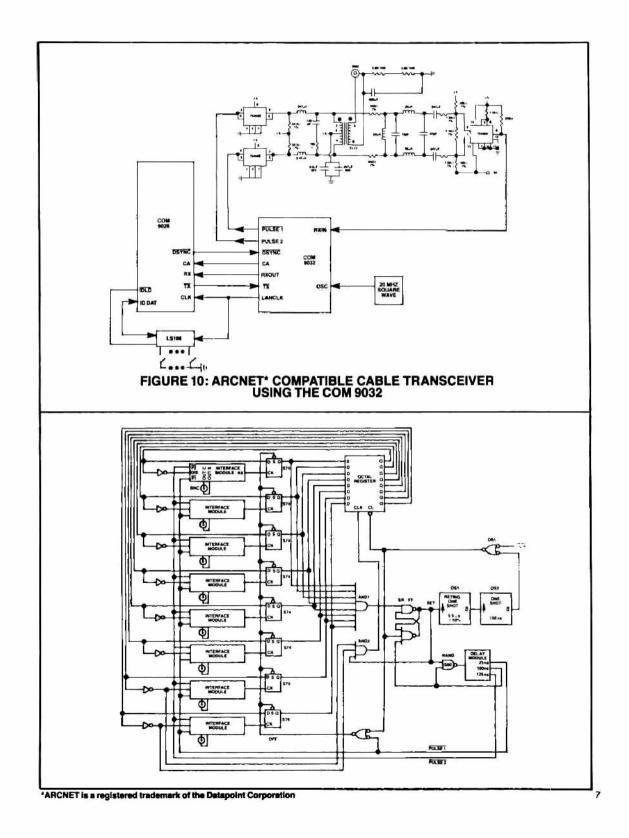

#### **Network Controller**

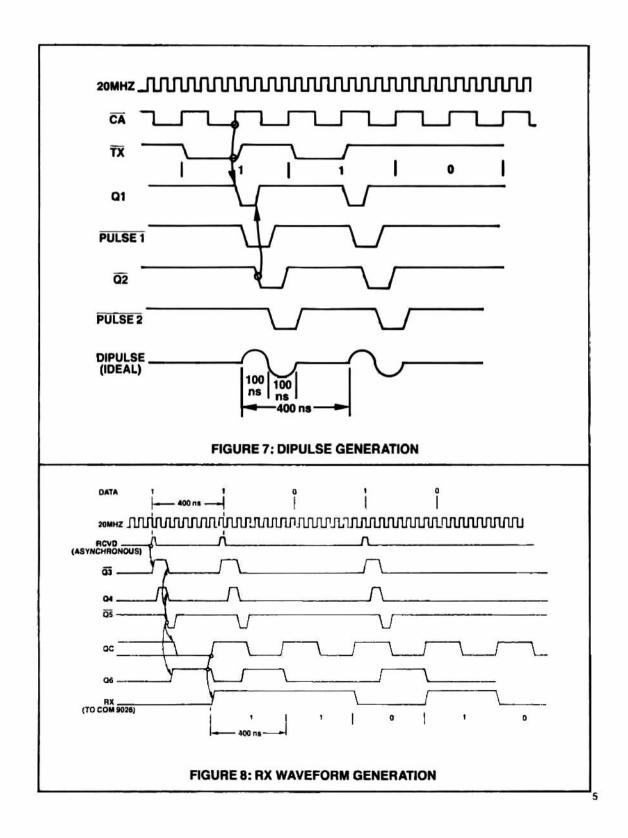

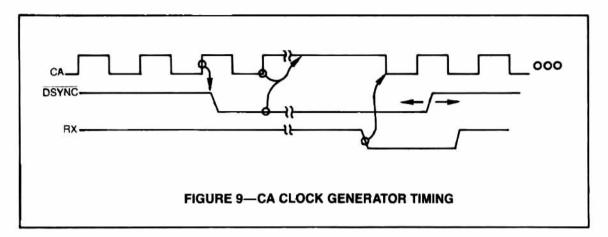

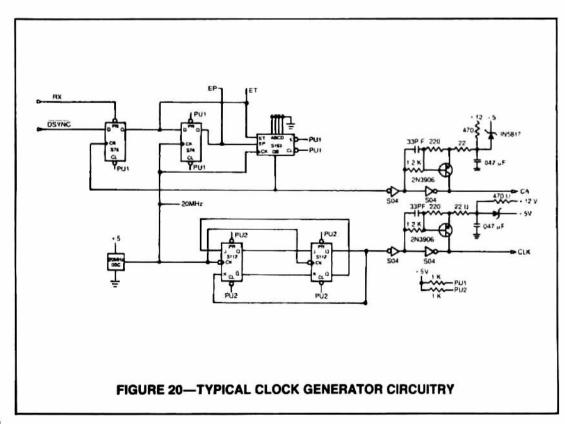

The network controller circuitry consists of U116, U123, and U124 (20 MHz oscillator). The network controller circuitry operates at a 2.5M bit data rate and works under a token passing scheme by passing an invitation to transmit to the next active ID number. U116 is the Local Area Network Controller (LANC) and U123 is the Local Area Network Transceiver (LANT). Together they provide the interface between the system and the network.

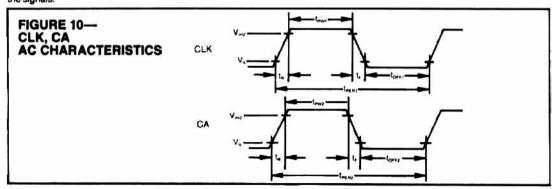

U124 provides the clock signal necessary for U123 to generate CA and CLK (pins 13 and 9) for U116 (pins 2 and 19). CLK is also used by U132 to clock the ID number to U116.

U123 also serves as an interface between the incoming/outgoing pulses on the interface modules (IM101 through IM103), and RX and TX\* on U116. TX\* (U116-37) is converted by U123 to PULS2\*. Incoming signals (RXIN) are converted by U123 to RXOUT, which is connected to RX on the U116-38.

#### **ID Number**

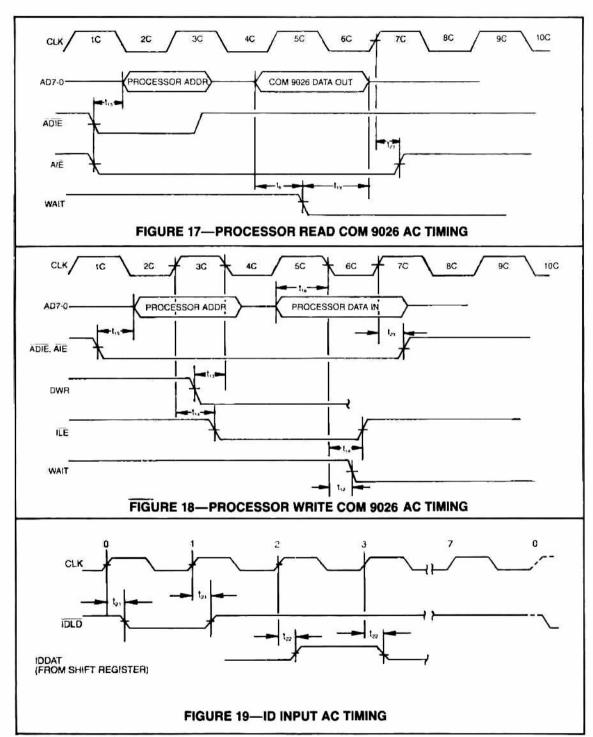

When power or a keyboard reset is applied to the system, U116 reads the ID number from U132. The hardware is capable of selecting an ID number from 1 to 255, which is physically set by the user by SW105. The ID number is present at the parallel inputs of U132, pins 2, 3, 4, 5, 10, 11, 12, and 14. When U116 sends IDLD\* (ID Load) and CLK to U132, the chip outputs the data in serial form, to U116-34, IDDAT (ID Data In). U116 stores the ID number in RAM location 01H. (The specific location in the Z-100 is F000:01H.)

The following switch setting designates ID number 100 (64H).

SW105

POSITION 0 1 2 3 4 5 6 7 ON/OFF ON OFF OFF ON ON OFF ON ON

#### **Active Hub**

At initial power up of the system, U125-9 is momentarily held low by the RC network (R101 and C134) for 0.22 seconds. After being gated through U125, U141, and U142, this signal becomes PRSFF\*. PRSFF\* initializes the flip-flops (U120 and U129) so that the Q outputs are high and remain in that state until data from the network or this board pulses in a low at a D input.

Power up clears U119, initializing all of the Q outputs low. The Q outputs are the D inputs to U120 and U129 and remain low until a data pulse toggles one output high.

For example, assume the onboard port is the first to transmit. PULS2\* from U123-1 is applied to U129-11 through inverter U140-4.

The low at U129-12 is clocked through to U119-13 (D4) and U128-3, putting a low (this will occur if any of the D inputs to U119 are low) at U142-3. This causes U125-11 to go high. U125-11 feeds four inputs: U137-12, U125-5, U128-9, and U128-2.

Remember that at this point, the Q outputs of U119 are still low, causing U141, pins 8, 10, and 12 to be high. These three high inputs to the AND gate (U128) cause the output to go high and provide U119 the required positive-edged clock. Q1, Q2, and Q3 of U119 remain high since the flip-flops have not toggled. The low at D4 is clocked through, causing Q4 to go low.

U137-9 (IDLE\*) goes low 4.9 usec after a high is applied to U137-12. U137 is a one-shot whose timing is determined by R111 and C151.

IDLE\* enables U127, which turns on the LED whose line is active. When no signal is present, U137-9 is high and the diodes (LED's) are unlit. In this case Q4 is low, therefore D109 will light. If one of the other ports is transmitting, the corresponding LED will light.

U137-10 is high at the same time as IDLE\*, and causes U137-7 to go low after a time determined by R112 and C123 when IDLE becomes inactive (EOT). This signal is named EOT\* and stands for End of Time. It is called this since a low on EOT\* causes PRSFF\* to reset the flip-flops in the same manner a power on of the system did.

U125-5 starts the pulse generation through the delay line (U126). The high on U125-5 is inverted and sent to U126-1. U126-12 (P1\*) then goes low, and is connected to P1\* of the interface modules. P2\* goes low after P1\*, and is connected to P2\* of the interface modules. The interface modules generate the dipulse to the coax.

U126-6 goes low after the original input. U125 inverts the signal and U126-1, P1\* and P2\* go high, limiting their pulse widths to 100 nsecs. Note that P2\* is inverted at U140-6 and connected to U123-10 (RXIN). U123 then generates RXOUT to U116. RXOUT is used for both U116 and the other three port network transmissions.

The Q outputs (either Q1, Q2, or Q3) of U119 are inverted by U141, and tied to the DIS/EN\* lines (pin 19 of IM101-IM103). When the signal is high, the interface module is disabled and when low, it is enabled.

Initially, all the DIS/EN\* lines are low, enabling the interface modules to receive data from the network. A high on the DIS/EN\* line prevents the interface modules from retransmitting and disturbing any incoming data.

The hybrid interface modules provide interface to the coax cable (RG62). Pin 11 connects to the shield and 12 to the center of the coax cable. The shield is not tied to logic or chassis ground, but is AC coupled to chassis ground at the back panel through the chassis adapter box. Pins 6 and 3 of the interface modules are connected to +5V and -5V power supplies. Pin 7 (RX) is the incoming signal which is tied to the clock line on the flip-flops U120, pins 11 and 3, and U129, pin 3.

# Chapter 10 Service Instructions

## Introduction

This chapter contains information to assist in servicing and troubleshooting.

Check the jumpers and switches to be sure the NET-100-1 Card is configured properly. If these settings are all correct and the trouble is still present, refer to Table 10-1.

# **Troubleshooting**

Table 10-1 lists some problems you may encounter and some possible causes.

Table 10-1. Troubleshooting

| PROBLEM                                                   | POSSIBLE CAUSE                                                                                            |

|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| System fails to operate.                                  | Be sure the card is fully seated in the card connector.                                                   |

|                                                           | <ol><li>Be sure line cord is plugged in.</li></ol>                                                        |

|                                                           | <ol><li>Check all jumpers.</li></ol>                                                                      |

|                                                           | 4. Check all switches.                                                                                    |

|                                                           | <ol><li>Inspect all I.C. packages for proper seating in sockets.</li></ol>                                |

| Card fails RAMTEST (LED D105)                             | <ol> <li>Check SW101 and SW106 for correct selection.</li> </ol>                                          |

|                                                           | <ol><li>Check MREQ* signal out of U107. If present U108,</li></ol>                                        |

|                                                           | D105; otherwise U116, U111, U101, U134, U105, U107.                                                       |

| Card fails IOTEST (LED D102).                             | Check SW107 and SW103 for correct settings.                                                               |

|                                                           | <ol><li>Check IOREQ* signal out of U107. If present U140,<br/>D102; otherwise U135, U110, U107.</li></ol> |

| Card fails MEMORY TEST.                                   | 1. U102, U103, U104, U112, U118, U122, U132, U138, U115.                                                  |

| Interrupt LED D103 does not light when INTR* is asserted. | 1. U138, D103.                                                                                            |

(Continued...)

# Service Instructions

Table 10-1. Troubleshooting (continued...)

| PROBLEM                                               | POSSIBLE CAUSE                                                                                                                                                   |

|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ROM LED D104 does not light when ROM is being mapped. | <ol> <li>Check for correct settings on SW102 and SW104.</li> <li>Check ROMSEL* signal out of U130. If present U140, U131, D104; otherwise U106, U130.</li> </ol> |

| ROM inoperative.                                      | 1. U108, U133, U136, U109, U117.                                                                                                                                 |

| RDY signal not generated.                             | . U133, U139, U121, U136, U140, U142, U131, U116.                                                                                                                |

| All ports inoperable.                                 | U116, U123, U124, U125, U142, U129, U119, U128,<br>U141, U126.                                                                                                   |

| Ports 1, 2, and 3 inoperable.                         | 1. U111, U119, U137.                                                                                                                                             |

| Onboard port inoperable.<br>(LED D109 not lit)        | 1. U123, U140, U129, U128, U119, U127, D109.                                                                                                                     |

| Port 3 inoperable.<br>(LED D108 not lit)              | <ol> <li>Bad coax. IM103, U141, U120, U128, U119, U127,<br/>D108.</li> </ol>                                                                                     |

| Port 2 inoperable.<br>(LED D107 not lit)              | <ol> <li>Bad coax. IM102, U141, U129, U128, U119, U127,<br/>D107.</li> </ol>                                                                                     |

| Port 1 inoperable.<br>(LED D106 not lit)              | 1. Bad coax. IM101, U141, U119, U27, D106.                                                                                                                       |

| EMI emissions                                         | <ol> <li>Bad ground between network interface and S-100.</li> </ol>                                                                                              |

# Chapter 11 Parts List

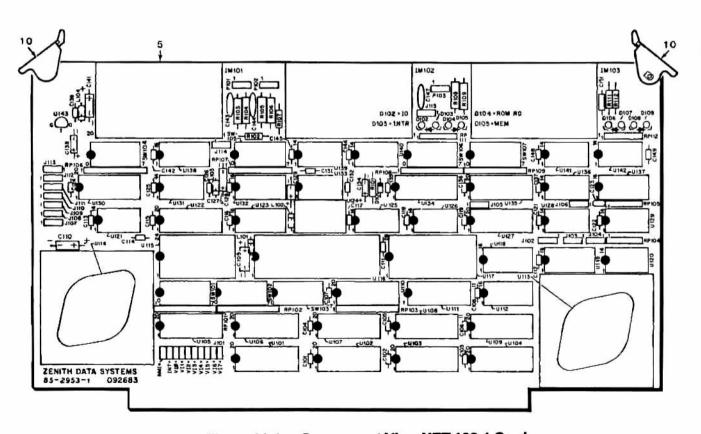

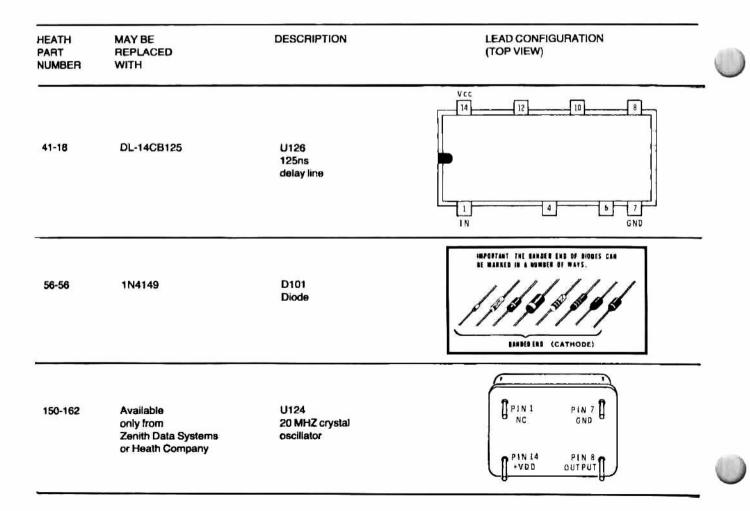

## Introduction

This chapter includes a component view of the NET-100-1 Card and an exploded view of the Network Chassis Adapter to assist in the identification for replacement parts. Adjacent to the circuit reference designator or exploded view number are the part number and description which must be supplied when ordering a replacement part.

## **Replacement Parts**

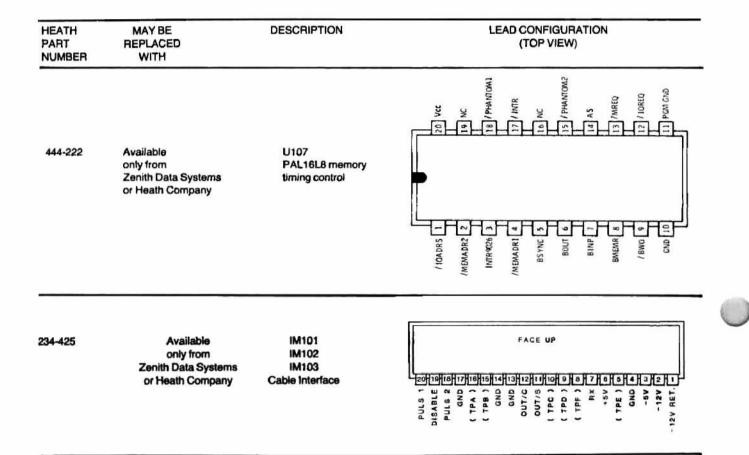

#### **NET-100-1 Network Card**

The NET-100-1 Card is Part Number 181-4638-1. Refer to Figure 11-1 to identify replacement parts.

**CAUTION:** This board contains ESDS (Electrostatic Sensitive devices). Exercise extreme care in handling these devices to prevent damage.

**NOTE:** Refer to the Semiconductor Identification section of this chapter, or Chapter 12, Data Sheets, for description of semiconductor devices.

Figure 11-1. Component View NET 100-1 Card

| CIRCUIT<br>REFERENCE<br>DESIGNATOR | ZDS<br>PART NO.        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CIRCUIT<br>REFERENCE<br>DESIGNATOR | ZDS<br>PART NO. | DESCRIPTION     |

|------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------|-----------------|

| Capacitors                         |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | C141                               | HE 25-195       | 2.2 μF tantalum |

|                                    |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | C142                               | HE 21-769       | .01 μF ceramic  |

| C101                               | HE 21-769              | .01 μF ceramic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | C143                               | Not Used        |                 |