# The S-100 BUS Handbook

DAVE BURSKY

### THE S-100 BUS HANDBOOK

### THE S-100 BUS HANDBOOK

#### **DAVE BURSKY**

#### Dedication

I would like to thank the many friends that helped me to complete this book. Many thanks to Jeff Bierman and Robert Meehan for some of the photographs, and to Katherine Berger, Clare Bursky, and Hilary Mendelson for their typing and proofreading. I am also grateful for the encouragement of others too numerous to name.

Additionally, I would like to thank the many manufacturers that loaned various pieces of S-100 bus equipment to me for use in preparing the book. Some of the many companies include: AP Products, Advanced Micro Devices, Ball Brothers Research, Circuit Stik (now part of Bishop Graphics), Continental Specialties, E & L Instruments, EMM Semiconductor, Extensys Corp., Intel Corp., MITS (now part of Pertec Computer Corp.), Motorola, National Semiconductor, NEC Microcomputers, Oliver Audio Engineering, Seals Electronics, Shugart, Solid-State Music (now called SSM), Southwest Technical Products, Technical Design Labs (now called Xitan Corp.), Texas Instruments, Triple I Corp., Vector Electronics, and Vector Graphic Corp.

Library of Congress Cataloging in Publication Data

Bursky, Dave.

The S-100 bus handbook.

Includes index.

1. Microcomputers. 2. Microcomputers-Buses.

I. Title.

TK7888.3.B84

621.3819'58'3

79-26153

ISBN 0-8104-0897-X

Copyright © 1980 by HAYDEN BOOK COMPANY, INC. All rights reserved. No part of this book may be reprinted, or reproduced, or utilized in any form or by any electronic, mechanical, or other means, now known or hereafter invented, including photocopying and recording, or in any information storage and retrieval system, without permission in writing from the Publisher.

Printed in the United States of America

1 2 3 4 5 6 7 8 9 PRINTING

### **Preface**

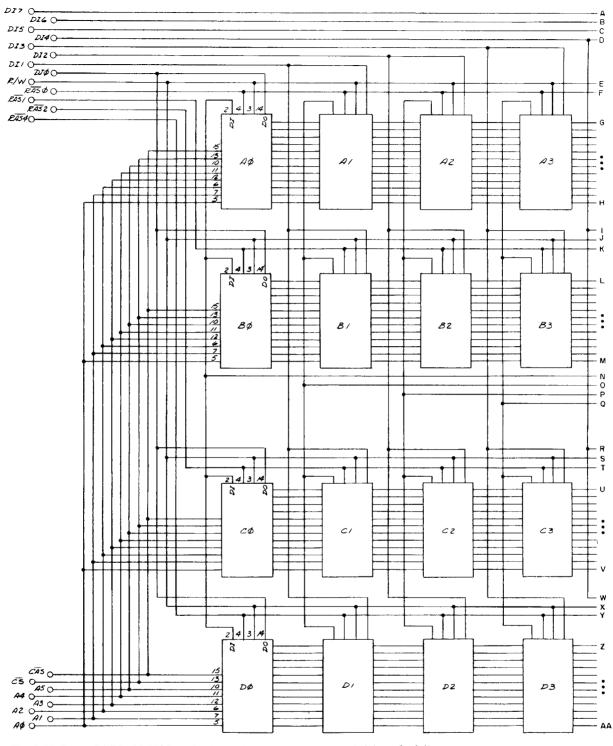

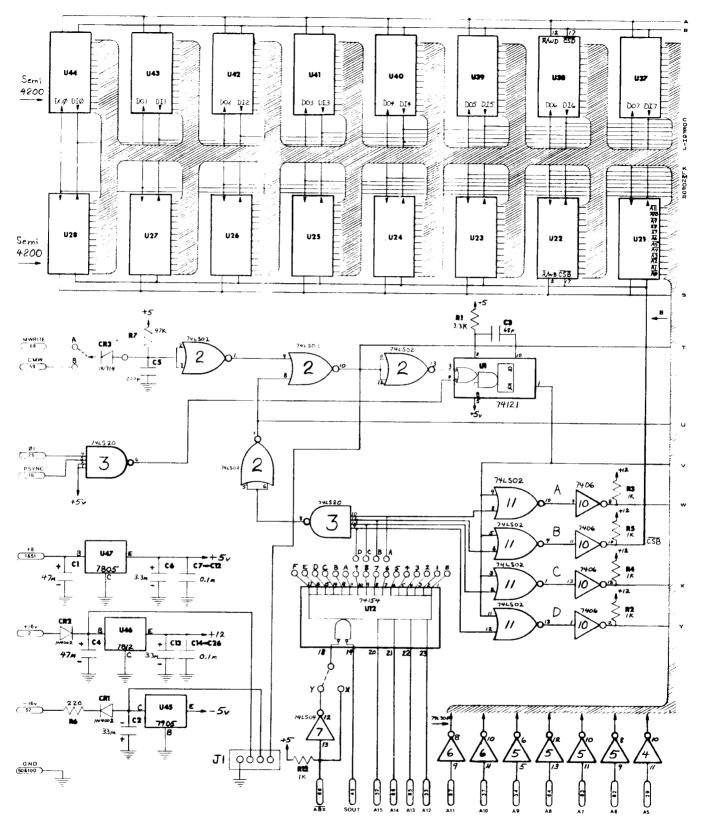

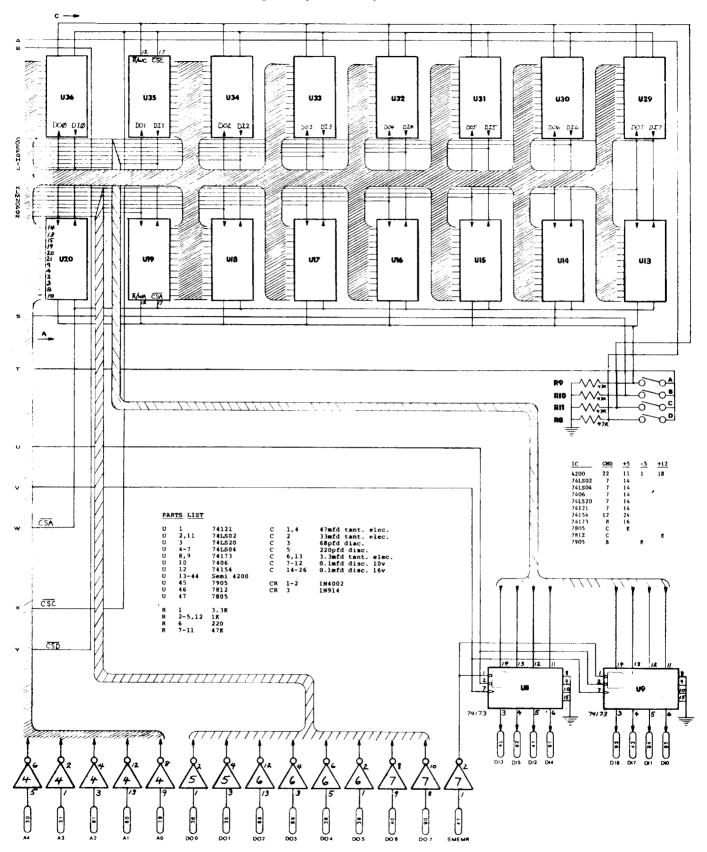

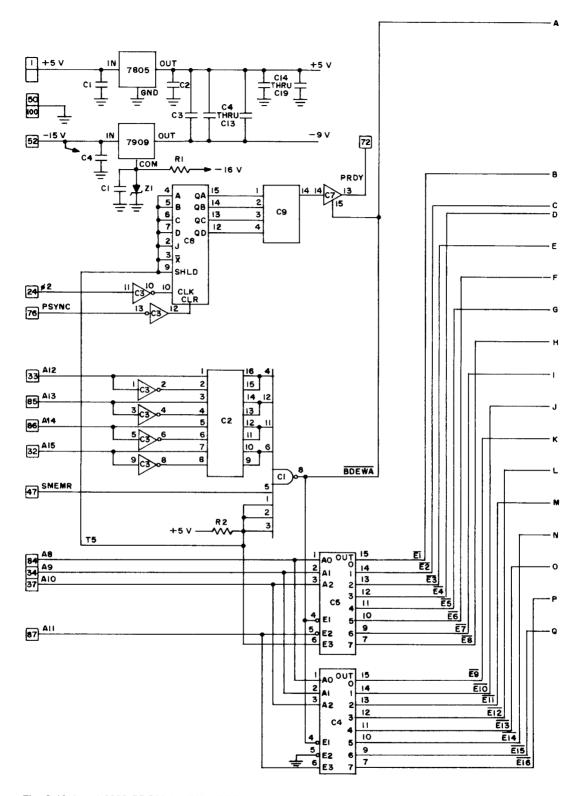

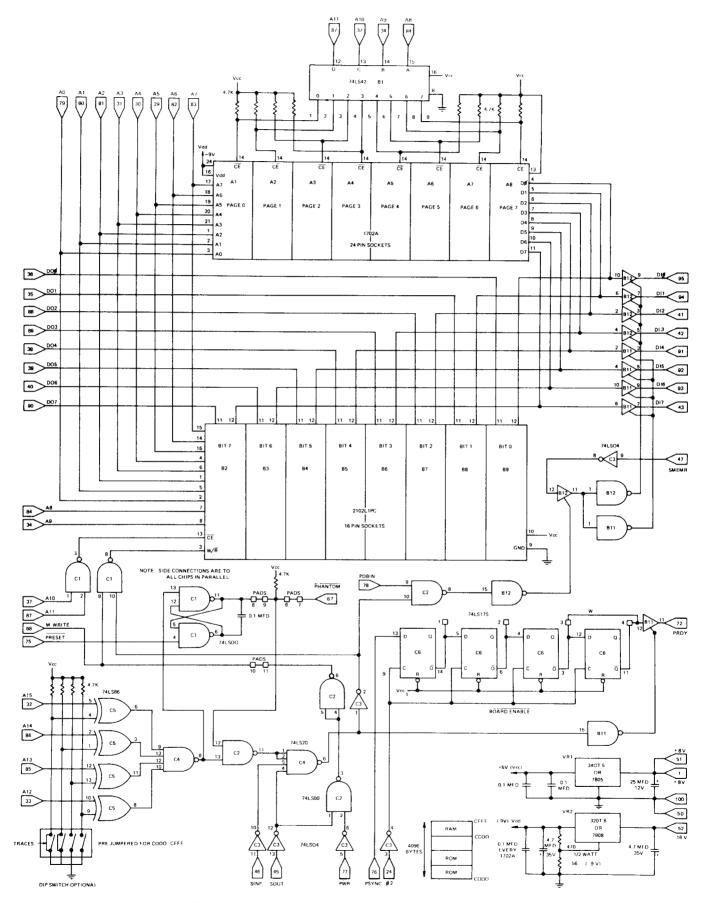

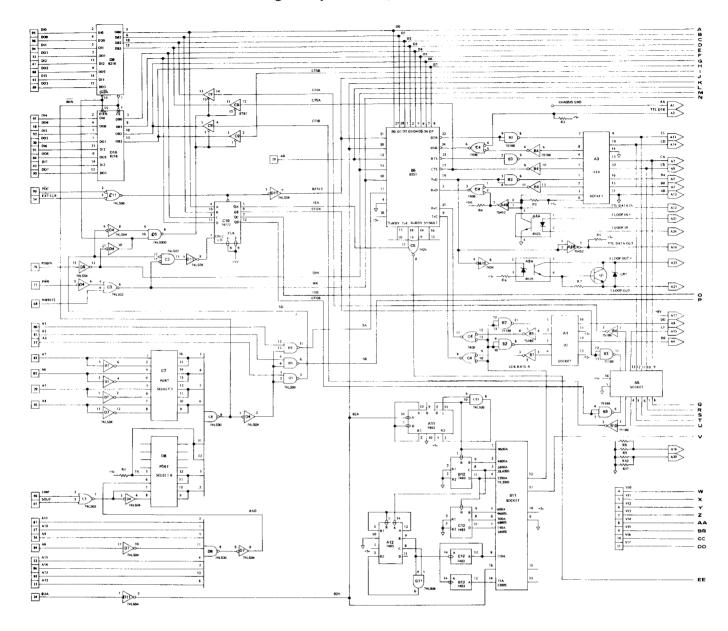

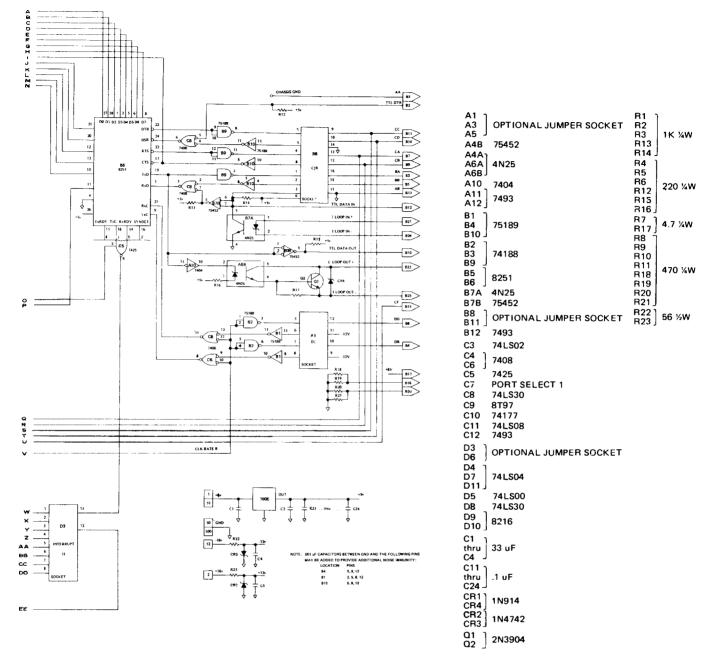

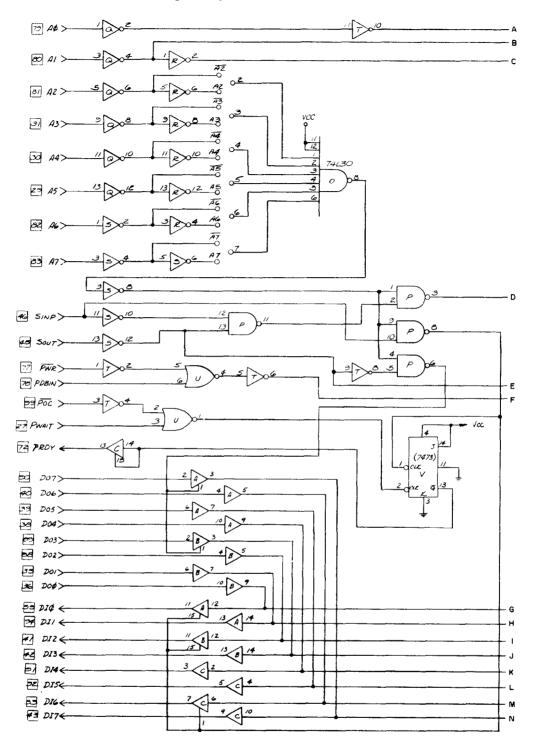

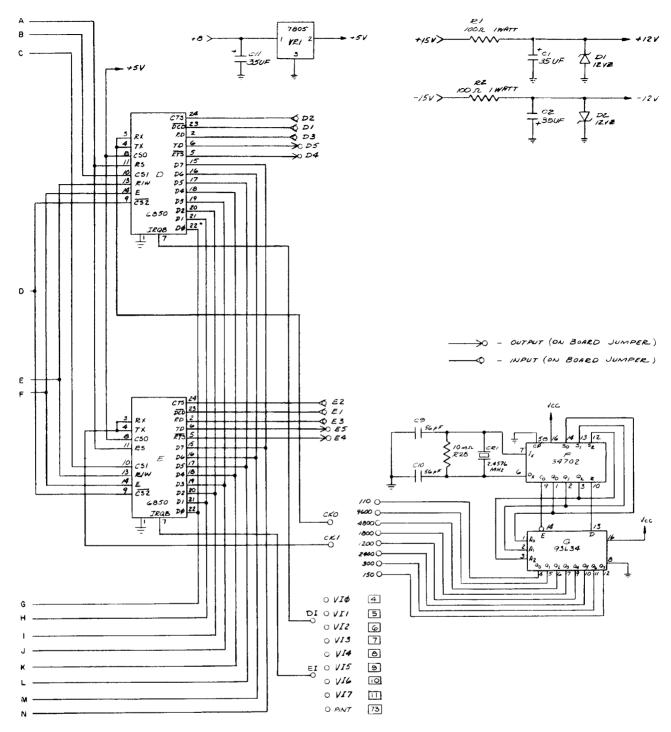

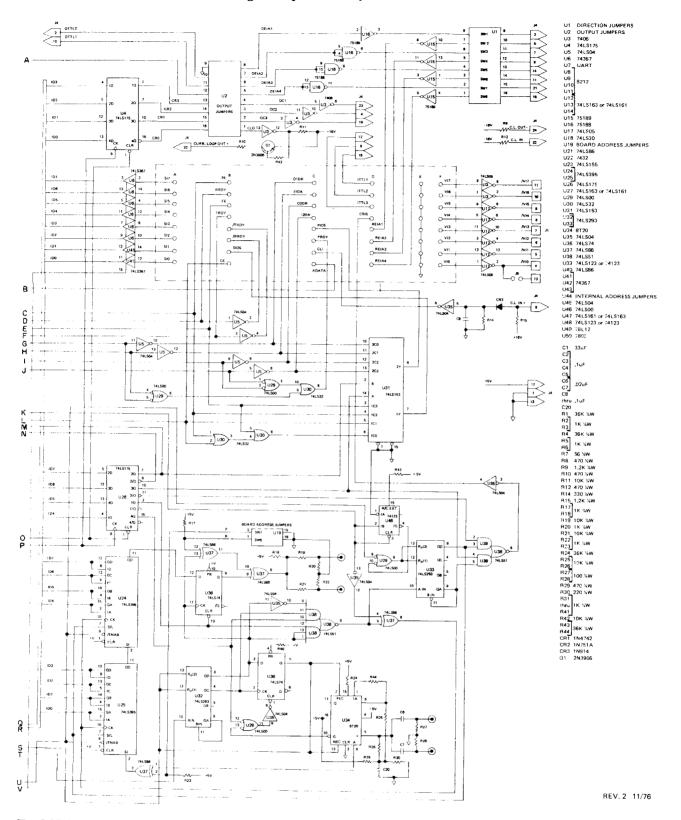

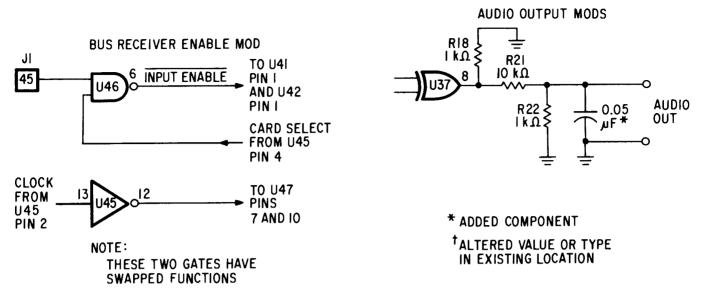

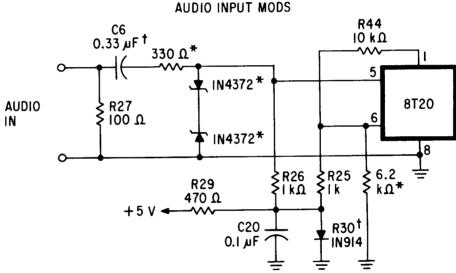

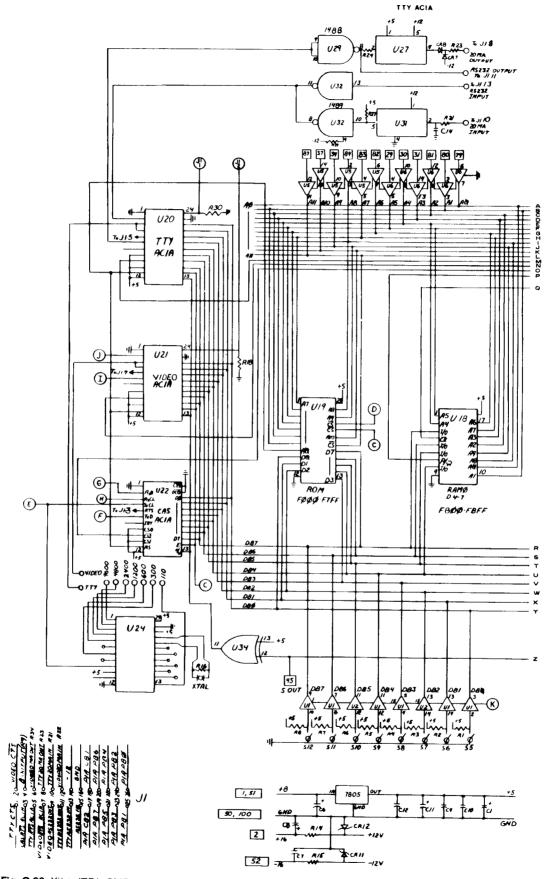

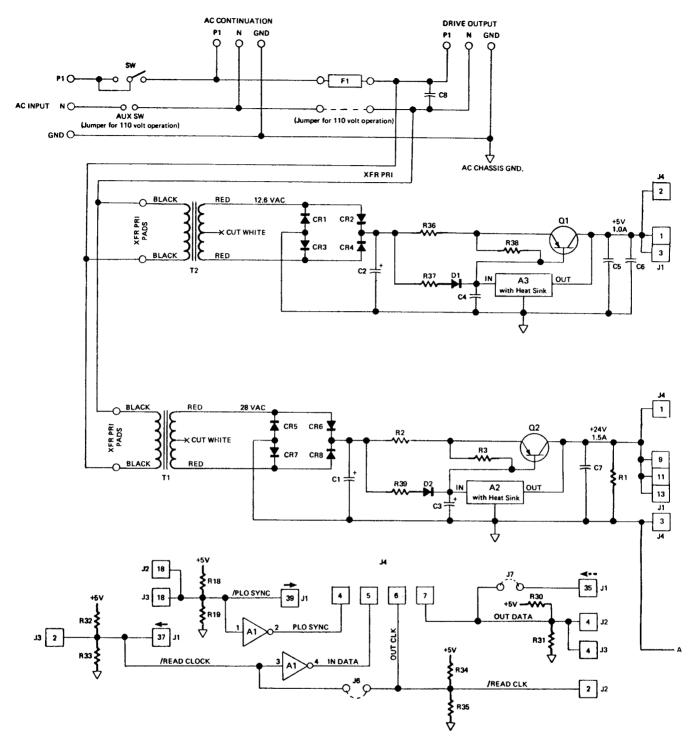

The material in this book has been put together from the many operating manuals and system descriptions published by the various manufacturers mentioned in this book. And, in many cases, the complete latest schematic revision of the particular board described has been included for handy reference. In total, this book is intended to serve as a quick, handy compendium of technical information about S-100 bus equipment. And, although some companies have changed names, been acquired by others, or closed their doors, many thousands of their boards are in the field, and this book will be one of the few places that data will be available.

The boards covered in this book span a wide range of functions, and although it would be impossible to cover every manufacturer's product in a single book, the equipment described here is representative of the many other products that are available. Companies such as MITS and IMSAI were the pioneers in the field of "personal" computing, which has now opened up to an extremely large assortment of low-cost completely assembled systems, some using the S-100 bus and others using proprietary bus structures.

However, another controversy covered in this book is that of just what is the S-100 bus. MITS introduced the original version of it on their Altair 8800 microcomputer system, revised it for the 8800b system and then developed an entirely new structure. The pin definitions picked by Imsai were very similar to those of MITS, but there were some differences—differences that make some of the boards that operate in one system incompatible on the other system. For future S-100 bus systems, many of the incompatibility problems should be eliminated as the "standard" for S-100 bus systems that has been developed by a committee of IEEE (Institute of Electrical and Electronic Engineers) becomes widely adopted. Included in Appendix D is a summary of the new standard, including a listing of all the pins and their definitions.

Not only will this book serve as a handy compendium of information about the boards, but it will serve as a simple guide to troubleshooting some of the basic simple system failures beyond "it doesn't work." Detailed troubleshooting information would require a book on each type of board, so the material included here will just help track down the problem to a defective board, system component, or program.

I would just like to add a word of thanks to all the microcomputer manufacturers that helped me put this material together and hope that for you, the user, it serves its intended purpose.

DAVE BURSKY

### **Contents**

| 1. Basic Introduction to Computers and Microprocessors                                                                                                                                                                                                                | 1  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| A Little Computer Prehistory 1 What Is a Computer? 4 What Is a Microprocessor? 6 The Microprocessor Operates in Cycles 9                                                                                                                                              |    |

| 2. Binary Mathematics and Boolean Algebra                                                                                                                                                                                                                             | 11 |

| Computer Math: A Quick Review 11 Nondecimal Numbering Systems 12 Doing Math with Binary Numbers 13 Using Logic Operators 14 Combining Logic Operators 15 The Basic Rules of Boolean Algebra 16                                                                        |    |

| 3. Introductory Electronics and Logic Functions                                                                                                                                                                                                                       | 17 |

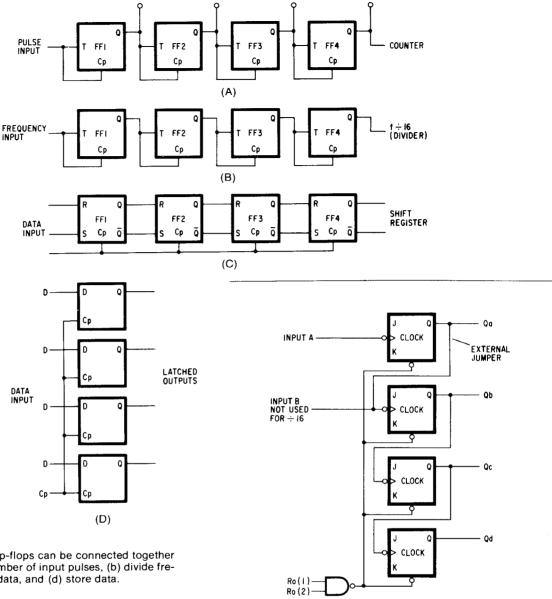

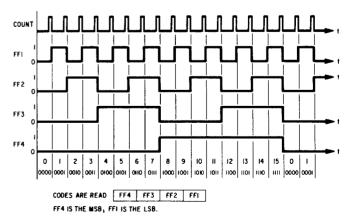

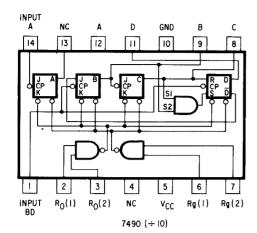

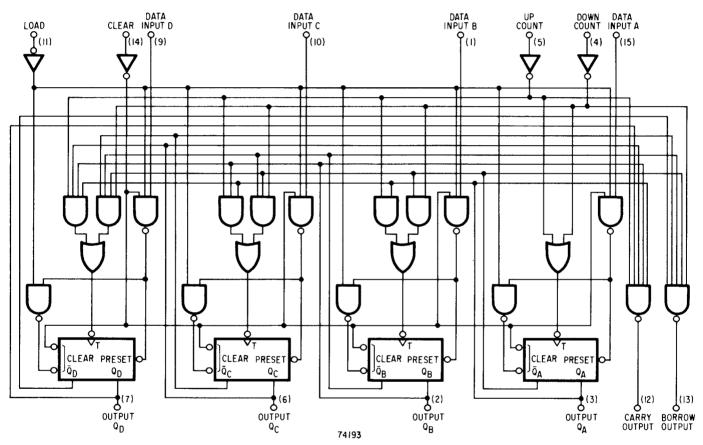

| Let's Look at the Components 18 The Basics of Solid-State Technology 19 Transistors: Semiconductor Control Elements 20 The Integrated Circuit 23 More Complex Circuits 23 Cascaded Flip-Flops Count 27                                                                |    |

| 4. The Basic S-100 Bus and the Computer Mainframe                                                                                                                                                                                                                     | 33 |

| Control and Signal Lines Hold the System Together 37<br>The CPU Works like This 38                                                                                                                                                                                    |    |

| 5. Computer Memory Systems                                                                                                                                                                                                                                            | 40 |

| The Random-Access Memory: What Is It? 40 Start with the Static Memories 42 ROMs: ICs That Remember 45 The PROMs Are Programmed like This 49 Design the Board That Remembers 50                                                                                        |    |

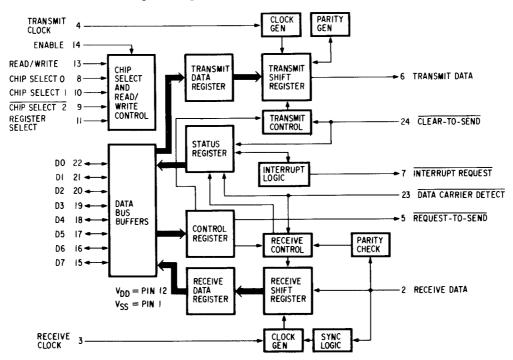

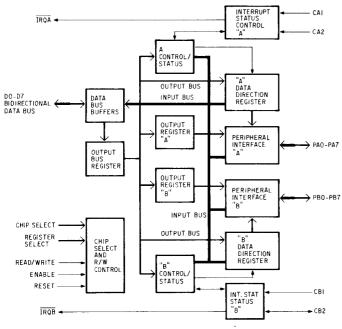

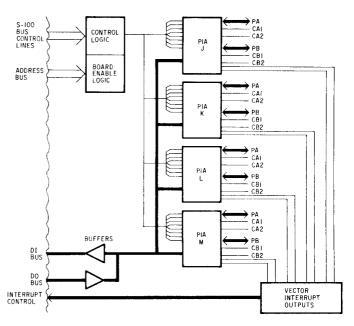

| 6. Input/Output Interfaces for the S-100 Bus                                                                                                                                                                                                                          | 54 |

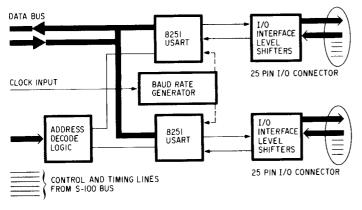

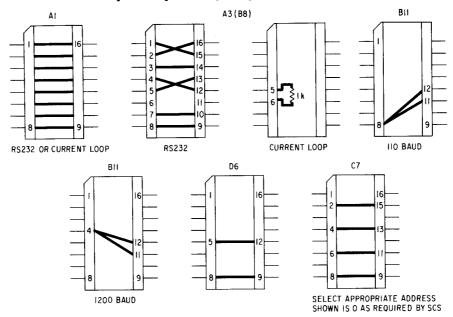

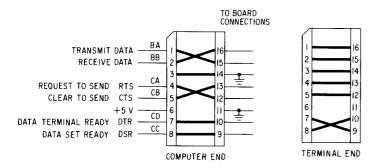

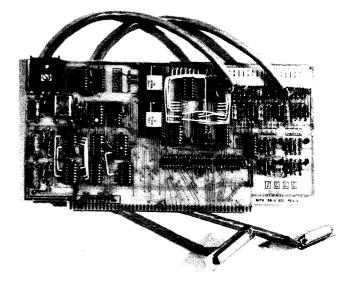

| Study the 8251 Before Using Board 57 Get the Board Up and Running 58 Another Path to the Same End 61 Status Information Is Important Too 63 Don't Want Serial? Go Parallel 64 Combine Functions onto a Single Board 68 Other Designs Provide Different Performance 69 |    |

| 7. Pe  | eripheral Storage Devices for Microcomputer Systems                                                                                                                                                                                                                                                                                                                                                                                         | 71  |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|        | Storing Your Programs—Which Way to Go? 71 Boost Data Entry and Storage Speed with Cassettes 73 Using the Cassette Interface 75 Control the Recorder with the Computer 78 Consider the Kansas City Standard 79 Get Larger Storage Capability with a Floppy 86 Printer Control Signals Are Important 89                                                                                                                                       |     |

| 8. Pr  | rogramming the 8080 CPU in the S-100 Bus Microcomputer                                                                                                                                                                                                                                                                                                                                                                                      | 91  |

|        | Start by Flowcharting the Problem 92 Get to Know the 8080A Programming Model 93 Condition Bits in the 8080A Tell You Its Secrets 95 Examine the 8080A Instruction Set Carefully 95 Write Your Programs Systematically 102 Organize Your Work Carefully When Writing Programs 105 Use Software from Others to Write Your Own 107 Pseudo Operations Add Flexibility to the Assembler 109 Now That You Have BASIC, What Do You Do With It? 121 |     |

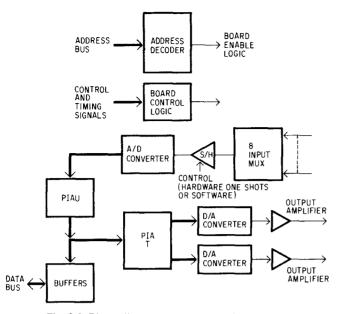

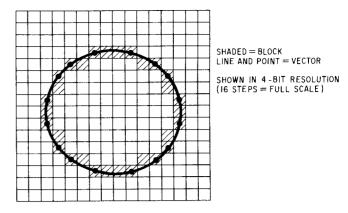

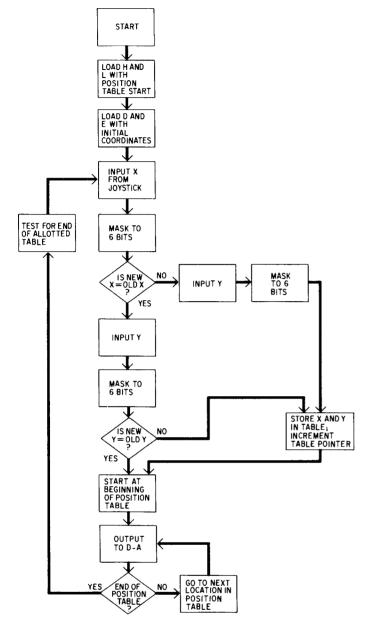

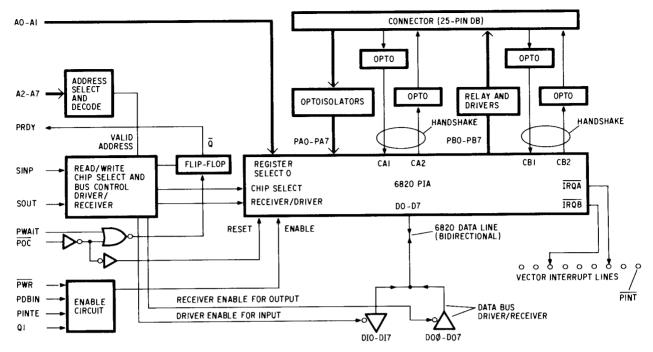

| 9. In  | terfacing the Microcomputer to Real-World Applications                                                                                                                                                                                                                                                                                                                                                                                      | 122 |

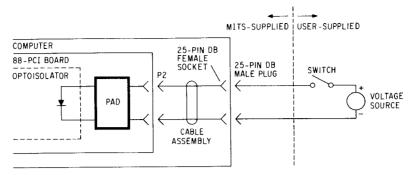

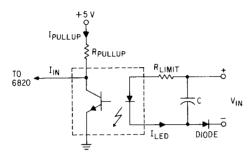

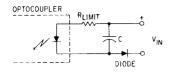

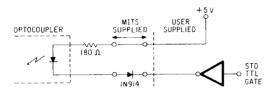

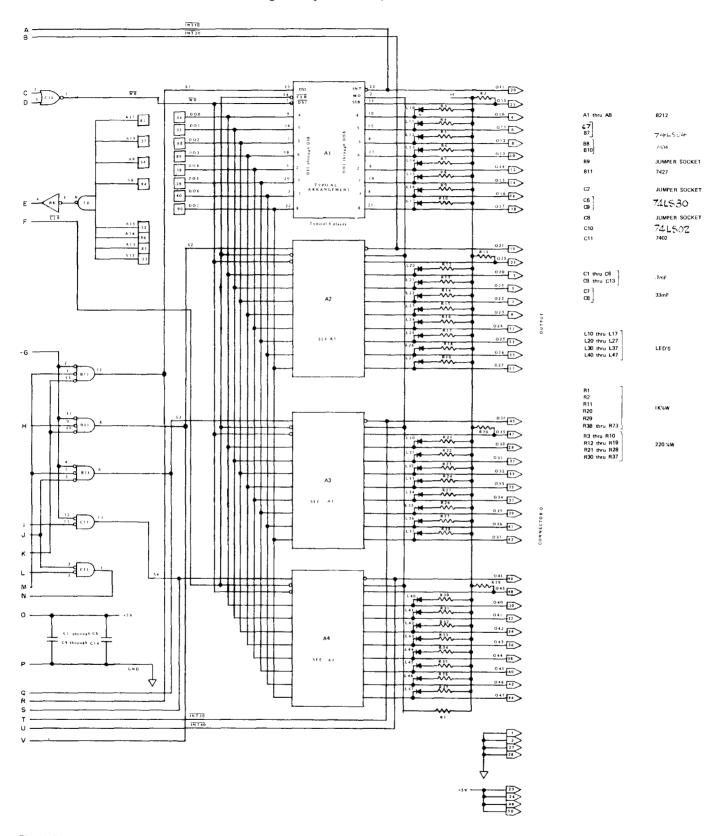

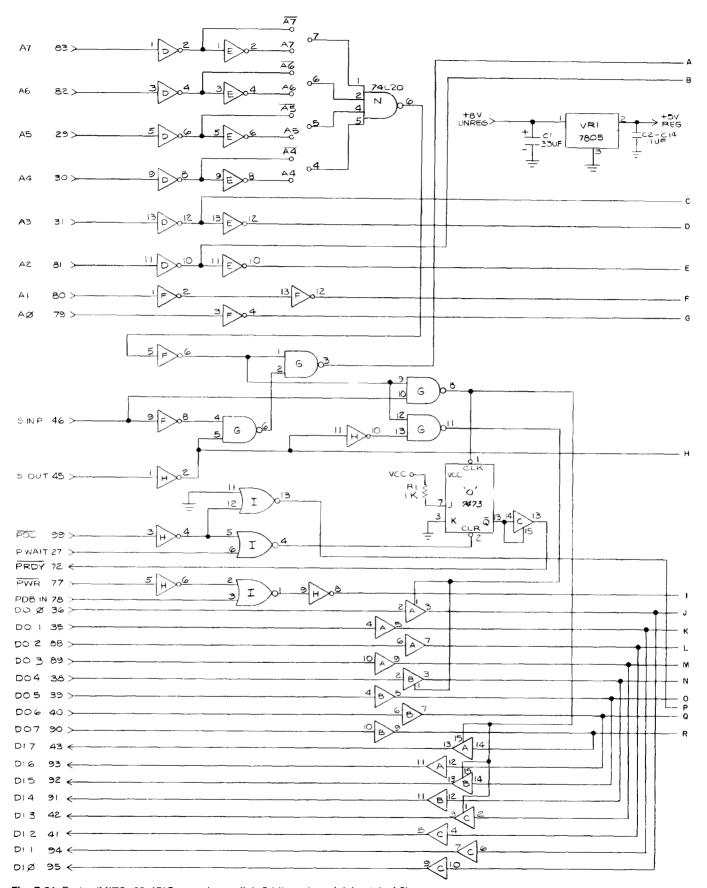

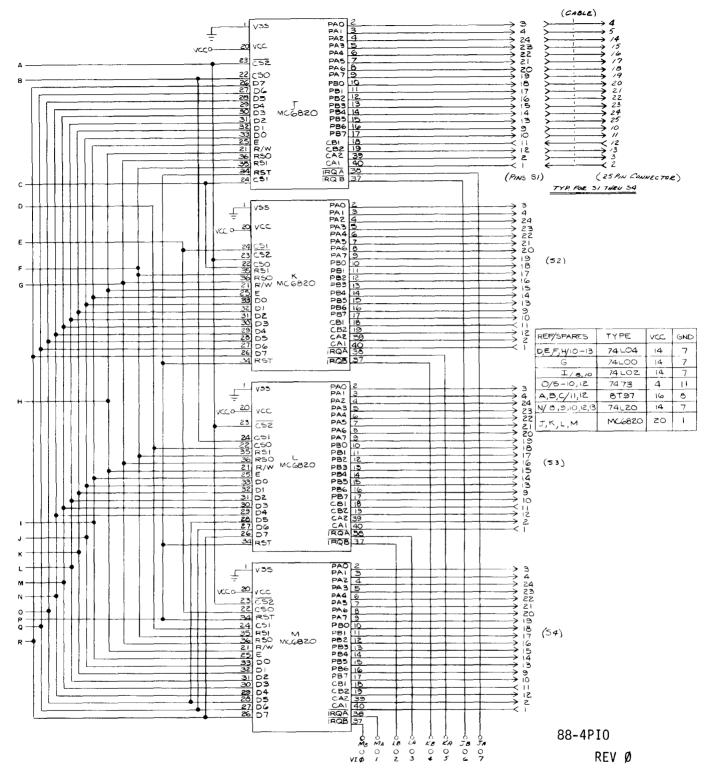

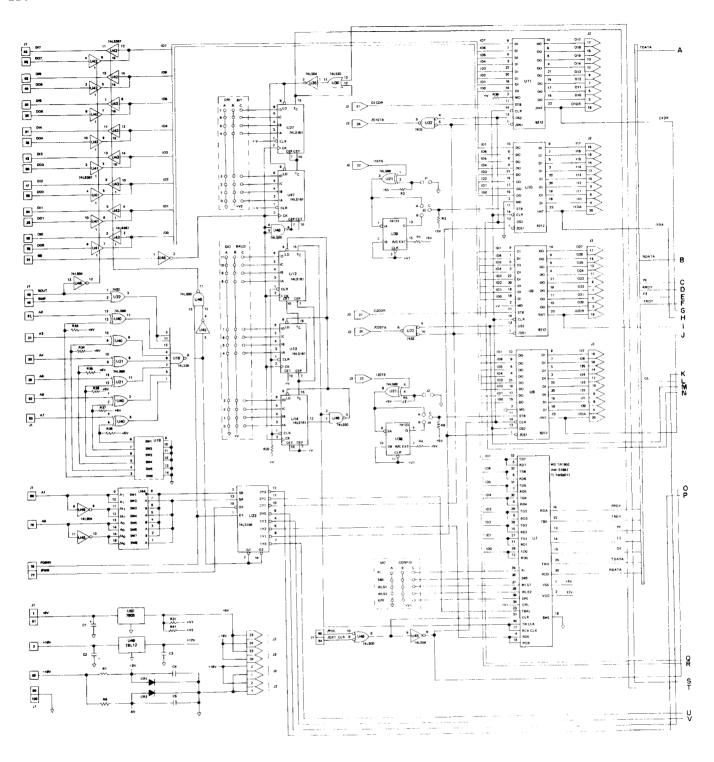

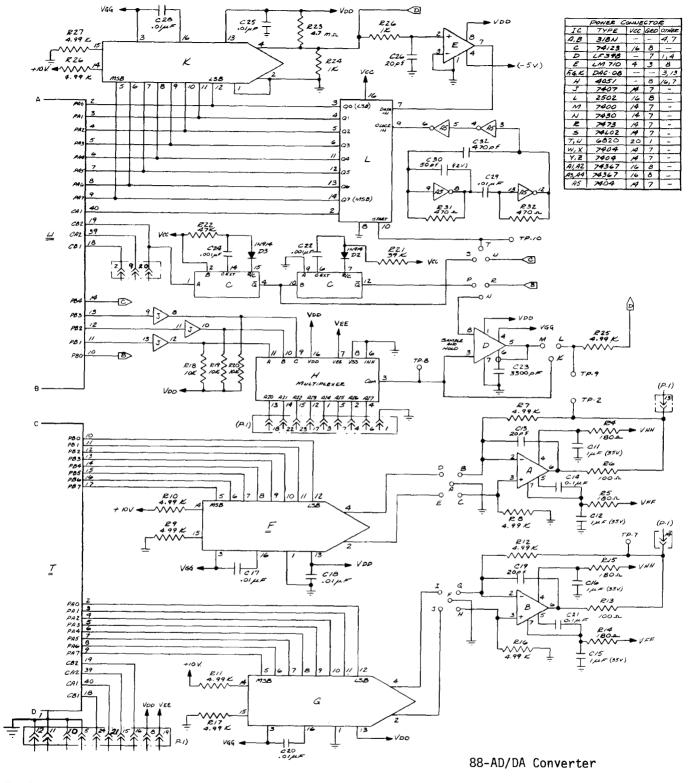

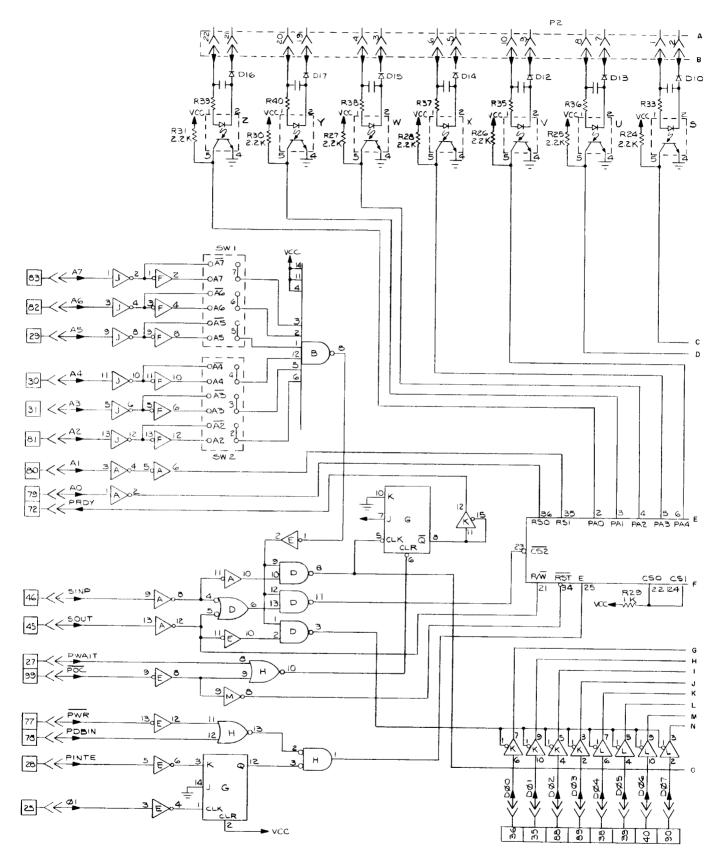

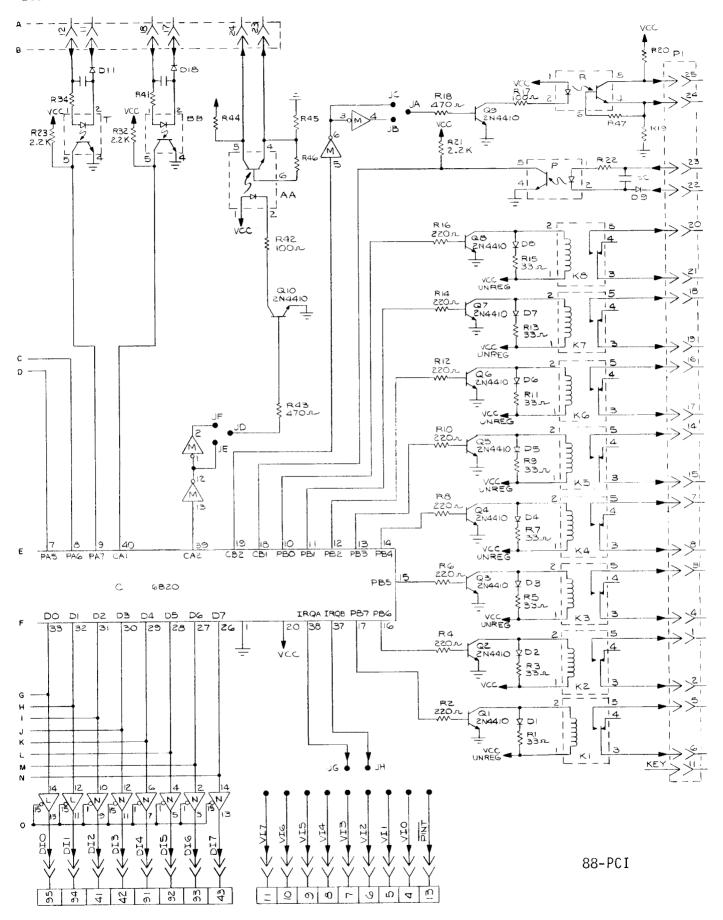

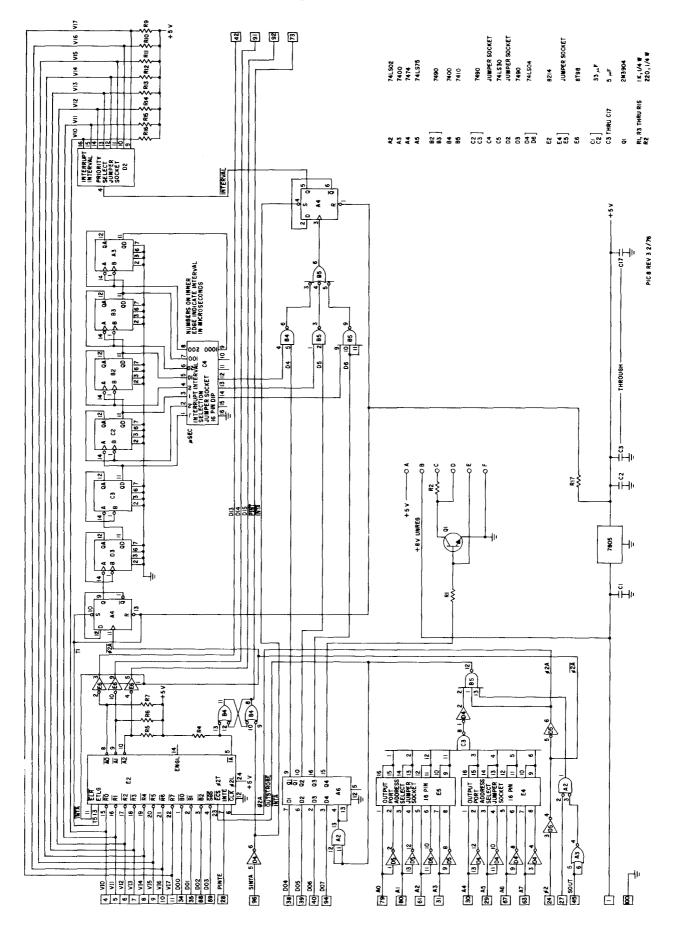

|        | Bring Analog Signals into the Digital World 122 Provide Control for Large Loads 127 Get to Know the 88-PCI Board Options 130                                                                                                                                                                                                                                                                                                                |     |

| 10. Tr | oubleshooting the Microcomputer System                                                                                                                                                                                                                                                                                                                                                                                                      | 139 |

|        | Decide on the Level of Repair You'll Handle 139<br>Check the Memory with Software 140<br>Software Bugs: Gremlins That Can Drive You Crazy 144                                                                                                                                                                                                                                                                                               |     |

| APPE   | NDIX A. Reference Books and Publications                                                                                                                                                                                                                                                                                                                                                                                                    | 149 |

|        | Basic Electronics and Integrated Circuits 149 Programming 149 Microprocessors 150 Advanced Digital Theory and Computer Architecture 150 Troubleshooting 150 Publications 150                                                                                                                                                                                                                                                                |     |

| APPE   | NDIX B. Commonly Used Components and Suppliers of S-100 Bus Systems                                                                                                                                                                                                                                                                                                                                                                         | 152 |

|        | Low-Power Schottky TTL 152 4000 Series CMOS 153 Microprocessor Manufacturers 154 S-100 Computer and Board Manufacturers 156 Printers 157 CRT Terminals 157 Printing Terminals 157 Breadboarding and Cabinets 157                                                                                                                                                                                                                            |     |

PROM Erasers 157

Floppy Disk Drive and Controller Manufacturers 157

Supplementary Products 158

Component and Surplus Dealers 158

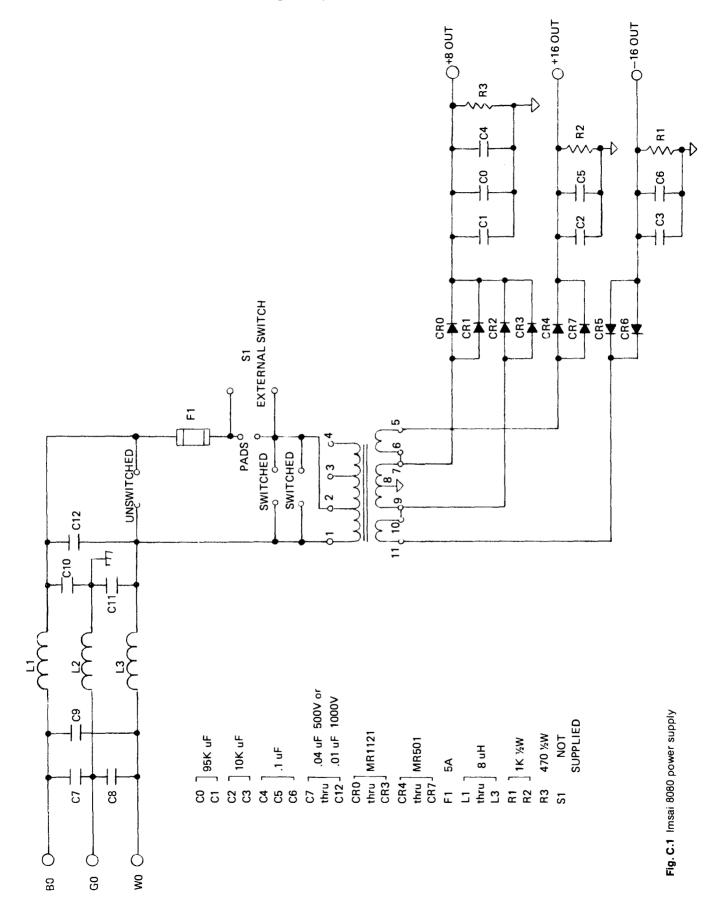

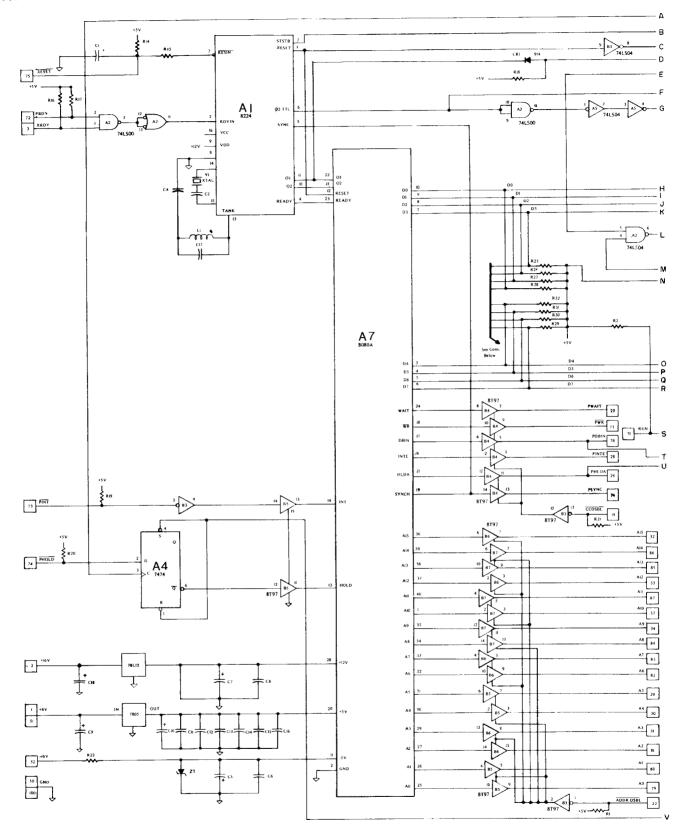

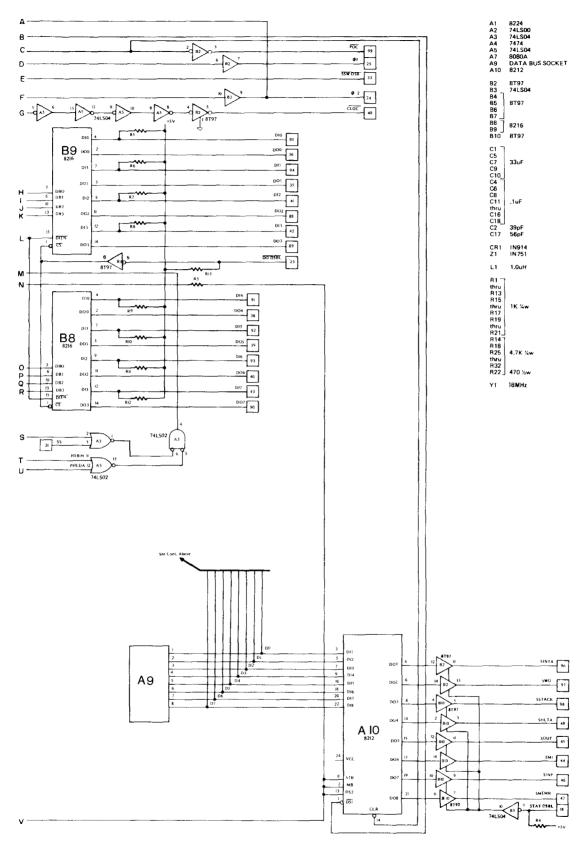

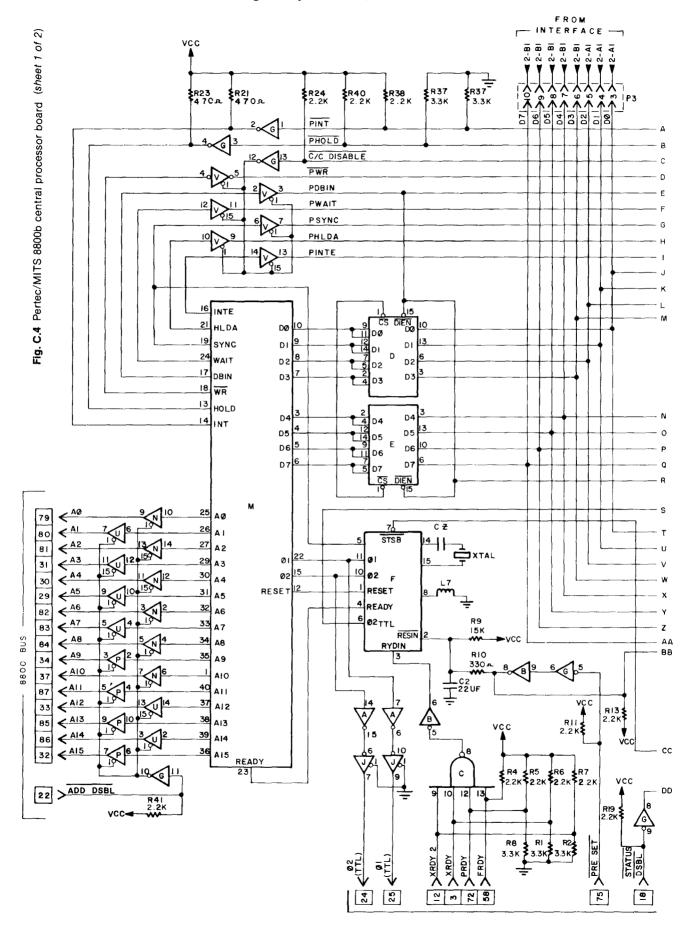

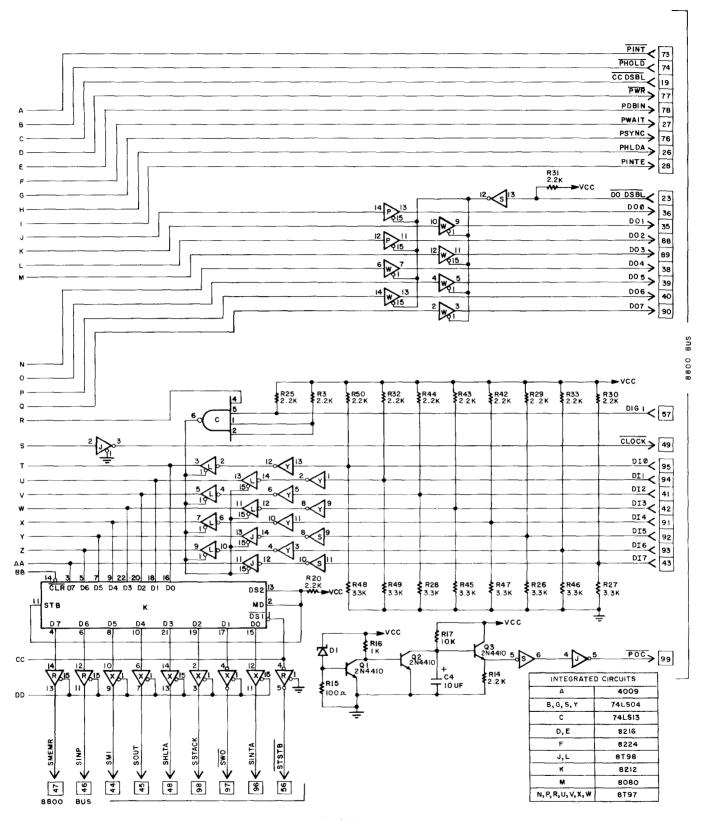

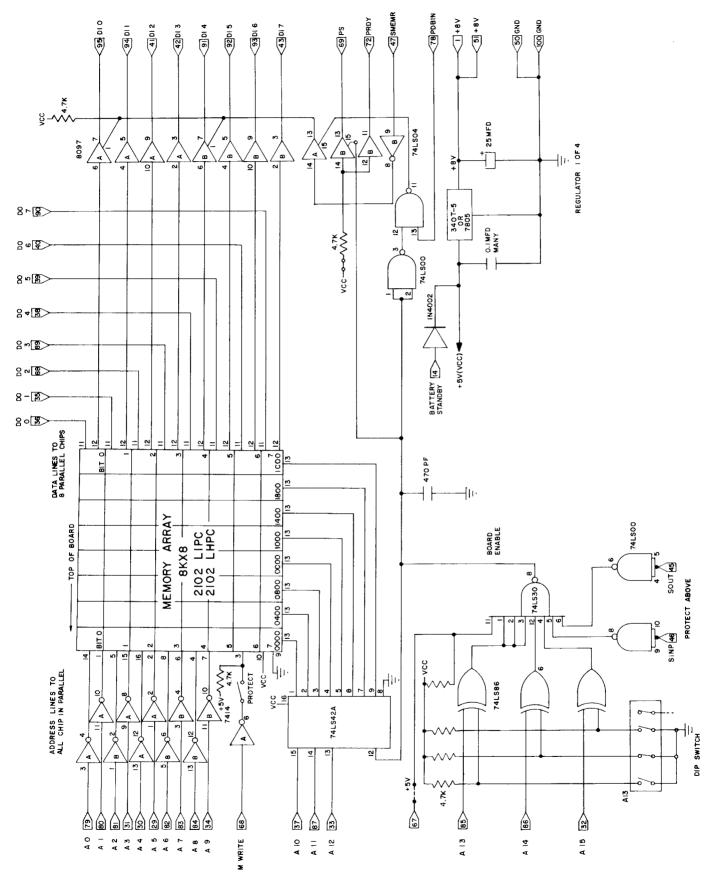

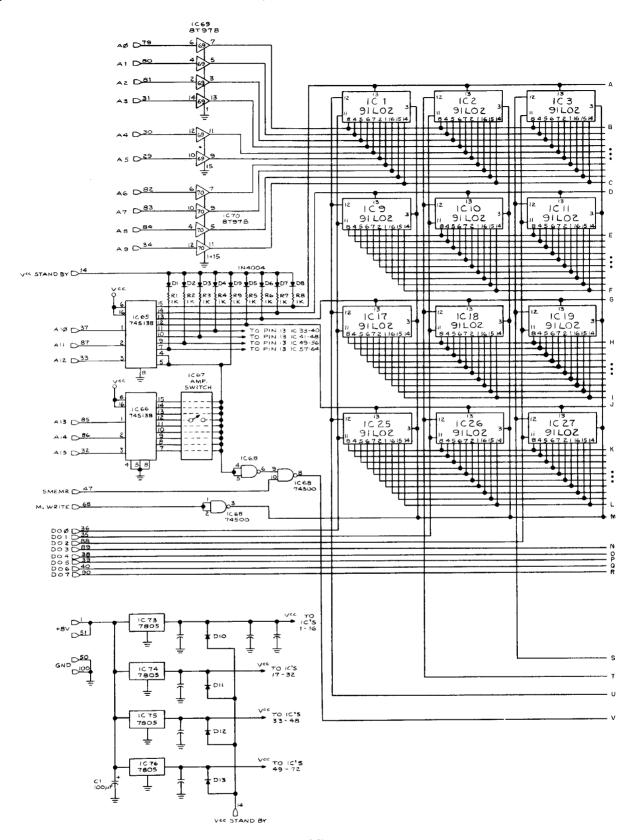

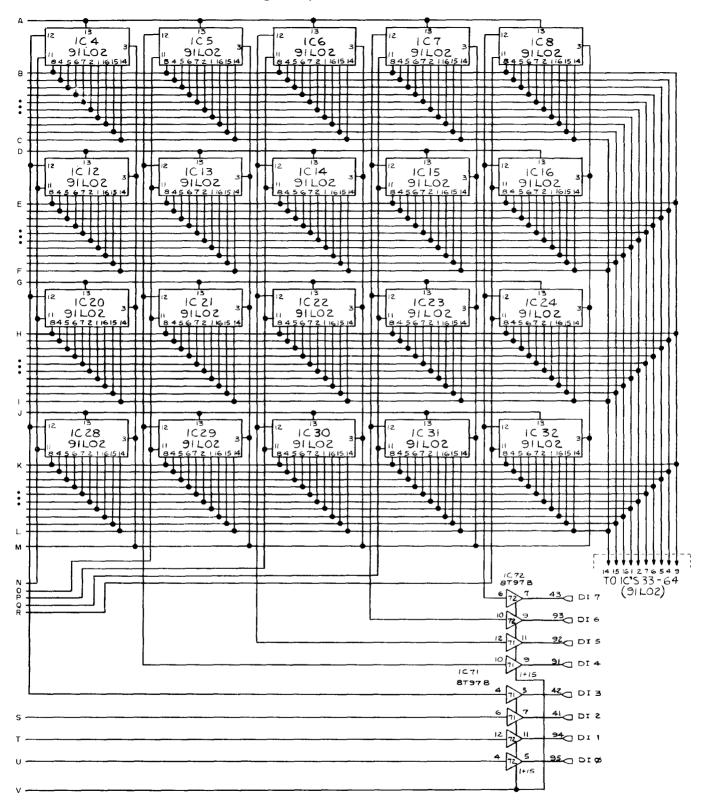

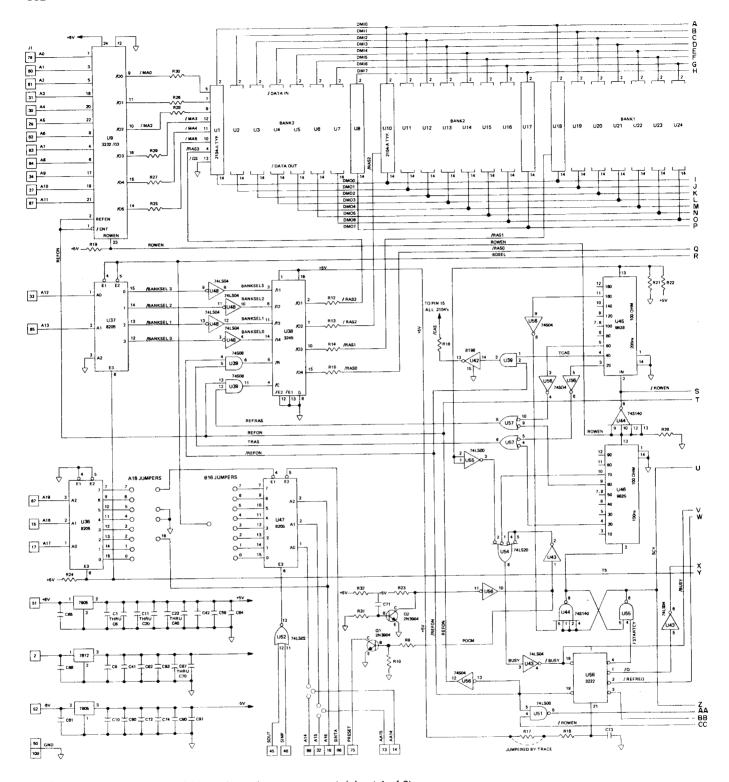

| APPENDIX C. Schematic Diagrams of Commonly Used S-100 Bus Boards |     |  |  |  |

|------------------------------------------------------------------|-----|--|--|--|

| Contents 160                                                     |     |  |  |  |

| APPENDIX D. Proposed S-100 Bus Standard                          | 249 |  |  |  |

| INDEX                                                            | 255 |  |  |  |

|  |  | , |

|--|--|---|

|  |  |   |

# Basic Introduction to Computers and Microprocessors

So you want to use a computer. But just buying one and reading the instruction and operating manuals will not get you very far, especially if you're not familiar with programming or electronics.

By itself, a computer is nothing more than a collection of electronic circuits arranged to process information that is fed into it. In addition to all the electronics, therefore, a computer requires some sort of language to communicate back and forth with the operator—you. Such a language consists of a stable of commands that can be combined in various ways to make the computer do almost anything—solve business problems, simulate speech, play music, play games, or even solve mathematical equations.

#### **A Little Computer Prehistory**

Ever since man started counting on his hands and toes, he has been trying to find easier and faster ways to do everything. The Chinese abacus, developed before 2000 B.C., was one of the first calculating machines (Fig. 1.1). It could add, subtract, multiply, and divide under the skillful control of an operator. And even today, if you were to go into the Chinese community of any sizable city you would probably find some shop-keepers still using the abacus to do their bookkeeping.

Fig. 1.1 The Chinese abacus, one of the first of man's calculating machines, is still in use today.

Early Western civilization, though, struggled along without such a handy device. Moreover, it had to make do with the numbering system devised by the Romans—what today we call Roman numerals:

$$I = 1$$

,  $V = 5$ ,  $X = 10$ ,

$C = 100$ , and  $M = 1000$

It wasn't until the thirteenth and fourteenth centuries that the decimal system of Arabic numerals we use today—0, 1, 2, 3, 4, 5, 6, 7, 8, and 9—came into widespread use. Except for the zero, the numbering system dates back to about the fifth century. However, the idea of a placeholder, the zero, was not developed until about the ninth or tenth century.

Today, the decimal numbering system is used throughout the world as a common mathematical tool. However, most computers don't operate with decimal numbers—they use one of the forms of binary number representations to perform their operations. We'll talk more about numbering systems and how they work in the next chapter.

It wasn't until the seventeenth century that modern computing devices began to take shape. Two of Europe's top philosopher-scientists—Blaise Pascal and Gottfried von Leibnitz—improved on some basic mathematical concepts in a way that made some crude calculators possible (crude, that is, by today's standards).

Pascal's contribution was to increase our understanding of the carry and borrow operations used in addition and subtraction. About the middle of the seventeenth century he developed an adding machine (Fig. 1.2a) that could perform all four basic functions—addition, subtraction, multiplication, and division—by means of notched wheels interconnected by gears. Each wheel had ten notches, and after every complete rotation of a lower wheel the next higher wheel would move ahead one notch. Multiplication consisted of nothing more than repeated additions, and division of nothing more than repeated subtractions. Most electric and gas meters used by the utilities today use the same principle to calculate power usage.

Fig. 1.2 The first crude calculator, "Pascal's Machine Arithmetique," was developed in the seventeenth century (a). During the nineteenth century, Babbage conceived a fully automatic calculating machine he called an analytical engine (b). It used punched cards to feed in the information.

(B)

Leibnitz improved on Pascal's machine by developing a way to do multiplication directly. The principle of his machine, called a stepped reckoner, was used in many electromechanical calculators until the 1960s. Of course, both Pascal's and Leibnitz's machines had to be manually operated; someone had to feed in the numbers and turn the crank for each operation.

About 200 years had to pass before Charles Babbage conceived of a fully automatic calculating machine—he called it the analytical engine (Fig. 1.2b). Unfortunately, his machine was too complex for the metal-working technology of the early 1800s, and it was never built. Babbage's concept of the analytical engine also fostered the idea of using punched cards to feed information (both instructions and data) into a machine for processing. Many computer installations still use Babbage's punched-card concept for entering programs and data.

While Babbage's idea remained sidelined, another mathematician, George Boole, developed a theory of logical algebra (what today engineers refer to as Boolean algebra) that has served as the basis for all modern computer theory. A lot of other developments had to take place, however, before modern computers could even be imagined.

Electricity was still the experimenter's parlor toy in the nineteenth century, and the theory of electricity had yet to be formulated. Once it had been, the great cataclysms of the twentieth century's two World Wars brought forth many advances in electrical machinery and computing devices. Not long after the end of World War II, several large computing machines were developed by researchers at Harvard and the University of Pennsylvania—the Mark I at Harvard, and ENIAC at the University of Pennsylvania.

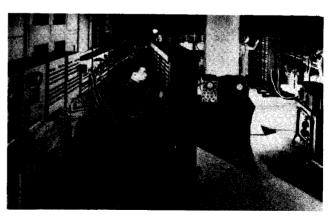

By today's standards, ENIAC (only 30 years old) was a very primitive machine (Fig. 1.3). It used 18,000 vacuum tubes, weighed more than 30 tons, consumed 130,000 watts, and performed only 5000 operations per second. Modern programmable pocket calculators that can store instructions on magnetic cards have as much capability as did ENIAC.

While scientists struggled to keep ENIAC running, researchers at Bell Labs refined the principles of semiconducting materials. By the early 1950s semiconductors—transistors—started to replace vacuum tubes in many applications. They not only offered almost unlimited life compared to that of vacuum tubes, but were only a fraction the size.

Fig. 1.3 World War II spurred scientists at the University of Pennsylvania to develop the first digital computer—ENIAC. (Courtesy Sperry Univac)

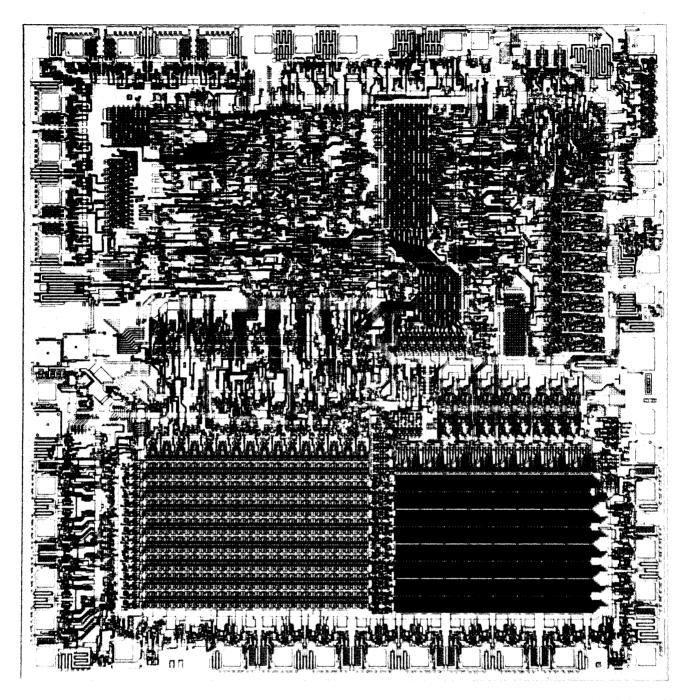

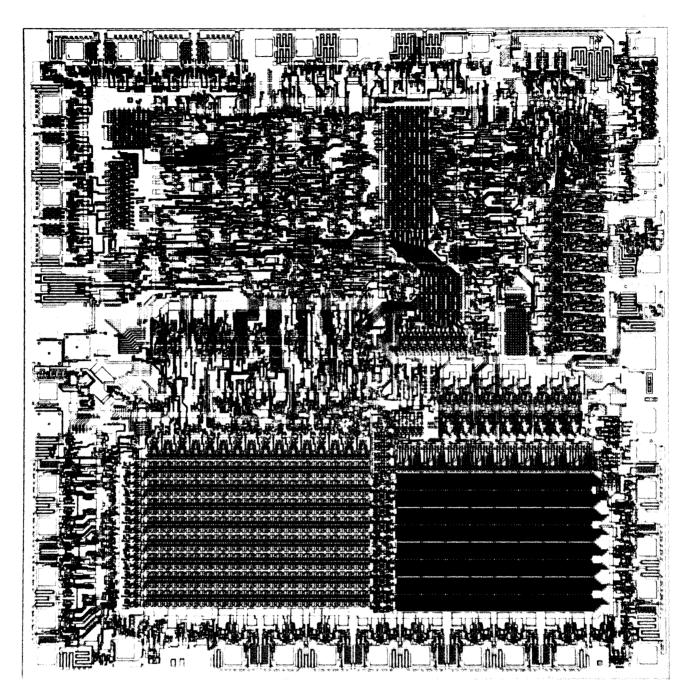

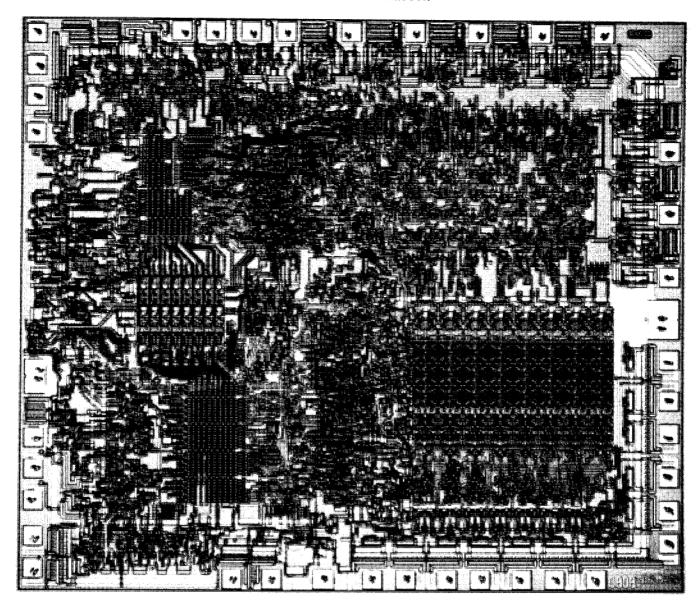

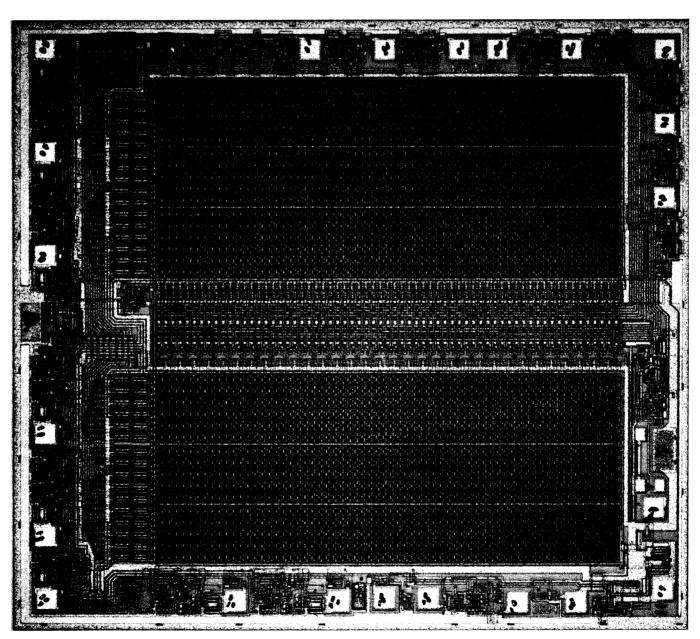

Fig. 1.4 Containing all the major logic sections that make up a computer, the 8048 microcomputer developed by Intel is built into a chip of silicon less than a quarter of an inch on a side. (Courtesy Intel)

Use of these semiconductor materials—germanium and silicon—to build miniaturized systems allowed designers to build machines that required a fraction of the power, were only a fraction the size, and only a small percentage of the weight of ENIAC. The transistor indeed marked the turning point of modern computer design.

But even since the invention of the transistor there have been major advances. In 1958, several companies

managed to combine several transistors and some other components within a single tiny chip of silicon. These all-solid-state circuits, now referred to as monolithic integrated circuits, have reduced the number of actual components needed to build a computer system to a mere handful. As a matter of fact, today's technology has already made possible the complete computer on a single chip of silicon only 0.25 in. on a side (Fig. 1.4). The chip contains about 40,000 transistors and requires

data and instructions. Boolean algebra can thus be used to express many of the processes of computer systems since it is a form of logic reasoning involving two states: truth and untruth.

The ability of a computer to perform logic and math operations rapidly is its only strength. In logic, all statements must be either true or false; there are no intermediate conditions such as "maybe."

The binary numbering system provides us with just the right symbols to work with, and we will adopt them as a standard for the rest of the book. For a true logic statement, the binary value of 1 will be assigned, and for an untrue statement, a value of 0. Thus, a statement can equal 1 or 0 but it cannot have any other value (that is, it must be either true or false). Electronic circuits adapt easily to this system because only two voltages are needed and they can be as simple as ground (nothing, or 0 V) and some level V (which can be positive or negative). The true or false representation can be turned into an on and off equivalent for electronic circuits. Thus, when the circuit is turned on the statement could be true, and when the circuit is turned off the statement could be false. Depending on the type of logic circuits used, the positive level or ground could just as easily represent the true statement or the false statement.

Either statement standing by itself is of little logical interest. A statement has a truth value of 1 or 0, and that's all. However, when several statements are grouped together, other logical inferences can be developed. The three basic logic operators—AND, OR, and NOT—help connect statements so that conclusions can be drawn.

#### **Using Logic Operators**

The AND operator can be used to connect any number of logic statements, all of which must be true for the conclusion to be true. For instance, suppose a friend tells you that on Saturday you will find him at the park if the weather is good AND he has the day off from work. This remark can be written as a logic equation by using symbols: Let A represent the statement that the weather is good, B the statement that he has the day off from work, and C that you will find him at the park. Therefore, if A AND B then C.

Writing out an entire logic operation is often not necessary; a shorthand notation can be used. Sometimes the multiply dot in the middle of a line is used to represent the AND function, and other times the dot is omitted and the individual letters are placed next to each other:

Each of the two statements A and B can be either true or false. If true, we assign the statement a value of 1, if false, a value of 0. The statements can be tabulated to show all four possible combinations and the possible outcomes:

| Statement B | Outcome (A · B)     |

|-------------|---------------------|

| 0           | 0                   |

| 1           | 0                   |

| 0           | 0                   |

| 1           | 1                   |

|             | Statement B 0 1 0 1 |

This type of listing is called a truth table since it shows every possible combination of the two statements.

The OR operator can also be used to connect any number of logic statements. However, unlike operations with the AND operator, only one statement of all those connected need be true for the outcome to be true. Let's use the same example we used for the AND operator but modify it slightly: A friend tells you that on Saturday you will find him at the park if the weather is good OR he has the day off from work.

We can write this statement in the form of a logic equation if we use the plus symbol + to represent the logic OR operation. Thus, if A + B then C. Whenever A or B is true, or they are both true, the outcome is true. Again, this can be shown in truth-table form very simply:

| Statement A | Statement B | Outcome $(A + B)$ |

|-------------|-------------|-------------------|

| 0           | 0           | 0                 |

| 0           | 1           | l                 |

| 1           | 0           | l                 |

| 1           | 1           | 1                 |

The only time your friend won't be at the park will be if the weather is not good AND he doesn't have the day off from work.

The last basic logic operator, the NOT function, can be used to invert or complement a logic statement. It is usually symbolized in shorthand by an overscore of the logic statement or statements you want to invert. Let's see how the logic statements used for the AND and OR operators can be rewritten.

The statement  $\underline{A}$  refers to the fact that "the weather is nice"; therefore,  $\overline{A}$  represents the statement that "the weather is not nice." Similarly,  $\underline{B}$  represents the statement that "he has the day off from work," and  $\overline{\underline{B}}$  means that "he does not have the day off from work." Since  $\underline{A}$  is represented by the binary 1,  $\overline{A}$  would then be binary 0 ( $\underline{A} = 1$ ,  $\overline{A} = 0$ ). Common pronunciations of  $\overline{A}$  are "not  $\underline{A}$ " and " $\underline{A}$  bar," although you may run across others. The truth table for the NOT function is very simple since it operates on one item at a time:

$$\begin{array}{ccc} A & \overline{A} \\ 0 & 1 \\ 1 & 0 \end{array}$$

Each of the logic operators has a physical equivalent that you might find easy to relate to. The simplest example is probably the common water faucet. If you take a look at your kitchen sink, you'll probably see something like the arrangement shown in Fig. 2.1. On top of the sink are two faucets (call them A and C) and a common spout. Under the sink you'll find two valves (call

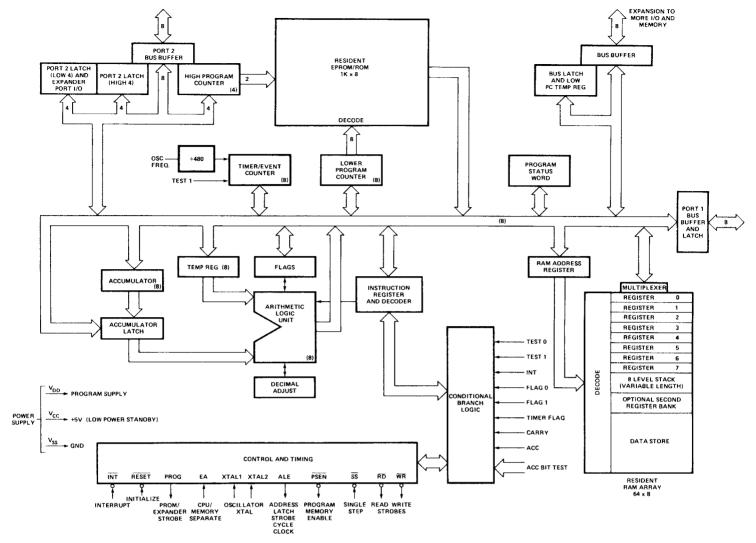

Fig. 1.4 Containing all the major logic sections that make up a computer, the 8048 microcomputer developed by Intel is built into a chip of silicon less than a quarter of an inch on a side. (Courtesy Intel)

Use of these semiconductor materials—germanium and silicon—to build miniaturized systems allowed designers to build machines that required a fraction of the power, were only a fraction the size, and only a small percentage of the weight of ENIAC. The transistor indeed marked the turning point of modern computer design.

But even since the invention of the transistor there have been major advances. In 1958, several companies

managed to combine several transistors and some other components within a single tiny chip of silicon. These all-solid-state circuits, now referred to as monolithic integrated circuits, have reduced the number of actual components needed to build a computer system to a mere handful. As a matter of fact, today's technology has already made possible the complete computer on a single chip of silicon only 0.25 in. on a side (Fig. 1.4). The chip contains about 40,000 transistors and requires

Fig. 1.4 (cont'd) Containing all the major logic sections that make up a computer, the 8048 microcomputer developed by Intel is built into a chip of silicon less than a quarter of an inch on a side. (Courtesy Intel)

less power than even one of the vacuum tubes used in ENIAC. And modern technology is striving to improve on this circuit—another two years will see up to 100,000 transistors on a single chip of silicon.

#### What Is a Computer?

Basically, any device can be called a computer that, once given instructions and information to process, proceeds to carry out those instructions. Human beings are forms of highly complex computers, too. Each of us can accept many types of data through our senses, and, based on our earlier experiences and learning (programming), can react to solve the problem posed. However, there is one major difference between mechanical and human computers: Human "computers" are capable of taking original action without instructions; mechanical computers can only do what they are instructed to do

and cannot modify what they are doing without following a preordained procedure.

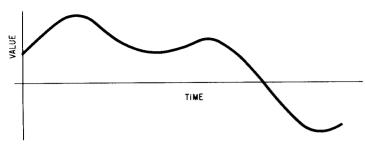

Modern computers can be split into two basic families: analog and digital. The analog computer works with signals that are continuous. By continuous, we mean signals that can take on an infinite number of values between two points, as shown in Fig. 1.5. Analog computers must know the value of these signals, or at least how a signal compares to the other signals also being used as information.

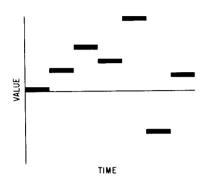

Conversely, digital computers work on discrete, discontinuous numerical values, such as those shown in Fig. 1.6. Currency offers a good example of such "discrete" values. The amount of money you pay for a candy bar is a digital quantity—say, between 0 and \$1. Since only 100 discrete amounts (cents) exist between these limits, the change from one value to the next is discontinuous. But, since digital computers don't care

Fig 1.5 Analog signals can take on an infinite number of values between two points on the graph.

Fig 1.6 Digital signals are represented by discrete, discontinuous numerical values that can appear as steps on a graph.

whether one value is larger than another, a simple way to represent an amount had to be found. More about computer numbering systems and information representation will be presented in the next chapter.

Since this book deals with the use and circuit design of digital computer systems, the rest of the discussions pertain to digital computer systems only. (If you're interested in finding out more about analog computers, see the references in Appendix A.) Digital machines perform arithmetic operations and can make logic decisions based on instructions fed into the machine. Therefore, basic computer mathematics includes the operations of addition, subtraction, multiplication, and division, as well as logic operations such as AND, OR, NAND, NOR, Exclusive-OR (XOR), etc. (More about these functions later in the book.)

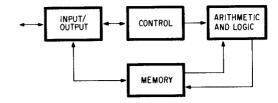

No two digital computers are identical, especially if you look inside. You can give them the same commands and the same data and, in all probability, get the same answers. But inside, each machine handles the information in a different way. The internal organization of a computer is often referred to as the machine's "architecture." All computers can, at least for the sake of analysis, be broken into five basic building blocks: an input section, a memory section, a control section, an arithmetic and logic section, and an output section. A typical interconnection diagram of these building blocks is shown in Fig. 1.7.

The input part of the computer is often some manually operated device similar to a typewriter, but it could just as easily be a magnetic tape reader or a

Fig. 1.7 Any computer system can be broken down into several basic building blocks.

punched tape reader or any of the many other types of input devices. Part of the input system's job is to translate the information prepared by the operator into a form the computer can digest.

Once information has been converted into digital signals, it is usually fed into the memory section of the computer, where it is stored until needed. The memory section also holds the instructions and often the basic operating procedures of the computer itself. Computer memory devices include such units as magnetic tapes, magnetic discs (mass storage devices), ferrite cores, and semiconductor circuits called flip-flops, RAMs, or ROMs.

To coordinate all the operations of the computer, the control section selects information and instructions from a storage location in memory in the proper sequence and lets it flow to the proper section for processing. The control section is the decision-making element of any computer. Inside an actual machine, however, the control circuits are actually spread out through the entire machine and are not grouped together as shown in Fig. 1.7.

The actual processing is done by the arithmetic and logic section of the computer. In this section, digital information can be manipulated, analyzed, and rearranged under the direction of the control unit.

Once the information has been processed, it is often fed back into the memory before you see the answer. Under the direction of the control section, the answers are delivered to you by means of some output device—in some cases, the same machine that you entered the instructions into, and, in other cases, possibly a printer, a tv screen, or a magnetic-tape recorder.

Of course, there are several parts of the computer that we've skipped over for the moment—the power supply, the front panel, and the cabinet. However, these sections are much like the "dressing" on a cake. They must be there, but all you have to know is that they're there and they do their work. Some operations of the front control panel will be discussed in a later chapter.

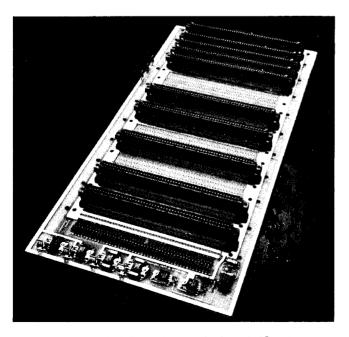

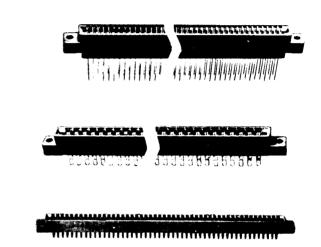

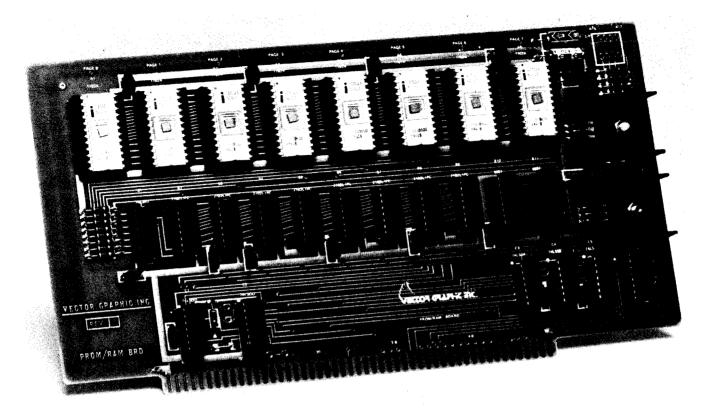

Often, the various sections of the computer are built on separate circuit cards and then the cards are connected together. The cards described in the following chapters are all identical in physical size—5 in. × 10 in.—and have an edge connector on them that permits up to 100 connections to the circuitry on the card (Fig. 1.8). In a computer, many of these cards are interconnected by a wiring scheme called a bus—a common

Fig. 1.8 Some typical S-100 bus compatible circuit cards. (Courtesy Pertec)

group of wires over which signals from all the boards can be transmitted.

nology has been able to shrink the circuitry needed to build a CPU so that all the components needed fit on a single chip of silicon a mere quarter of an inch on a side—the microprocessor (Fig. 1.10). Of course, for it to work, power and special signals must be supplied and circuits to make the output signals stronger (buffers) must be used.

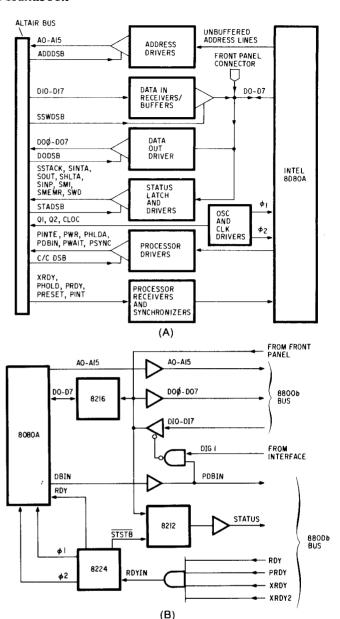

The computers and cards discussed in this book all use the same bus structure, commonly referred to as the S-100 bus. This bus was originated by MITS, when the company introduced the Altair 8800—the first personal computer—back in 1975. Since then over 50 companies have adopted the same interconnect bus and offer a wide variety of computer cards that connect to the bus. The computers discussed in this book, the Altair 8800b from MITS and the Imsai 8080 from Imsai Manufacturing (Fig. 1.9), use the S-100 bus and can accept all of the bus-compatible cards made by other companies.

#### What Is a Microprocessor?

These computer systems are all based on electronic circuits that have been in existence since 1970, and some only in the last few years. The heart of these computer systems is the central processor unit (CPU), which contains the arithmetic and logic unit. Modern tech-

But a microprocessor is not a computer. It is just the processing section. Along with the basic microprocessor, many memory circuits, input/output circuits, and other specialized components are needed to make a full computer. And, just as with the large computers, all microprocessors are not the same. There are about 30 different types, made by about as many different companies, and each has its own architecture, instruction set, power supply requirements, and other peculiarities.

Both the Altair 8800b and the Imsai 8080 were designed to operate with one specific microprocessor as the central processor—the 8080A made by Intel Corp., and now available from about half a dozen vendors. However, since the creation of the 8080A in 1973, newer microprocessors, the Z-80 from Zilog and the 8085 from Intel, offer compatibility and improved performance.

Fig. 1.9 The heart of any computer system, the computer itself, typically comes in a large case with many front panel switches and indicators. The Imsai 8080 (left) and the Pertec Altair 8800b (right) were two of the first personal computer systems. (Courtesy Pertec and Imsai)

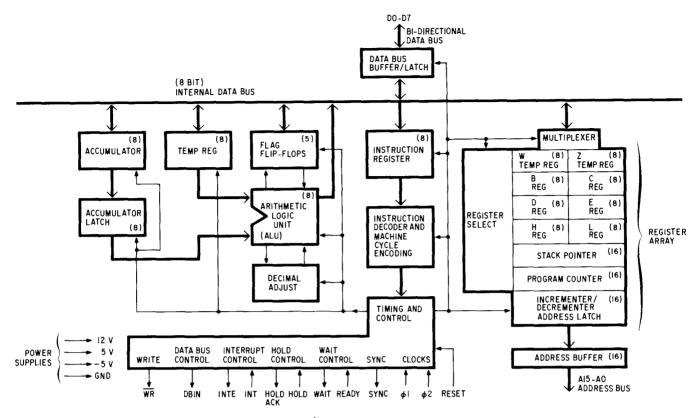

The microprocessor is just what its name implies a miniature processor. Buried within the silicon chip are all the basic elements of a computer—the control section, the processing section, and some memory (usually referred to as temporary registers). Specifically, the 8080A has an internal structure as shown in Fig. 1.11. As you can see, there are quite a few subsections squeezed into that quarter-inch chip of silicon. To use the computer system, it's not necessary to know how the microprocessor works or what each of its internal subsections does. Also, for the most part, you must have a fairly good technical background in computers before you can even understand what the different sections do. For those of you with a reasonable background in computers, the next few paragraphs will try to summarize the characteristics of the 8080A. For those of you with no background, some additional reading from selections in Appendix A might be warranted if you want to understand the inner workings of computers.

The 8080A microprocessor is a circuit designed to process information in digital form. It operates on digital information in groups of eight binary digits at a time (each binary digit is referred to as a bit, and a group of eight bits is referred to as a byte), and can perform many different types of mathematical and logic operations on the digital information. There are four basic internal sections of the 8080A—the register array and address logic, the arithmetic and logic unit, the instruction register and control section, and the bidirectional, three-state data bus interface.

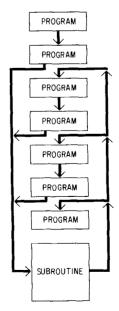

The register section consists of an array of memory cells organized so that six 16-bit information blocks can be stored. Two of the 16-bit registers are assigned specific purposes—they serve as the program counter (PC) and the stack pointer (SP). The purpose of the program counter is to keep track of the location of the current program instruction in the computer's memory. The stack pointer maintains the location of a section of memory called a stack, which is used to hold memory

addresses when a computer program calls a subroutine. (More about programming in a later chapter.)

Three more of the 16-bit registers are actually broken into six 8-bit registers that can be operated on individually or in pairs. The 8-bit registers are referred to as the B, C, D, E, H, and L registers and can be accessed in pairs as BC, DE, and HL. All of the registers discussed so far can be manipulated by instructions. One other register, called the temporary register, also stores up to 16 bits, but it cannot be controlled by instructions. This register, referred to as the W, Z register, is used only for the internal execution of instructions.

Bytes can be transferred between any of the registers inside the processor by the appropriate instruction. Double-byte transfers can also be performed between the register pairs and the SP and PC registers and the address logic. The address logic in turn feeds a 16-bit binary number to the memory array external to the processor, thus permitting the microprocessor to access any one of 65,536 memory locations.

The arithmetic and logic unit (ALU) within the 8080A performs the actual manipulating of the computer data. It performs the arithmetic, logic, and rotate operations dictated by the instructions. In addition to the circuits necessary to perform the operations, there are several registers used to hold intermediate information—an 8-bit register called the accumulator, another 8-bit register called the temporary accumulator, an 8-bit register called the temporary register, and a 5-bit register called the flag register that is used to hold indicators from operations that took place in the arithmetic and logic unit. The indicators are ZERO (shows when an operation leaves a zero result in the accumulator), CARRY (shows when an operation generates a carry from the most-significant bit position), SIGN (shows when an operation leaves a negative result in the accumulator), PARITY (shows whether the sum of all the bits left in the accumulator is odd or even), and AUXILIARY CARRY (shows when there is a carry

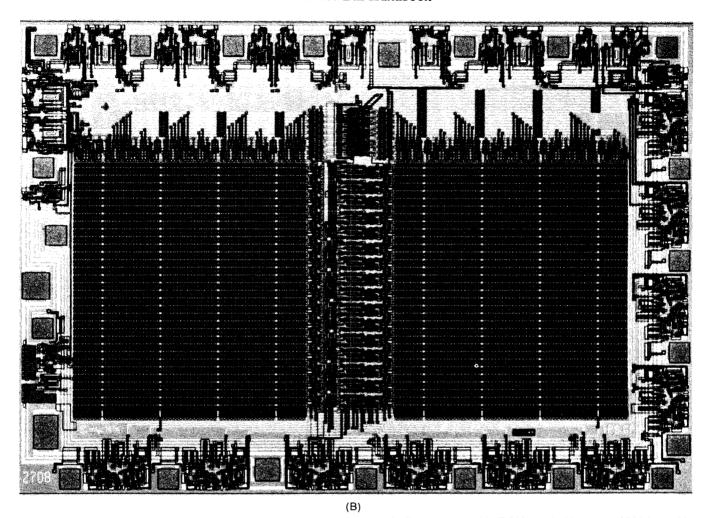

Fig. 1.10 Making the home computer system possible, the microprocessor offers the computing power of large computers in an extremely small package. Housed in a 40-pin DIP, the 200 mil square chip of silicon called the 8080 contains over 10,000 transistors. (Courtesy Intel)

generated from the fourth to the fifth bits in the accumulator).

The accumulator can be loaded from the ALU and the internal bus, and can transfer data to the temporary accumulator and the internal bus. A special instruction permits the contents of the accumulator and the AUXILIARY CARRY flag to be tested for decimal correction when the processor is handling decimal numbers in binary form. The DAA instruction permits the results to be corrected back to the decimal format.

The instruction register and control section of the microprocessor holds the current instruction and controls all the internal operations of the processor for the execution of that instruction. To properly synchronize all the internal operations, special timing signals called clocks are fed into the microprocessor.

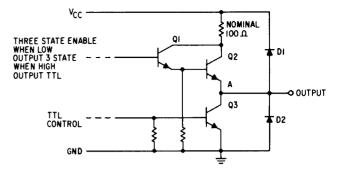

Information flows in and out of the microprocessor over an 8-bit path called the data bus. Digital information can flow in either direction, depending on the operation the processor is performing. The bus is referred to as a three-state bus because in addition to the normal HIGH and LOW logic states possible, the bus can be

Fig. 1.11 The architecture of the 8080A microprocessor is similar to that of most computer central processors. An arithmetic and logic unit does all the processing and it is controlled by instructions and data fed into it.

made to go into a state where it effectively uses no power and has no effect on the other circuits it is connected to. This third state is often referred to as a high-impedance state. When the bus is not in use it is usually placed in this third state just to minimize power consumption.

#### The Microprocessor Operates in Cycles

Each time the microprocessor executes an instruction, it completes an *instruction cycle*. The duration of an instruction cycle includes the time required to pull an instruction from memory and execute it. During the pull, or fetch, part of the cycle, the selected instruction (one, two, or three bytes long) is extracted from the memory and deposited in the processor's instruction register. Then, during the execution phase of the cycle, the instruction is decoded and translated into specific actions by the control logic.

Every instruction cycle consists of one, two, three, four, or five machine cycles. The fetch portion of an instruction cycle requires one machine cycle every time a byte must be fetched from memory. The length of the execution portion of the cycle depends on the instruction being executed—some instructions may not require any machine cycles beyond those of the fetch operation, others may require additional cycles.

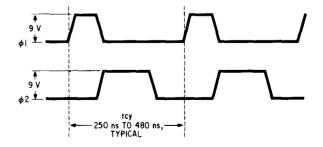

Each machine cycle further consists of three, four, or five states, where a state is the smallest unit of processing activity and is defined as the interval between two successive positive-going transitions of the phase-one clock signal. (The 8080A has all of its timing signals supplied by a two-phase clock generator that delivers two signals to the phase-one and phase-two clock input terminals, as shown in Fig. 1.12.)

Every instruction cycle has at least one memoryreference operation during which the instruction is fetched. An instruction cycle must always have a fetch, even if the execution of the instruction requires no further references to memory. The first machine cycle in every instruction cycle is thus a fetch operation. Beyond that, there are no restrictions; subsequent

Fig. 1.12 Performing its instructions with timing derived from a two-phase clock signal, the 8080A operates at frequencies of up to 4 MHz.

machine cycles can perform any type of operation. While no one instruction cycle will contain more than five machine cycles, there are 10 types of machine cycles that can possibly occur during an instruction cycle:

- 1. Instruction fetch

- 2. Memory read

- 3. Memory write

- 4. Stack read

- 5. Stack write

- 6. Input

- 7. Output

- 8. Interrupt

- 9. Halt

- 10. Halt · Interrupt

The processor identifies the machine cycle in progress by transmitting an 8-bit status word during the first state of every machine cycle. Updated status information is presented on the 8080A's data lines during the SYNC interval in the timing sequence. These data are usually saved in a register and can be used to provide control signals for external circuitry.

Before delving into computer operations any further, let's backtrack and go through a quick review of computer mathematics and logic, as well as a simple summary of the basic electronics needed to understand the various components used in the computers.

## Binary Mathematics and Boolean Algebra

No matter which computer is used, or what instructions are given, the same number system performs all the mathematical operations and the same logic gates perform the Boolean operations. Computers use the binary numbering system to perform their operations since for electronic circuits the two states of the binary system—1 (HIGH) and 0 (LOW)—provide the simple equivalents to the ON and OFF states used in electronic switching systems. But no matter which numbering system is used, the operations performed—addition, subtraction, multiplication, and division—are all done in the same way; only the numbers change.

#### Computer Math: A Quick Review

Mathematics with the decimal numbering system has become so commonplace that no one really has to sit down and think about how a problem has to be done. If we wanted to solve some simple problems such as these:

$$48 - 12 = ?$$

$13 + 26 = ?$

$4 \times 4 = ?$

$18 \div 3 = ?$

we wouldn't even slow down to give the answers; we would just rattle off 36, 39, 16, and 6.

But if we switch numbering systems to one we aren't familiar with, such as the binary numbering system used by all computers, some of us would be hard pressed to solve the same problems:

$$110000 - 1100 = ?$$

$1101 + 11010 = ?$

$100 \times 100 = ?$

$10010 \div 11 = ?$

The answers are 100100, 100111, 10000, and 110. All the same mathematical rules apply to any numbering system, but the notation can confuse you. Let's try to clarify all numbering systems by first looking at the one we're most familiar with—the decimal system.

When we write down a number and then say it aloud, we begin to get the organizational picture of our num-

bering system. For instance, the number 3165 is pronounced three-thousand, one-hundred sixty-five. Now, if we break it down into the positional notation represented by each number spoken aloud, we get

$$3 \times 1000 = 3000$$

$1 \times 100 = 100$

$6 \times 10 = 60$

$5 \times 1 = 5$

$3165$

As written, the center column of the breakdown is nothing more than a listing of the powers of 10, similar to the breakdown shown in Table 2.1. Each column of a decimal number represents a power of 10, and the highest number that can appear in each column is a nine. The name of this numbering system stems from the Latin decema meaning 10, since there are a total of 10 symbols used to represent all numbers.

Table 2.1 Positive Powers of 10

```

10^{0} = 1 = 1

10^{1} = 10 = 10

10^{2} = 100 = 10 \times 10

10^{3} = 1000 = 10 \times 10 \times 10

10^{4} = 10,000 = 10 \times 10 \times 10 \times 10

10^{5} = 100,000 = 10 \times 10 \times 10 \times 10 \times 10

10^{6} = 1,000,000 = 10 \times 10 \times 10 \times 10 \times 10

```

Since each column is represented by a power of 10, we can say that the columns are ordered in ascending or descending sequence, depending on which direction we read from. Normally, a number is read with the largest power of 10 first, so that the number follows a descending sequence. Another name for the highest order column is the "most-significant digit," and for the lowest order column the "least-significant digit." The total number of columns defines the number of digits.

We often use a decimal point in writing numbers that are a fraction of a whole number. To simplify the use of the decimal point, we use negative powers of 10 to represent numbers to its right, as shown in Table 2.2. Thus,

Table 2.2 Negative Powers of 10

| $10^{-1} = 0.1$ = 1/10             |

|------------------------------------|

| $10^{-2} = 0.01 = 1/100$           |

| $10^{-3} = 0.001 = 1/1000$         |

| $10^{-4} = 0.0001 = 1/10,000$      |

| $10^{-5} = 0.00001 = 1/100,000$    |

| $10^{-6} = 0.000001 = 1/1,000,000$ |

a number such as 15.328 would be represented by

The 10 different symbols used for the decimal system form the base, or radix, of the system (base 10). Any number, however, can be used as the base. Three of the other most common numbering systems in use are the octal, the hexadecimal, and, of course, the binary, where the respective bases are 8, 16, and 2.

#### **Nondecimal Numbering Systems**

In a numbering system based on eight symbols (the octal), we can count from 0 to 7 before running out of numbers. If we count higher, we must follow the same procedure used for decimal counting. After we fill up the first column, a placeholder (zero) must be inserted and a carry placed in the next higher column. The following octal count sequence, with the decimal equivalent shown just below it, illustrates this very clearly:

Of course, numbers written in octal do not have the same value as similar numbers written in decimal notation. In octal, any number filling a column represents a power of eight instead of 10. For instance, the number 1762<sub>8</sub> can be broken into its parts to convert it back into decimal notation.

A base that is larger than 10 can be used, but several new symbols will have to be added. Our alphabet fortunately provides a ready source of symbols. The letters A, B, C, D, E, and F, for instance, have been used to represent the numbers 10, 11, 12, 13, 14, and 15, respectively, in the hexadecimal numbering system. A comparison between the four most popular codes is given in Table 2.3.

Table 2.3 Comparison of Binary, Octal, Decimal, and Hexadecimal Codes

| Binary | Octal | Decimal | Hexadecimal |

|--------|-------|---------|-------------|

| 0000   | 00    | 00      | 0           |

| 0001   | 01    | 01      | 1           |

| 0010   | 02    | 02      | 2           |

| 0011   | 03    | 03      | 3           |

| 0100   | 04    | 04      | 4           |

| 0101   | 05    | 05      | 5           |

| 0110   | 06    | 06      | 6           |

| 0111   | 07    | 07      | 7           |

| 1000   | 10    | 08      | 8           |

| 1001   | 11    | 09      | 9           |

| 1010   | 12    | 10      | Α           |

| 1011   | 13    | 11      | В           |

| 1100   | 14    | 12      | С           |

| 1101   | 15    | 13      | D           |

| 1110   | 16    | 14      | E           |

| 1111   | 17    | 15      | F           |

Base 16 numbers also follow the same mathematical guidelines, as you can see from the following hexadecimal-to-decimal conversion of the number B13E:

The binary number system is perhaps the simplest of systems to use and to understand. There are only two symbols in the binary system—0 and 1—but all the same rules again apply. A typical binary counting sequence, with the decimal equivalents shown on the line below, would be

Each binary digit, or bit, represents a power of two, so that any number can be represented by adding bits together. As a typical example, let's break down the number 1100111 and convert it back into decimal notation:

Converting a binary number into decimal notation is easy enough, and going the other way is also simple. The quickest conversion method is a simple process of dividing and checking the remainder. Let's look at an actual example, the conversion of 241 into binary:

| Number |   | Divisor |   | Result |   | Remainder | Comments                                  |

|--------|---|---------|---|--------|---|-----------|-------------------------------------------|

| 241    | ÷ | 2       | = | 120    | + | 1         | if remainder = $1$ , $2^0$ is present     |

| 120    | ÷ | 2       | = | 60     | + | 0         | if remainder = $0$ , $2^1$ is not present |

| 60     | ÷ | 2       | = | 30     | + | 0         | if remainder = $0$ , $2^2$ is not present |

| 30     | ÷ | 2       | = | 15     | + | 0         | if remainder = $0$ , $2^3$ is not present |

| 15     | ÷ | 2       | = | 7      | + | l         | if remainder = $1, 2^4$ is present        |

| 7      | ÷ | 2       | = | 3      | + | 1         | if remainder = $1, 2^5$ is present        |

| 3      | ÷ | 2       | = | 1      | + | 1         | if remainder = $1, 2^6$ is present        |

| 1      | ÷ | 2       | = | 0      | + | 1         | if remainder = $1$ , $2^7$ is present     |

The binary number is thus 11110001, with the leftmost digit representing the most-significant bit (MSB) and the right-most digit representing the least-significant bit (LSB).

#### **Doing Math with Binary Numbers**

In the binary system, the highest number that appears in each column is, of course, 1. Therefore, every time two 1s get added together, they generate a 0 and a carry. Let's look at a few simple examples:

The sum of 1 + 1 is 2, but 2 can also be represented as  $2^1$  and thus counts as a 1 in the next column. Let's now look at a more complicated example:

To do the addition, first combine the right-most bits to form a sum of 0 and generate a carry of 1 that gets placed in the next column. The second column then has a total of 3, which, of course, cannot exist in binary. A total of 2 must thus be carried into the third column and that leaves a remainder of 1, which stays in the second column. The 2 that was carried into the third column appears as a 1 and is summed, just as in the first column. The sum is 0, and another carry is generated. The last column follows the same procedure. Since the sum is again 0, another carry is generated and gets added to a placeholder 0. Diagramatically, the same problem can be shown as follows:

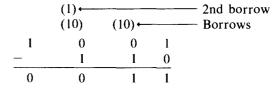

Subtraction procedures are just the reverse; instead of a carry to the left, you must generate a borrow to the right. Here are a few simple examples that illustrate basic subtraction:

$$(1) \longleftarrow Borrow$$

$$\begin{array}{ccccc}

0 & 1 & 1 & 0 \\

-0 & -0 & -1 & -1 \\

\hline

0 & 1 & 0

\end{array}$$

Let's take a closer look at the borrow with a more complex subtraction example:

For the right-most digits there is no borrow problem, and the difference is 1. The next digits, however, require a borrow from the left-most column, and the borrowing goes from left to right until the borrow reaches the second column. Since each column represents twice what is stored in the previous column, the borrowing of a 1 provides 2 for the column that needs the borrow. Thus, when the 1 is subtracted there is a remainder of 1. In the third column, 1 has already been borrowed from the 2 that was shifted right, so when 1 is subtracted the difference becomes 0. Diagrammatically, the subtraction looks like this:

Let's compare this operation to a similar decimal subtraction:

2 (15) 8 (12)

$$\leftarrow$$

Borrow plus whatever  $\beta$  5  $\emptyset$  2 was in the column  $\frac{1}{1}$   $\frac{9}{6}$   $\frac{3}{5}$   $\frac{8}{4}$

The binary numbering system is the easiest one for digital electronic circuits to use since only two electrical levels are needed: one to represent the binary 1 and another to represent the binary 0. Different computer systems use different electrical levels to represent 1 and 0, but whatever voltage levels are used, electronic circuits operate similarly.

The computing power of all computers is based on their ability to perform logic operations controlled by data and instructions. Boolean algebra can thus be used to express many of the processes of computer systems since it is a form of logic reasoning involving two states: truth and untruth.

The ability of a computer to perform logic and math operations rapidly is its only strength. In logic, all statements must be either true or false; there are no intermediate conditions such as "maybe."

The binary numbering system provides us with just the right symbols to work with, and we will adopt them as a standard for the rest of the book. For a true logic statement, the binary value of 1 will be assigned, and for an untrue statement, a value of 0. Thus, a statement can equal 1 or 0 but it cannot have any other value (that is, it must be either true or false). Electronic circuits adapt easily to this system because only two voltages are needed and they can be as simple as ground (nothing, or 0 V) and some level V (which can be positive or negative). The true or false representation can be turned into an on and off equivalent for electronic circuits. Thus, when the circuit is turned on the statement could be true, and when the circuit is turned off the statement could be false. Depending on the type of logic circuits used, the positive level or ground could just as easily represent the true statement or the false statement.

Either statement standing by itself is of little logical interest. A statement has a truth value of 1 or 0, and that's all. However, when several statements are grouped together, other logical inferences can be developed. The three basic logic operators—AND, OR, and NOT—help connect statements so that conclusions can be drawn.

#### **Using Logic Operators**

The AND operator can be used to connect any number of logic statements, all of which must be true for the conclusion to be true. For instance, suppose a friend tells you that on Saturday you will find him at the park if the weather is good AND he has the day off from work. This remark can be written as a logic equation by using symbols: Let A represent the statement that the weather is good, B the statement that he has the day off from work, and C that you will find him at the park. Therefore, if A AND B then C.

Writing out an entire logic operation is often not necessary; a shorthand notation can be used. Sometimes the multiply dot · in the middle of a line is used to represent the AND function, and other times the dot is omitted and the individual letters are placed next to each other:

Each of the two statements A and B can be either true or false. If true, we assign the statement a value of 1, if false, a value of 0. The statements can be tabulated to show all four possible combinations and the possible outcomes:

| Statement A | Statement B | Outcome (A · B) |

|-------------|-------------|-----------------|

| 0           | 0           | 0               |

| 0           | 1           | 0               |

| 1           | 0           | 0               |

| 1           | 1           | 1               |

This type of listing is called a truth table since it shows every possible combination of the two statements.

The OR operator can also be used to connect any number of logic statements. However, unlike operations with the AND operator, only one statement of all those connected need be true for the outcome to be true. Let's use the same example we used for the AND operator but modify it slightly: A friend tells you that on Saturday you will find him at the park if the weather is good OR he has the day off from work.

We can write this statement in the form of a logic equation if we use the plus symbol + to represent the logic OR operation. Thus, if A + B then C. Whenever A or B is true, or they are both true, the outcome is true. Again, this can be shown in truth-table form very simply:

| Statement A | Statement B | Outcome $(A + B)$ |

|-------------|-------------|-------------------|

| 0           | 0           | 0                 |

| 0           | 1           | 1                 |

| 1           | 0           | 1                 |

| 1           | 1           | 1                 |

The only time your friend won't be at the park will be if the weather is not good AND he doesn't have the day off from work.

The last basic logic operator, the NOT function, can be used to invert or complement a logic statement. It is usually symbolized in shorthand by an overscore of the logic statement or statements you want to invert. Let's see how the logic statements used for the AND and OR operators can be rewritten.

The statement A refers to the fact that "the weather is nice"; therefore,  $\overline{A}$  represents the statement that "the weather is not nice." Similarly, B represents the statement that "he has the day off from work," and  $\overline{B}$  means that "he does not have the day off from work." Since A is represented by the binary 1,  $\overline{A}$  would then be binary 0 (A = 1,  $\overline{A}$  = 0). Common pronunciations of  $\overline{A}$  are "not A" and "A bar," although you may run across others. The truth table for the NOT function is very simple since it operates on one item at a time:

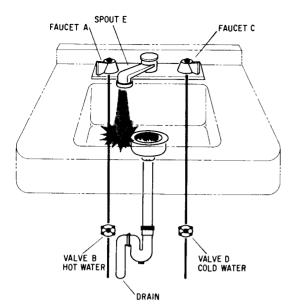

Each of the logic operators has a physical equivalent that you might find easy to relate to. The simplest example is probably the common water faucet. If you take a look at your kitchen sink, you'll probably see something like the arrangement shown in Fig. 2.1. On top of the sink are two faucets (call them A and C) and a common spout. Under the sink you'll find two valves (call

Fig. 2.1 A kitchen sink with two faucets, a common spout, and two emergency valves underneath is a good analogy for combined AND/OR logic statements.

Fig. 2.2 Just as valves are used to start and stop water flow, switches (toggle, push button, rotary, etc.) are used to start and stop electrical current flow. (Courtesy Centralab and Micro Switch)

them B and D), one on the hot water line and one on the cold.

For water to flow out of the tap (call this statement E), the valve under the sink AND its respective faucet must be opened:  $A \cdot B + C \cdot D = E$ . This logic statement combines both the AND and OR operators since the tap is common to both hot and cold water lines. Water will flow if both valves A AND B are opened OR valves C AND D are open.

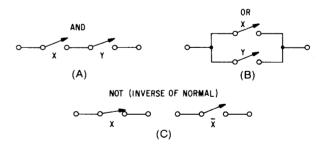

Just as we use valves to start and stop water flow, we can use electrical switches to start and stop electrical current flow (Fig. 2.2). Several switches connected in series perform an AND function (Fig. 2.3a). Switches in par-

allel perform an OR function (Fig. 2.3b), and a simple switch set up to function in a normal way can simulate the NOT function (Fig. 2.3c).

#### **Combining Logic Operators**

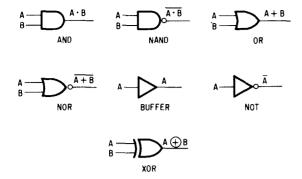

By mixing the three basic operators AND, OR, and NOT together, several other logic functions can be created. An AND combined with a NOT makes a NOT-AND, or NAND function; an OR combined with a NOT makes a NOT-OR, or NOR function; and two NOT functions cancel each other out. The truth tables for these functions and several others are shown in Fig. 2.4. Only two truth statements are used as determining elements in the examples although any number of statements can be used.

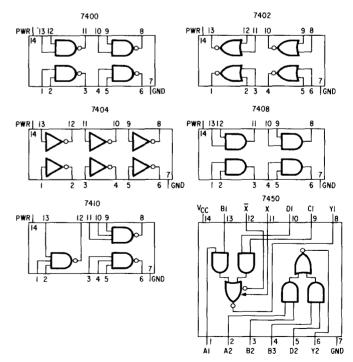

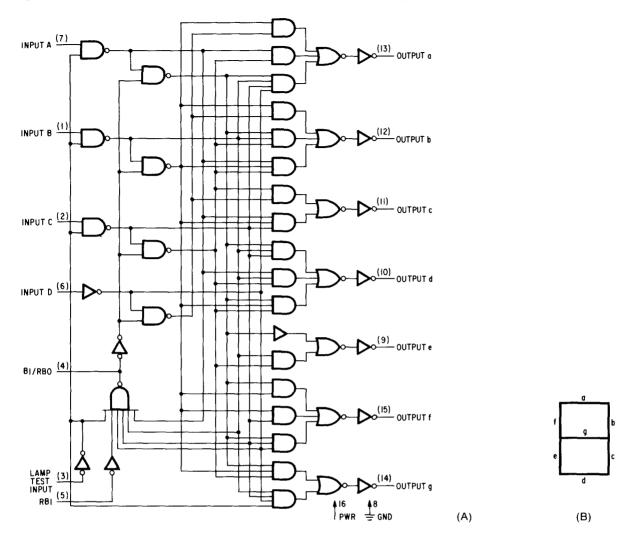

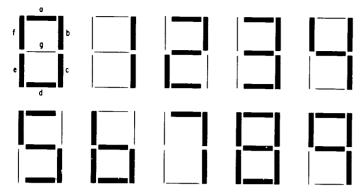

Multiple statements can be combined into one logic equation and there is no limit to the number of statements that can be linked. You can have two, three, four, eight, or more logic statements or expressions combined on one operator. The electronic equivalent to the logic operator is called a *gate*. It is possible to buy AND, OR, NAND, NOR, NOT, Exclusive-OR (XOR), AND/OR, and many other types of gates, each with different numbers of possible inputs. Many of the common symbols for logic gates are shown in Fig. 2.5.

The mathematics of combining these different logic gates is what we call Boolean algebra. Every form of mathematics has some basic theorems, postulates, and underlying truths. In the short space of this book, you'll just get an overview and rudimentary understanding of the basic concepts. (For more about Boolean algebra, see Appendix A for additional reading.)

Fig. 2.3 Switch connections showing (a) AND, (b) OR, and (c) NOT (inverse of normally open) equivalents of logic gates.

| A | В  | A·B | Α   | 8   | A+B | Α  | Ā          | A | В  | A 🕀 B |

|---|----|-----|-----|-----|-----|----|------------|---|----|-------|

| 0 | 0  | ı   | 0   | 0   | ı   | 0  | 0          | 0 | 0  | 0     |

| 0 | 1  | 1   | 0   | 1   | 0   | 1. | i          | 0 | 1  | 1     |

| I | 0  | 1   | ı   | 0   | 0   |    |            | 1 | 0  | 1     |

| 1 | 1  | 0   | - 1 | 1   | 0   |    |            | I | ŧ  | 0     |

|   | (A | )   |     | (B) | )   | (( | <b>C</b> ) |   | (D | )     |

Fig. 2.4 Truth tables for (a) NAND, (b) NOR, (c) NOT-NOT, and (d) Exclusive-OR (XOR) gates.

Fig. 2.5 Commonly used symbols for logic gates.

#### The Basic Rules of Boolean Algebra

Thus far we've looked at truth statements, and if one was true we assigned it a value of 1, and if false a value of 0. Let's see what happens if we try combining statements.

When two true statements are ANDed together, the outcome is always true. If one of the statements is false, the outcome is always false. In symbolic form, some universal statements may be made, as follows:

1. The outcome of a logic AND equation where all but one term is known to be true depends directly on the unknown term:

$$A \cdot 1 = A$$

2. The outcome of a logic AND equation where any of the terms is false is always false:

$$A \cdot 0 = 0$$

3. Any logic statement ANDed with itself is equal to the original logic statement:

$$A \cdot A = A$$

4. Any logic statement ANDed with its complement is always false (see statement 2):

$$A \cdot \overline{A} = 0$$

5. Any logic statement upon which a double NOT operation has been performed is equal to the original statement without any operations performed:

$$\overline{\overline{A}} = A$$

6. The outcome of a logic OR operation where any number of statements are ORed with at least one true statement will always be true:

$$A + 1 = 1$$

7. The outcome of a logic OR equation where one or more terms are known to be false depends on the remaining statements:

$$A + 0 = A$$

8. Any logic statement ORed with itself is equal to the original logic statement:

$$A + A = A$$

9. Any logic statement ORed with its complement is always true:

| COLUMNI |   | NI | 2         | 3     | 4         | 5                                            |  |  |

|---------|---|----|-----------|-------|-----------|----------------------------------------------|--|--|

| Α       | В | С  | A + B + C | Ā·Ē·Č | A · B · C | $\overline{A} + \overline{B} + \overline{C}$ |  |  |

| 0       | 0 | 0  | ī         | 1     | 1         | 1                                            |  |  |

| 0       | 0 | 1  | 0         | 0     | 1         | 1                                            |  |  |

| 0       | 1 | 0  | 0         | 0     | 1         | 1                                            |  |  |

| 0       | ı | 1  | 0         | 0     | 1         | l l                                          |  |  |

| -1      | 0 | 0  | 0         | 0     | 1         | 1                                            |  |  |

| 1       | 0 | 1  | 0         | 0     | ı         | 1                                            |  |  |

| -1      | i | 0  | 0         | 0     | 1         |                                              |  |  |

| i       | 1 | 1  | 0         | 0     | 0         | 0                                            |  |  |

Fig. 2.6 Truth table for DeMorgan's theorem using binary numbers.

$$A + \overline{A} = 1$$

Boolean algebra also follows some common mathematical laws, which can be illustrated as follows:

#### Commutative Laws

$$A \cdot B = B \cdot A$$

$$A + B = B + A$$

#### Associative Laws

$$(A \cdot B) \cdot C = A \cdot (B \cdot C)$$

$$(A + B) + C = A + (B + C)$$

#### Distributive Laws

$$A + B \cdot C = (A + B) \cdot (A + C)$$

$A \cdot (B + C) = A \cdot B + A \cdot C$

Two theorems were developed after Boole formulated his basic postulates. These theorems, developed by DeMorgan, bear his name. The DeMorgan theorems simply state that:

1. The inverse of any series of OR operations is equivalent to an identical series of inverted AND statements:

$$\overline{A + B + C} = \overline{A} \cdot \overline{B} \cdot \overline{C}$$

2. The inverse of any series of AND operations is equivalent to an identical series of inverted OR operations:

$$\overline{A \cdot B \cdot C} = \overline{A} + \overline{B} + \overline{C}$$

Let's go through the truth table for these two theorems (Fig. 2.6). When all three statements are false, the NOT-OR combination (column 2), the NOT-AND combination (column 4), and their DeMorgan equivalents (columns 3 and 5) are all true. However, for the NOR function (column 2) and its equivalent in column 3. whenever any one or more of the logic statements in column 1 are true, the outcome is false. On the other hand, the NAND function shown in column 4 (and its equivalent in column 5) remains true for all combinations of the logic statements except for the case of all three statements being true. When A, B, AND C are true, the AND function requires that the output be true; however, since a NOT operator covers the entire expression, the outcome will be opposite to that normally expected.

# Introductory Electronics and Logic Functions

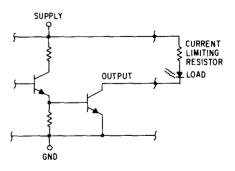

Computers are built from a wide variety of electronic components and hardware—resistors, capacitors, integrated circuits, transistors, diodes, transformers, cabinets, switches, sockets, indicators, printed circuit boards, and a multitude of other items. However, unless you are going to troubleshoot the computer when it breaks down, or you intend to build your own computer boards, you really don't have to know how the various components work. This chapter will provide a brief summary of the operation of most of the major components encountered in a computer. For detailed explanations and theoretical discussions consult Appendix A for additional reading.

Very simply, electricity is the flow of electrons from one point to another. Materials that permit an easy flow of electrons are called *conductors* and they offer a *low resistance* to the flow. Materials that totally block or tremendously impede the electron flow are called *insulators*; they offer a *high resistance* to the flow. There are also materials that fall somewhere in between the conductors and insulators; these we call *semiconductors*, and they form the basis for all solid-state circuits.

The force that moves electrons is called the electrical potential (often referred to as voltage); it is measured in units called *volts*. The flow of electrons caused by the voltage is called *current* and is measured in units called *amperes*. Opposition to the flow of current is called *resistance*; it is measured in units called *ohms*. The triad of volts, amperes, and ohms forms a simple mathematical relationship known as Ohm's law:

$voltage = current \times resistance$

Standard abbreviations for voltage, current, and resistance are as folllows:

V = volt (unit of voltage)

A = ampere (unit of current)

$\Omega$  = ohm (unit of resistance; symbolized by the capital Greek letter omega)

The basic numerical relationship between these three terms can be expressed with the help of symbols:

#### $1 V = 1 A \times 1 \Omega$

However, whenever numbers are not used, the letter E represents the voltage potential.

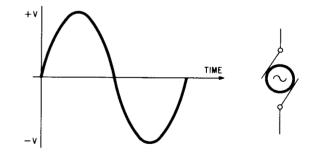

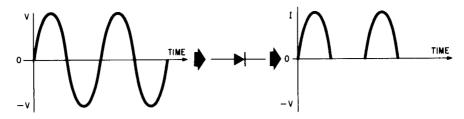

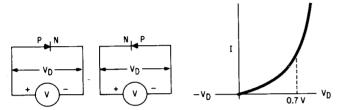

Electricity takes two forms: alternating current (ac) and direct current (dc). In your home, office, and most places of business, the power available at the wall outlet is a form of sinusoidally alternating current. The potential that forces the current to flow follows a pattern such as the one shown in Fig. 3.1. The voltage starts at a zero level, increases to a positive maximum value, then decreases through zero to a maximum negative value, and finally rises back to zero. This cyclic operation repeats many times a second and each complete variation is called a cycle. The ac power supplied in the United States provides 60 cycles every second at an average of 115 V. To measure the number of cycles per second, we use the unit Hertz (abbreviated Hz); thus the ac power is said to be 115 V, 60 Hz.

Dc voltages don't vary in cyclic patterns; they are constant. A simple example of a dc source is the com-

Fig. 3.1 Representation of an ac power source.

Fig. 3.2 A dc power source shown in graphic and schematic representations can be as simple as an ordinary flashlight battery or as complex as an entire rack of equipment.

mon flashlight battery. Its voltage remains almost constant, but slightly decreasing, as shown in Fig. 3.2 on the previous page, until the chemical processes inside the cell can't produce any more electricity. When that happens, the cell has served its useful life and is either discarded or recharged.

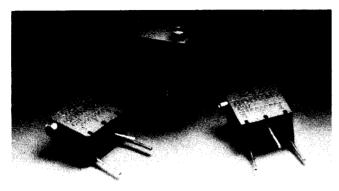

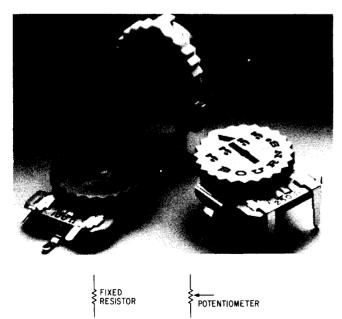

Fig. 3.3 Some typical resistors and their various schematic symbols. (Courtesy Allen-Bradley and Bournes)

#### Let's Look at the Components

Components specially designed to provide resistance, called resistors, form an important part of every electronic circuit. They are available in many different forms, in both fixed and adjustable types, as shown in Fig. 3.3. The type of resistor to be used depends on many design criteria, from resistance value to operating temperature. For many applications, low-cost resistors made from molded carbon are quite sufficient. However, when high power-handling capability or high precision is needed, more expensive metal-film or wirebound resistors are usually selected. Many resistors are often used in the same circuit, and sometimes several resistors must be combined either in series or in parallel to make a larger or smaller value. Combinations of resistors are often used to split currents and divide voltages.

Every electronic component has resistance, even conductors. Wire, for example, has a very low resistance—typically thousandths of an ohm for short lengths. And, in most cases the resistance can be ignored. But it can't be ignored in the power connections within the computer. Here, voltage losses of half a volt might occur, and that, combined with heat build-up from the power loss (I<sup>2</sup>R), can cause problems. Basically, wire resistance depends on four factors—length, material, temperature, and diameter—but is most often directly compared to diameter. The thicker the wire the lower the resistance.

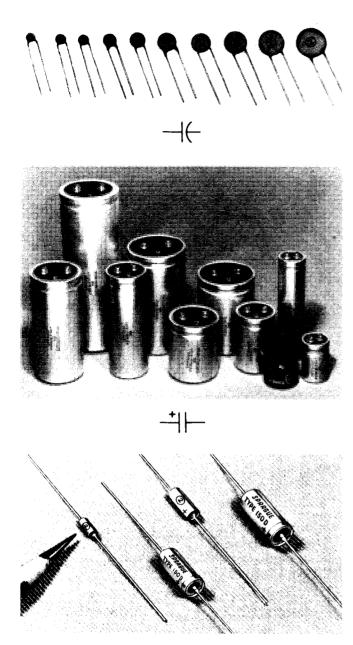

Another component often encountered is the capacitor, which is represented by the symbol shown in Fig. 3.4a; some representative samples are shown in Fig. 3.4b. The capacitor has a characteristic called capacitance, which is a sort of storage capability for electrons, and is measured in units called farads, F. Most capacitance values today are small compared to the farad, and in many cases capacitance is specified in millionths or millionth-millionths of a farad— $\mu$ F (microfarads) and pF (picofarads), respectively.

In its simplest form a capacitor consists of two closely spaced parallel conducting plates separated by some form of insulating material. The type of insulator used to separate the plates has a lot to do with the storage capacity. Commonly used insulators include ceramics, mica, glass, oil, and even waxpaper. Most small-valued capacitors (under 1  $\mu$ F) "don't care" as to the type of voltage (ac or dc) connected to them since the materials used are not sensitive to positive or negative voltages. However, larger-valued capacitors, known as electrolytics, use a special combination of materials and chemicals to obtain the high capacitance (tenths of a farad). Because of their special construction, the capacitor terminals have a fixed voltage polarity and can literally explode if polarities are not observed.

Fig. 3.4 Some typical capacitors and their schematic symbols. (Courtesy Sprague)

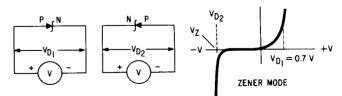

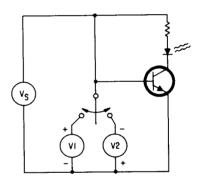

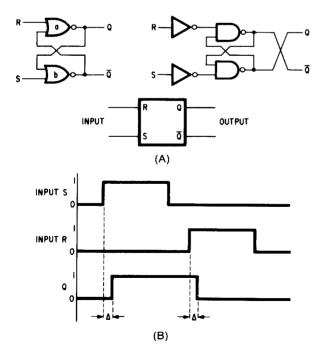

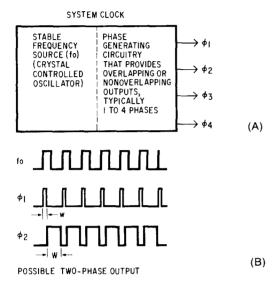

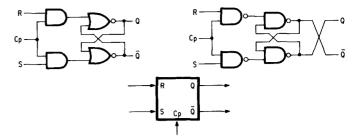

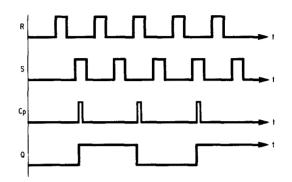

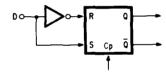

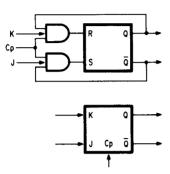

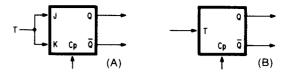

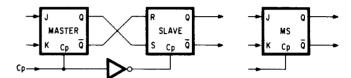

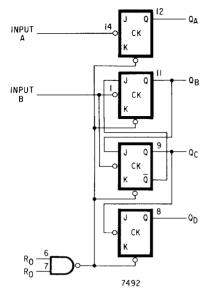

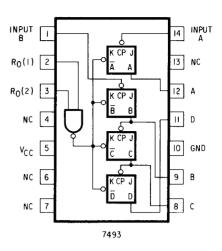

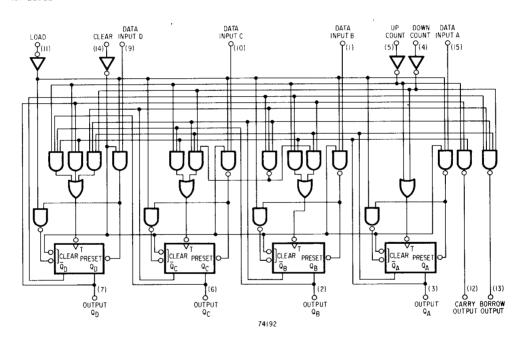

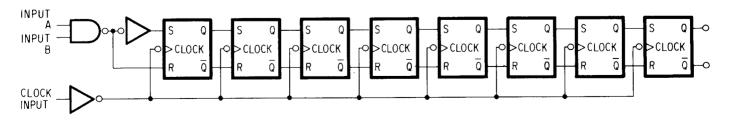

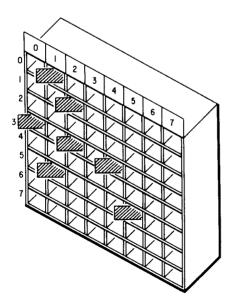

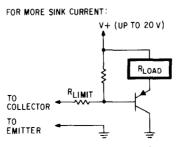

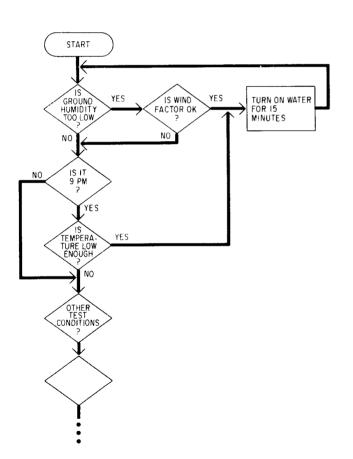

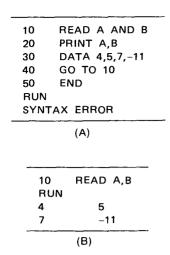

Capacitors are not only rated for their capacitance, but for their maximum operating voltage as well. Because of the nature of the materials used, the larger the capacitance value, the larger the physical size and the lower the voltage rating. A typical electrolytic capacitor used in a computer power supply might have a rating of, say 5000  $\mu$ F at 35 V and have a physical size of 5 in. long by 2 in. diameter. In contrast, a tiny disc capacitor, about 0.5 in. diameter and only 0.1 in. thick, might have a rating of 0.01  $\mu$ F at 1000 V.