# MicroMate

Technical Manual

Personal Micro Computers, Inc.

MicroMate Technical Manual

MODEL PMC-101

#### FCC WARNING

This equipment generates, uses, and can radiate radio frequency energy and if not installed, maintained, and used in accordance with instructions contained in the MicroMate manuals, may cause interference with radio communications. Equipped with a MicroMate power supply and covers, this equipment has been tested and been found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause inteference in which case the user, at his/her own expense, will be required to take whatever measures may be required to correct the interference.

#### COPYRIGHT

Copyright (c) 1983 by Personal Micro Computers. All rights reserved. No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise, without the prior written permission of Personal Micro Computers, 475 Ellis Street, Mountain View, California, 94043.

#### DISCLAIMER

Personal Micro Computers makes no representations or warranties with respect to the contents hereof and specifically disclaims any implied warranties of merchantability or fitness for any particular purpose. Further, Personal Micro Computers reserves the right to revise this publication and to make changes from time to time in the content hereof without obligation of Personal Micro Computers to notify any person of such revision or changes.

#### LIMITATION OF LIABILITY

The foregoing is in lieu of all other warranties, expressed or implied, including, but not limited to the implied warranties of merchantability and fitness for a particular purpose. In no event will Personal Micro Computers be liable for consequential damages even if it has been advised of the possibility of such damages.

#### TRADEMARKS

Zilog and Z80 are registered trademarks of Zilog Inc. MicroMate is a trademark of Personal Micro Computers, Inc.

The MicroMate Technical Manual has been prepared using the MicroMate computer and is printed in the United States of America.

First Edition: August 1983

# TABLE OF CONTENTS

# I. THEORY OF OPERATION

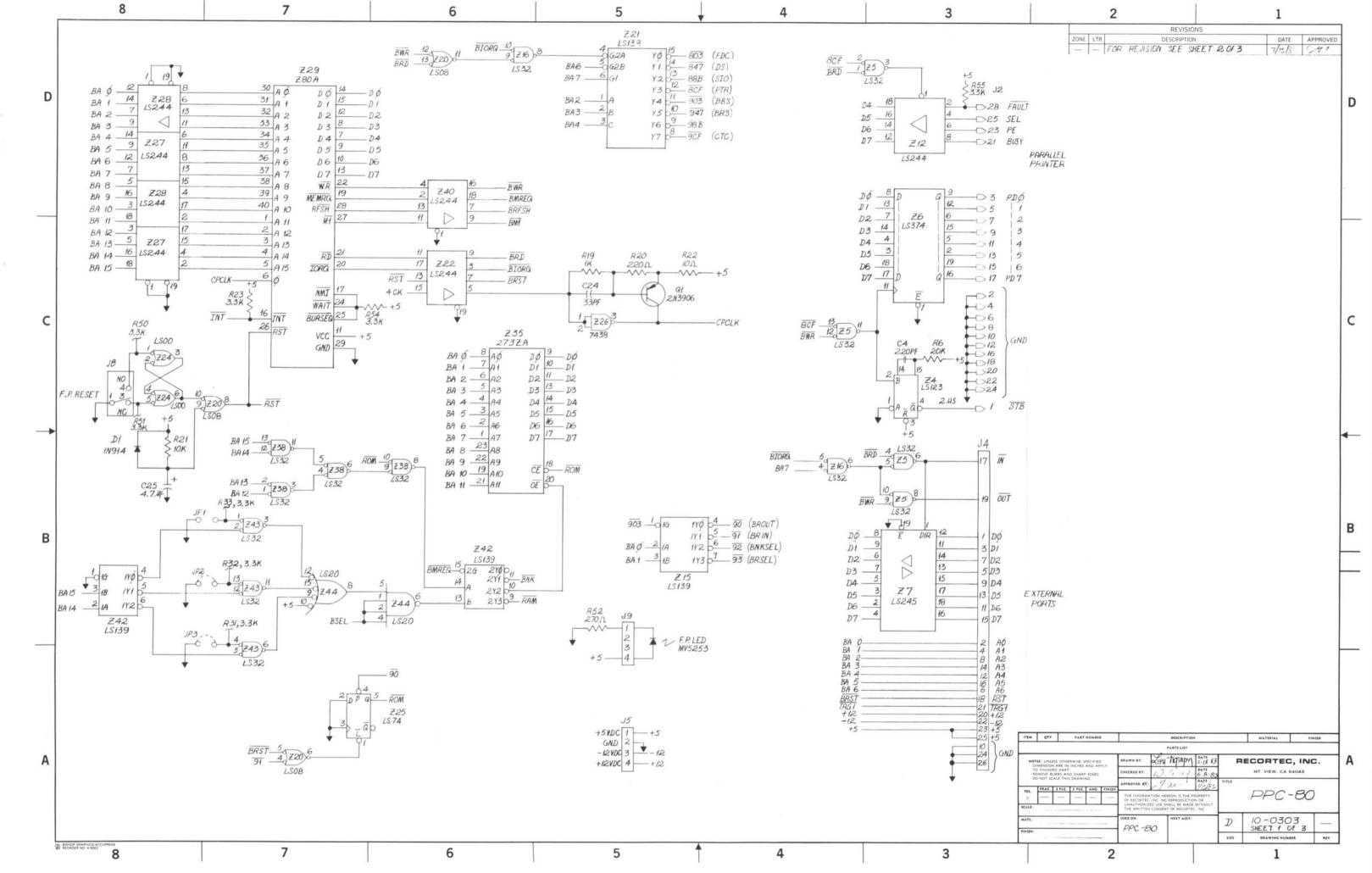

| 1.1 Sheet 1 of 3 (SCHEMATIC 10-0303)  1.1.1 CPU AND BUFFERS.  1.1.2 RESET AND CLOCK.  1.1.3 EPROM AND MEMORY DECODE.  1.1.4 I/O PORT DECODE.  1.1.5 PARALLEL PRINTER.  1.1.6 EXTERNAL PARALLEL PORTS. | 1<br>1<br>2<br>3<br>4<br>4 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 1.2 Sheet 2 of 3 (SCHEMATIC 10-0303)                                                                                                                                                                  | 5<br>5<br>6<br>7           |

| 1.3 Sheet 3 of 3 (SCHEMATIC 10-0303)                                                                                                                                                                  |                            |

| II. MEMORY MAP                                                                                                                                                                                        | 10                         |

| APPENDIX A - SUGGESTED REFERENCE MATERIAL                                                                                                                                                             | 11                         |

| APPENDIX B - SCHEMATIC DIAGRAM 10-0303                                                                                                                                                                | 13                         |

| LIST OF TABLES                                                                                                                                                                                        |                            |

| 1. ADDRESS DECODE JUMPERS 2. I/O PORT DECODER FUNCTIONS 3. I/O PORT 90 FUNCTIONS 4. EXTERNAL PORT CURRENT                                                                                             | 3                          |

| LIST OF FIGURES                                                                                                                                                                                       |                            |

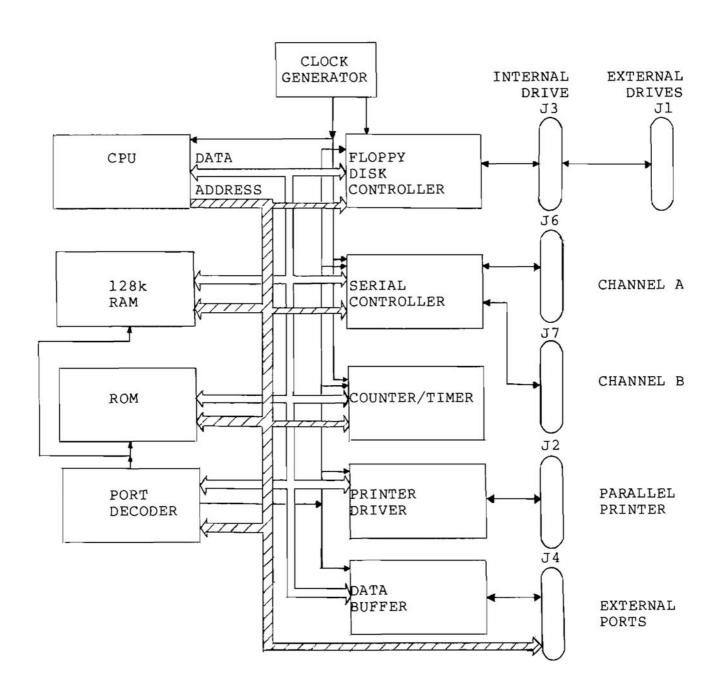

| 1. MicroMate BLOCK DIAGRAM                                                                                                                                                                            | 5                          |

FIGURE 1

MicroMate BLOCK DIAGRAM

|   |  |  |   | a. |

|---|--|--|---|----|

|   |  |  |   |    |

| * |  |  | E |    |

#### SECTION 1

## THEORY OF OPERATION

## 1.1 Sheet 1 of 3 (SCHEMATIC 10-0303)

## 1.1.1 CPU AND BUFFERS

229 is the Z80A CPU with D0 through D7 being the eight bidirectional data lines and A0 through Al5 being the sixteen address lines. The remaining lines form the various control signals. ICs Z27 and Z28 buffer the address lines from the CPU. One half of IC Z40 and one half of IC Z22 form the control line buffers.

# 1.1.2 RESET AND CLOCK

The front panel reset switch is tied to IC Z24 which forms a debounce latch. The latch output (Z24 pin 6) goes to one input of reset gate Z20. The other input to Z20 is from the power-on RC time delay circuit formed by R21 and C25. When either of these inputs to Z20 is low (ie, reset switch depressed or power-on) the output of Z20 at pin 8 goes to a low level which resets the CPU and all associated circuitry.

The system clock is derived from a 4.0 MHZ clock input to one gate of buffer IC Z22. The output of this gate (Z22 pin 5) goes to a clock driver formed by Z26, Q1 and associated components. The output of this clock driver is an NMOS compatible 4.0 MHZ clock as required by the CPU and its peripherals.

#### 1.1.3 EPROM AND MEMORY DECODE

ICs Z38, Z42, Z43 and Z44 form the memory decode section. The purpose of the memory decoder is to select the appropriate memory device (EPROM, main RAM or banked RAM) in response to the CPU address lines during a memory request. IC Z42 pins 9 (main RAM) 10 (EPROM) and 11 (banked RAM) select the device depending upon the status of input pins 13 and 14 during a memory request (pin 15).

IC 238 pin 8 (connected to 242 pin 14) is a low level when address lines 12 through 15 are low (hex addresses 0000 through 07FF) and the EPROM is enabled (238 pin 10 is at a low level).

IC Z44 pin 6 (connected to Z42 pin 13) is a low level when bank select is enabled (Z44 pins 1, 2 and 4 are at a high level) and Z44 pin 8 is at a high level. Z44 pin 8 goes to a high level in response to any of the three outputs of Z43 being low (pins 3, 6 or 11). The outputs of Z43 are conditioned by three jumpers (JP1, JP2 and JP3) and output pins 4, 5 and 6 of Z42. Z42 output pins are low in response to the state of address lines 14 and 15 from the CPU as follows:

| ADD | RESS | 242 | OUTP | UTS   | ADDRESS     | Z43    |

|-----|------|-----|------|-------|-------------|--------|

| 15  | 14   | 4   | 5    | 6     | RANGE (HEX) | JUMPER |

|     |      |     |      |       |             |        |

| 0   | 0    | 0   | 1    | 1     | 0000 - 3FFF | JPl    |

| 0   | 1    | 1   | 0    | 1     | 4000 - 7FFF | JP2    |

| 1   | 0    | 1   | 1    | 0     | 8000 - BFFF | JP3    |

| 1   | 1    |     | n    | ot us | ed          |        |

TABLE 1

The MicroMate has JP2 and JP3 installed. As can be seen from the table above, when bank select is enabled, the output at Z44 pin 6 will go low over the hex address range of 4000 to BFFF.

IC Z35 is a 32K EPROM which is enabled by Z25 pin 5 and Z42 pin 10 both being low. When Z35 is enabled it places data selected by the address lines on the data lines to be read by the CPU. Z35 is always selected after a power-on sequence or after the front panel reset button has been depressed via the reset signal to IC Z20 pin 5.

## 1.1.4 I/O PORT DECODE

ICs Z15, Z16, Z20 and Z21 form the I/O port decode section. The read and write signals from the CPU are OR'D together at Z20 pin 11 which is ANDED at Z16 pin 8 with the CPU I/O request to form one of the select inputs to IC Z21 (pin 4). The other two select inputs to Z21 are CPU addresses 6 and 7 which must be low and high respectively along with a low at pin 4 to select an I/O port. The I/O port selected is determined by CPU addresses 2, 3 and 4 on pins 1, 2 and 3 of Z21. Since CPU addresses 0 and 1 are not decoded by Z21, each I/O port selected has four addresses available for further decoding. An example of this is Z15, when pin 1 is low (from Z21 pin 11) CPU addresses 0 and 1 on pins 2 and 3 are decoded to determine which output is selected (pins 4, 5, 6 or 7).

Z21 output decoding is as follows:

| Z21 PIN | ADDRESS     | *READ/ |                        |

|---------|-------------|--------|------------------------|

| NUMBER  | RANGE (HEX) | WRITE  | FUNCTION               |

|         |             |        |                        |

| 15      | 80 THRU 83  | R/W    | FLOPPY DISK CONTROLLER |

| 14      | 84 THRU 87  | W      | FLOPPY DRIVE SELECT    |

| 13      | 88 THRU 8B  | R/W    | SERIAL INTERFACE       |

| 12      | 8C THRU 8F  | R/W    | PARALLEL PRINTER       |

| 11      | 90 THRU 93  |        | SEE Z15 DESCRIPTION    |

| 10      | 94 THRU 97  | R      | BANK/BAUD RATE STATUS  |

| 9       | 98 THRU 9B  |        | NOT USED               |

| 8       | 9C THRU 9F  | R/W    | COUNTER / TIMER        |

TABLE 2

Z15 output decoding is as follows:

| Z15 PIN |               | *READ/ |                       |

|---------|---------------|--------|-----------------------|

| NUMBER  | ADDRESS (HEX) | WRITE  | FUNCTION              |

|         |               |        |                       |

| 4       | 90            | R/W    | DISABLE EPROM         |

| 5       | 91            | R/W    | ENABLE EPROM          |

| 6       | 92            | W      | SET BANKS             |

| 7       | 93            | W      | SET SERIAL BAUD RATES |

\*note: R/W for explanatory purpose only. Outputs will select for an I/O read OR write.

## TABLE 3

Notice that CPU address 7 must be high during I/O to select Z21. This reserves the top 128 I/O ports for MicroMate use (ports 80 through FF hex).

#### 1.1.5 PARALLEL PRINTER

ICs 24, 25, 26 and 212 form the parallel printer port which is connected to card edge connector J2.

During a read from port 8C hex, IC Z12 pin 1 is enabled by IC Z5 pin 3 which places the printer status (busy, paper empty, select and fault) on data lines D7 through D4 (respectivly) allowing it to be read by the CPU.

When the CPU writes to the printer (port 8C hex) it places the data to be sent on data lines D0 through D7. At the end of the write command, IC Z5 pin ll goes from a low level to a high level which latches the data (D0 through D7) into IC Z6 and at the same time triggers one-shot IC Z4. Pin 4 of IC Z4 then goes to a low level for approximately 2 micro-seconds (pulse) which strobes the data on the output of IC Z6 into the printer.

#### 1.1.6 EXTERNAL PARALLEL PORTS

ICs Z5, Z7 and Z16 form the control for the external ports connected to J4. IC Z16 pin 6 goes low and enables the external ports during a CPU I/O request when address line 7 is low. Buffered address lines 0 through 6 are brought out to connector pins of J4 thus allowing an external device connected to these pins to decode 128 individual I/O ports (ports 00 through 7F hex).

During an I/O write to an external port, IC 25 pin 8 (J4 pin 19) goes to a low level which informs the external device connected to J4 to accept the data present at the outputs of IC 27.

During an I/O read from an external port, IC 25 pin 6 (J4 pin 17) goes to a low level which performs two functions. The first function is to change IC 27 from an output device to an input device. This action places the data lines at J4 onto the CPU data lines (D0 through D7). The second function is to inform the external device to present data (D0 through D7) to IC 27 at J4.

The external port connector (J4) outputs RESET, +5 volts, +12 volts, -12 volts and ground for external device use. The external device using the voltages should not exceed the current limits as follows:

+5 volts 1.0 amp max.

+12 volts 250 milliamps max. -12 volts 250 milliamps max.

## TABLE 4

J4 has one input signal called TRG1 (pin 21). This input is routed to one channel of the COUNTER/TIMER IC (230 sheet 2) for use as a general purpose clock or trigger input under user created program control.

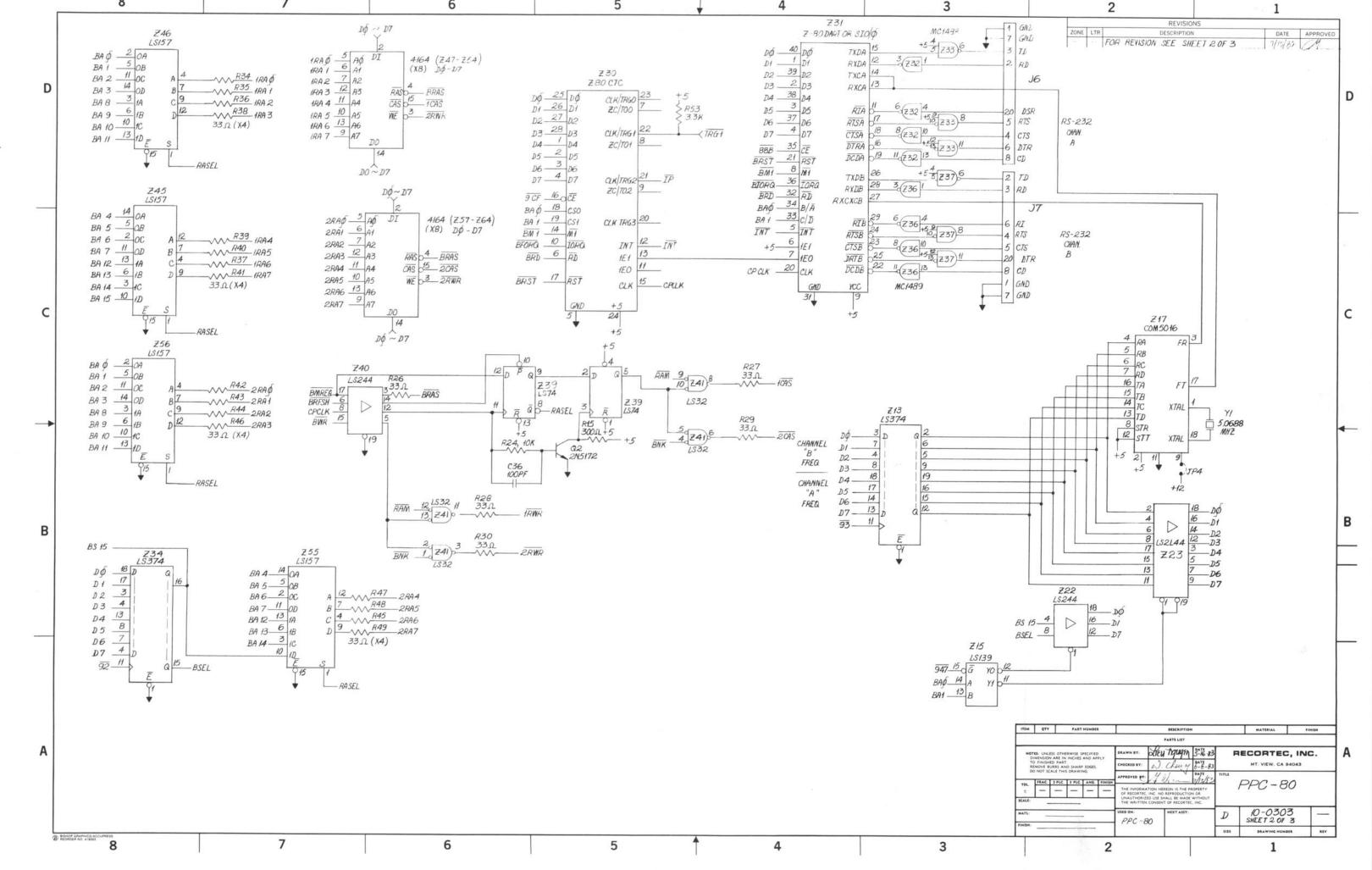

## 1.2 Sheet 2 of 3 (SCHEMATIC 10-0303)

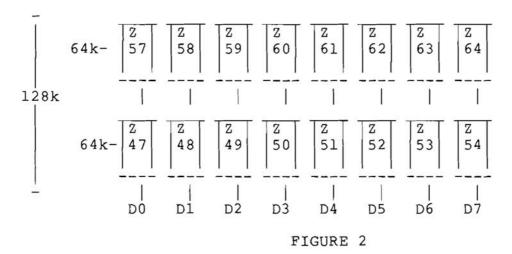

#### 1.2.1 128k RAM MEMORY

The MicroMate uses 16 64k RAM ICs (Z47 through Z54 and Z56 through Z64) arranged in two rows of 8 RAMs each to achieve 128k of total RAM memory. This arrangement is necessary as each 64k RAM IC has only one input and one output bit therefore, 8 RAMs are required to supply D0 through D7 to the CPU. The RAM arrangement is as follows:

Each 64k RAM stores data bits in a matrix of 256 rows by 256 columns. Data bits are accessed by first applying a row address and strobe followed by a column address and strobe (ie, 0.0 = bit at row 0, column 0; 1.0 = bit at row 1, column 0; etc.).

In the MicroMate the row and column addresses are generated by address multiplexers Z45 and Z46 for rams Z47 through Z54 and multiplexers Z55 and Z56 for rams Z57 through Z64. Pin 1 of each multiplexer controls which eight address lines are applied to the rams. When pin 1 is low the row address is output and when pin 1 is high the column address is output. Pin 10 of multiplexer Z55 is connected to IC Z34 pin 16. Z34 is the bank select control port (92 hex). When Z34 pin 15 is set to a high level by data bit 7 (D7) of I/O port 92, bank select is enabled. Data bit 1 (D1) of I/O port 92 then sets the state of Z34 pin 16 which controls the most significant bit of the column address for rams Z57 through Z64. This divides these 64k rams in half giving program control over which 32k section is accesed.

## 1.2.1 128k RAM MEMORY (cont)

ICs Z39, Z40 and Z41 generate the multiplexer and strobe timing. Z40 is a buffer for clock and control signals from the CPU. Upon receipt of a memory request from the CPU, Z40 pin 3 outputs the row address strobe to the ram. At the next rising edge of the buffered CPU clock from Z40, Z39 latches the state of memory request at pins 8 and 9. As memory request is an active low signal, pin 9 will go low and pin 8 will go high. 239 pin 8 going to a high level causes the address multiplexers to change from row address output to column address output. The buffered CPU clock from Z40 then gets inverted by transistor Q2 and applied to 239 pin 3. At the next rising edge of the inverted clock at pin 3, Z39 latches the state at pin 2 (from Z39 pin 9) on output pin 5. When Z39 pin 5 goes low, it is steered by the memory decoder through IC Z41 pins 6 and 8 to generate the column address strobe for the selected ram. If the memory request is a write function, Z41 steers the buffered write signal from Z40 pin 5 to the selected ram at pins 3 and 11. The CPU generates a row refresh address to insure that data is retained in the ram memory. The REFRESH signal is buffered by Z40 and applied to Z39 pin 10 which forces Z39 pin 9 to remain at a high level as long as the REFRESH signal is present. This prevents Z39 from responding to the memory request during refresh time so the multiplexer addresses are held at the row address state.

## 1.2.2 COUNTER/TIMER

IC Z30 is a four channel counter/timer that is fully under program control. CPU access to Z30 is at I/O ports 9C through 9F hex. In the MicroMate, Z30 is programmed to generate IM2 mode interrupts for the real time clock, upon a transition on pin 22 (external port trigger) and after approximately ten transitions on pin 21 (index pulses from the disk drive). The interrupt generated by pin 21 transitions will cause the disk drive motors to turn off if no further disk accesses are pending (this is done under program control). The IEI line (Z30 pin 13) is used to form an interrupt priority chain with IC Z31 for CPU interrupts.

## 1.2.3 SERIAL I/O

IC Z31 is a dual channel serial receiver/transmitter which is under program control. CPU access to Z31 is at I/O ports 88 through 8B hex. The channel A serial input, serial output and controls are through ICs Z32 and Z33 (level converters) which are connected to J6. The channel B serial input, serial output and controls are through ICs Z36 and Z37 (level converters) which are connected to J7.

The data (baud) rate of Z31 is set individually for channels A and B by the baud rate generator IC Z17. Pin 17 output of Z17 sets the channel A baud rate and pin 3 output of Z17 sets the channel B rate. The baud rates are selected at Z17 by the output of latch Z13 which is located at I/O port 93 hex. The CPU, under program control, sets the baud rates by writing data bits D0 through D7 to I/O port 93. Data bits D0 through D3 set the channel B baud rates while data bits D4 through D7 set channel A.

Port decoder IC Z15 allows the CPU to read the status of the bank select at port 94 hex through IC Z22 and to read the current baud rate setting at port 95 hex through IC Z23.

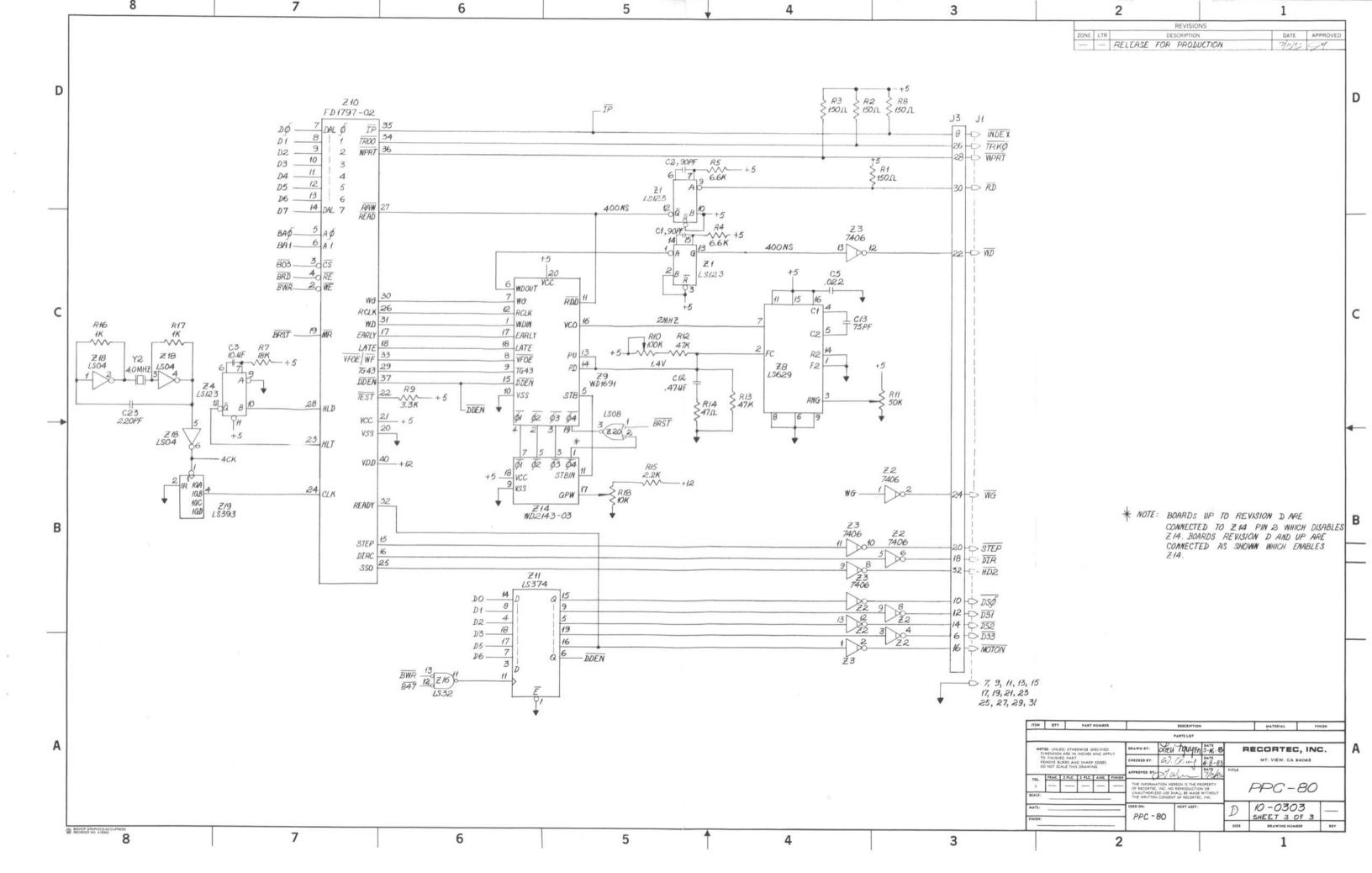

## 1.3 Sheet 3 of 3 (SCHEMATIC 10-0303)

## 1.3.1 5 1/4 INCH DISK CONTROLLER

IC Z18 and crystal Y2 form a 4.0 MHZ oscillator which supplies the clock for the CPU clock driver and, through divider IC Z19, a 1.0 MHZ clock for the disk controller IC Z10.

Z10 is a floppy disk controller interface IC which performs the data translation and timing required to allow the CPU to store and retrieve information on a 5 1/4 inch floppy disk drive. Z10 is accessed by the CPU at I/O ports 80 through 83 hex and is fully under program control.

ICs 28 (voltage controlled oscillator), Z9 (data seperator/write precompensation) and Z14 (4 phase clock generator) work in conjunction with Z10 to insure proper timing of read and write data sent to the disk drive. IC Z1 forms constant read and write pulse widths into and out of the disk drive. IC Z4 pins 10 and 12 provide a time delay to Z10 prior to all initial disk accesses to insure the disk drive is ready for operation with head(s) loaded, thus, no head load delay need be specified in software.

Three control lines from ZlO (pins 15, 16 and 25) control the disk drive head motion and side select. The outputs of IC Zll control the drive select and motor-on lines to the disk drives. Zll pin 6 output sets the desired data density (single or double) to Z9 and ZlO. Zll outputs are set through IC Zl6 pin ll by a CPU write to I/O port 84 hex.

All outputs to the disk drives connected to card edge connector Jl or internal connector J3 are through ICs Z2 and Z3. Z2 and Z3 are open collector inverters which allow up to four disk drives to be connected in parallel. The first disk drive (drive 0) is assigned to the internal MicroMate drive connected to J3. All other disk drives are connedted to J1. Only one disk drive is allowed to be active (selected) at a time to avoid conflict of data and status signals. When connecting external disk drives to J1, the proper drive select jumper must be set (1, 2 or 3) in the added disk drive. All external disk drives must have their signal and control line terminating resistors removed as the internal MicroMate disk drive contains the required terminators and double line terminations are not allowed.

There are three adjustments for the floppy disk controller that are set as follows:

Z8 VCO (set with no drive activity):

1st) Adjust R10 for 1.4 VDC at pin 2 of 28.

2nd) Adjust R11 for a frequency of 2.0 MHZ at pin 7 of Z8.

## 1.3.1 5 1/4 INCH DISK CONTROLLER (cont)

Z14 CLOCK GENERATOR (set with disk writing data to a track

number greater than 43):

Adjust R18 for the desired write precompensation value by observing the pulse width at pin 7 of Z14. The observed pulse width will be the precomp delay (typically 100 to 300 nanoseconds).

NOTE: The Z8 VCO adjustments (R10 and R11) are factory pre-set and no adjustment should be necessary. The Z14 CLOCK GENERATOR adjustment is NOT factory pre-set as the MicroMate disk drive is a 40 TRACK disk drive which does not require write precompensation.

#### SECTION 2

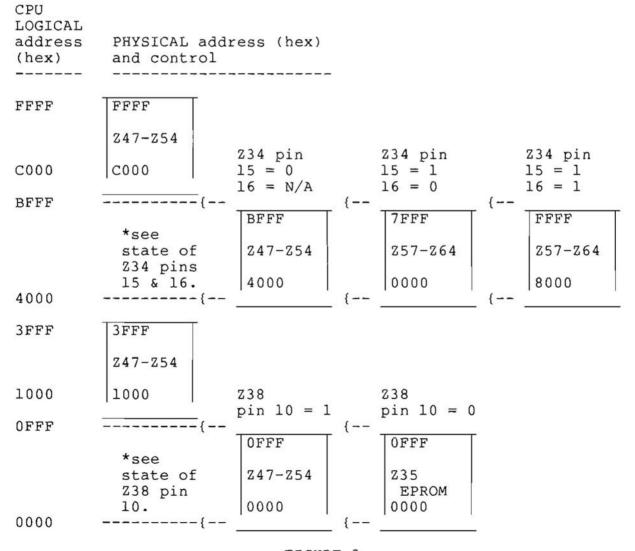

## 2.0 MEMORY MAP

The CPU has an address range of 64k, from 0000 to FFFF hex. This is reffered to as the LOGICAL address space of the CPU. The MicroMate has 128k of RAM memory and 32k (4k by 8 bits) of EPROM memory which, under program control, is mapped into the CPU's LOGICAL address space. The EPROM and each 64k row of RAM (the two rows comprising 128k total) have individual address and control signals to which they respond and are reffered to as the PHYSICAL address for each device. It is up to the program to map the correct PHYSICAL device into the CPU's LOGICAL address space. In the MicroMate, this mapping function is controlled by the operating system and is totally transparent to the user.

The memory map below shows the CPU's LOGICAL address along with each PHYSICAL device (along with the PHYSICAL address and control) which may be mapped into this space:

FIGURE 3

# APPENDIX A

# SUGGESTED REFERENCE MATERIAL-

| a) | ZILOG Technical Manuals                               | ZILOG Part Number                                    |

|----|-------------------------------------------------------|------------------------------------------------------|

|    | Z80 CPU<br>Z8430 CTC<br>Z80 SIO                       | 03-0029-01<br>03-0036-02<br>03-3033-01               |

| b) | ZILOG Product Specs.                                  | ZILOG Part Number                                    |

|    | Z8400 Z80 CPU<br>Z8430 CTC<br>Z8440 SIO<br>Z8470 DART | 00-2001-02<br>00-2041-A0<br>00-2042-A0<br>00-2044-A0 |

- c) WESTERN DIGITAL 1983 Components Handbook

- d) MicroMate User's Guide

THIS PAGE LEFT BLANK

# APPENDIX B

SCHEMATIC DIAGRAM 10-0303

|  | ž. |  |

|--|----|--|

|  |    |  |

|  |    |  |

|  |    |  |

|   | ~~ |

|---|----|

|   |    |

| • |    |

|   |    |

|   |    |

|   |    |

|   |    |

|   |    |

|   |    |

|   |    |

|   |    |

|   |    |

|   |    |

|   |    |

|   |    |

|   |    |

|   |    |

|   |    |