# DESKTOP COMPUTER SYSTEMS

# **Z-205 RAM CARD**USER'S MANUAL

Copyright 1983

Zenith Data Systems Corporation

All Rights Reserved

Printed in the

United States of America

# TABLE OF CONTENTS

| Introduction                            |

|-----------------------------------------|

| Specifications 5                        |

| Disassembly                             |

| Configuration                           |

| Installation14                          |

| Initial Tests15                         |

| Reassembly18                            |

| Theory of Operation20                   |

| Circuit Description23                   |

| In Case of Difficulty41                 |

| Replacement Parts List                  |

| Semiconductor Identification Chart      |

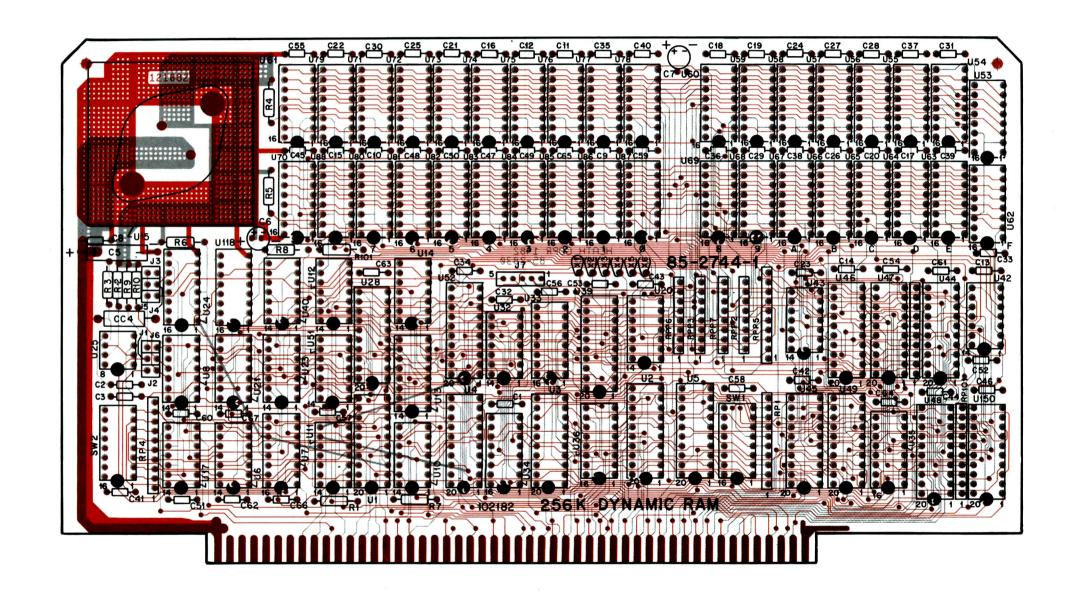

| Circuit Board X-Ray View50              |

| Appendix A: S-100 Bus Pin Definitions51 |

| Appendix B: Data Sheet, M5K4164 RAM55   |

| Schematic (fold-in)                     |

# INTRODUCTION

The Z-205 Dynamic RAM (Random Access Memory) Card gives your Z-100 Computer an additional 256K of memory. You may give your system additional RAM, up to a total system memory of 768K, by adding additional Cards. This main board must contain 192K of RAM. This Card is supplied fully populated, and may be placed in any vacant card slot in your Computer.

You can configure the RAM in many ways with the switches located on the Card. This configuration capability is especially useful if you have to troubleshoot, or configure the added memory around or in support of existing memory.

All of the information you need to use the features of the Z-205 Dynamic RAM Card is contained within this Manual. Please read it carefully before attempting to use your Z-205 Dynamic RAM Card.

# **SPECIFICATIONS**

| Memory Size        | 262,144 bytes $\times$ 9 (1-parity) in four banks of 65,536.                                                             |

|--------------------|--------------------------------------------------------------------------------------------------------------------------|

| Memory Chip Type   | $64 	extsf{K} 	imes 1$ Dynamic RAM, 5 volt single supply.                                                                |

| Addressing         | 256K contiguous address locations, configurable on 64K boundaries within 1 of 16 1-megabyte blocks.                      |

| Parity             | Byte parity for error detection.                                                                                         |

| Access Time        | 292 ns maximum using 200 ns RAM.                                                                                         |

| Width              | 256K $\times$ 8 + parity or 128K $\times$ 16 + byte parity. Automatic width selection via S-100 bus 16REQ/16ACK signals. |

| Wait States        | 0, 1, 2, or 3, user-selectable.                                                                                          |

| Bus Interface      | S-100, proposed IEEE Standard 696.                                                                                       |

| Refresh            | Transparent, onboard, independent of bus.                                                                                |

| Power Requirements | 8-11 volts DC at 1.2 A maximum.                                                                                          |

Zenith Data Systems reserves the right to discontinue products and to change specifications at any time without incurring any obligation to incoporate new features in products previously sold.

# **DISASSEMBLY**

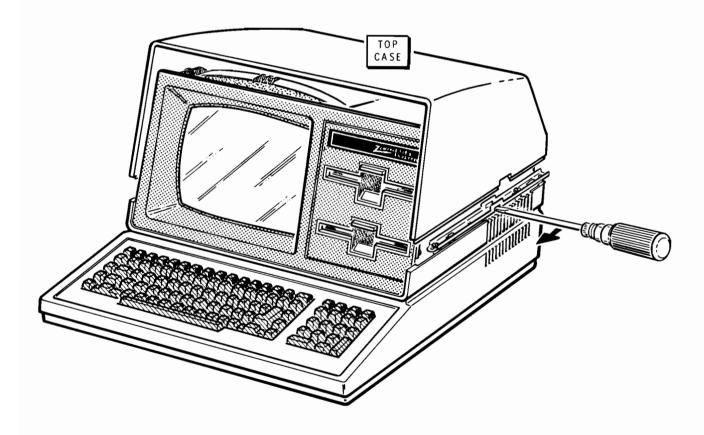

### **All-in-One Models**

WARNING: When the line cord is connected to an AC outlet, hazardous voltages can be present inside your Computer.

- ☐ Unplug the line cord from the AC outlet.

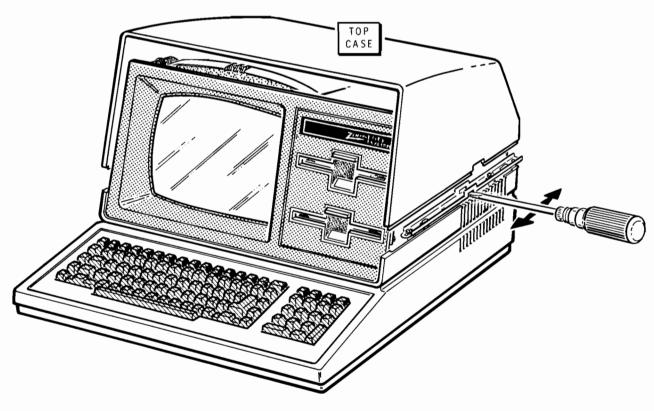

- Refer to Pictorial 1. Using a small flat-blade screwdriver, move the metal slides all the way to the front and then 1/4" to the back as shown.

- Carefully lift the top case straight up and set it to one side.

**PICTORIAL 1**

# **Low-Profile Models**

WARNING: When the line cord is connected to an AC outlet, hazardous voltages can be present inside your Computer.

- ☐ Unplug the line cord from the AC outlet.

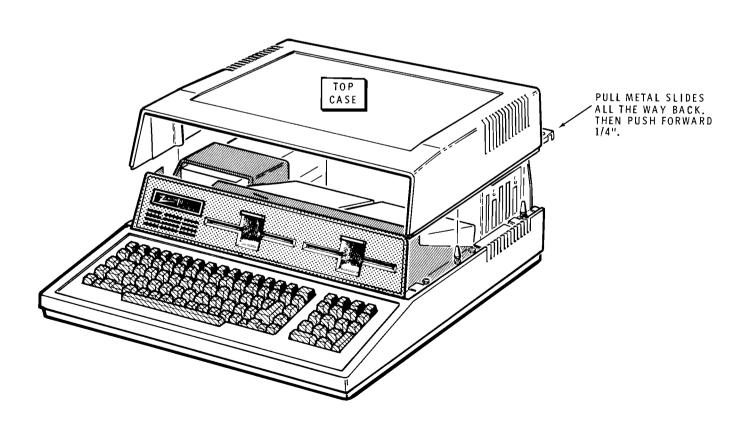

- Refer to Pictorial 2. Pull the metal slides all the way to the back, and then push 1/4" to the front as shown.

- ☐ Carefully lift the top case straight up and set it to one side.

**PICTORIAL 2**

# CONFIGURATION

# **Typical Configuration**

The following typical configuration instructions allow you to access the full 256K RAM on your Z-205 Card. Typical configuration data for H/Z-100 owners who use **more** than one Z-205 Card is found on Page 16. For special applications that require less than 256K RAM, or for system information for other than Zenith products, refer to the "Detailed Configuration Data" below.

NOTE: If you have more than one Card, repeat the following steps for each Card. Some of the jumpers and switches may already be in the correct position.

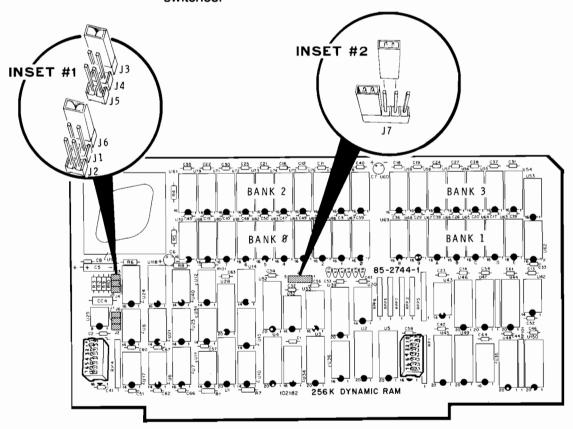

Refer to Pictorial 3 for the following steps.

| Position the Card as shown in the pictorial.                                                                             |

|--------------------------------------------------------------------------------------------------------------------------|

| Place a programming jumper on J6 (no wait states).                                                                       |

| Place programming jumpers on J7, pins 4 and 5, and on J7 pins 2 and 3 (normal operation and four banks).                 |

| Set DIP (Dual In-line Pack) switch SW1 positions 0 and 1 to the OFF (0) position, and all others to the ON (1) position. |

| Set DIP switch SW2 positions 0 and 1 to the ON (1) position, and all others to the OFF (0) position.                     |

NOTE: We assume that your H/Z-100 has the full 192K RAM installed. If it only has 128K RAM and the Z-205 Card is configured to respond to addresses in the 20000 (Hex)-5FFFF (Hex) range, it is possible to damage the mother board's data bus buffers. This will result in either an inoperative system, memory expansion, or both.

This completes the basic configuration for a Z-205 Dynamic RAM Card. Repeat these steps for each Card. Then proceed to "Installation."

# **Detailed Configuration Data**

The following information is furnished to allow purchasers of the Z-205 Dynamic RAM Card to configure the card for their non-Zenith Data System S-100 microcomputers, as well as for the Z-100 user who desires to make modifications or effect a customized configuration.

Refer to Pictorial 3 for the locations of the jumpers and switches.

Legend:

Bank 0 Banks 0,1 Used in 64K configuration. Used in 128K configuration.

Banks 0,1,2,3

Used in 256K configuration.

NOTE: It is possible to select any configuration on the fully populated board.

**PICTORIAL 3**

### CONFIGURATION

### **JUMPERS**

- J1 Open for 256K. Add programming jumper for 128K and 64K operation.

- J2 Open for 256K and 128K. Add programming jumper for 64K operation.

| <u>J1</u> | <u>J2</u> | <b>COMMENTS</b> |

|-----------|-----------|-----------------|

| 0         | O         | 256K            |

| 1         | 0         | 128K            |

| 0         | ı         | Not defined     |

| 1         | - 1       | 64K             |

NOTE: I = Installed [programming jumper used]

O = Open [programming jumper **not** used]

- J3 Add programming jumper for 3 wait states.

- J4 Add programming jumper for 2 wait states.

- J5 Add programming jumper for 1 wait state.

- J6 Add programming jumper for 0 wait state.

NOTE: You may only select **one** of the above programming jumpers. Any attempt to select more than one jumper will result in damage to U24, and a system failure.

J7 Place programming jumpers on pins 2 & 3 and 4 & 5 for normal (8-bit or 16-bit) operation for use with 128K or 256K.

Place programming jumpers on pins 1 & 2 and 3 & 4 for 64K (8-bit only with 1 bank) operation.

### **SWITCHES**

DIP switches SW1 and SW2 are used for the following purposes:

**SW1**—The Z-205 Card uses one I/O port to control and monitor the parity error circuitry. SW1, an eight-position switch, permits you to select any one of 256 possible address locations as the I/O (input/output) port address. For example, to select the address 98[HEX], you would set SW1 as shown below. NOTE: ZDS/Heath Computers use port address 98 (Hex) for the first 192K–448K, and 99 (Hex) for the second 448K–704K.

| <u>POSITION</u> | ADDRESS BIT | ON/OFF |  |

|-----------------|-------------|--------|--|

| 0               | AO          | OFF    |  |

| 1               | <b>A</b> 1  | OFF    |  |

| 2               | A2          | OFF    |  |

| 3               | <b>A3</b>   | ON     |  |

| 4               | A4          | ON     |  |

| 5               | <b>A</b> 5  | OFF    |  |

| 6               | A6          | OFF    |  |

| 7               | <b>A</b> 7  | ON     |  |

**SW2**—The Z-205 Card is addressed as a single (64K, 128K, or 256K) block of contiguous memory starting on a 64K boundary. The starting address is selected by SW2, an eight-position switch. To access the full 256K RAM, starting with address location 30000H (192K), SW2 would be set as follows:

| POSITION | ADDRESS BIT | ON/OFF |

|----------|-------------|--------|

| 0        | A16         | ON     |

| 1        | A17         | ON     |

| 2        | A18         | OFF    |

| 3        | A19         | OFF    |

| 4        | A20         | OFF    |

| 5        | A21         | OFF    |

| 6        | A22         | OFF    |

| 7        | A23         | OFF    |

### CONFIGURATION

### **INPUT/OUTPUT PORT**

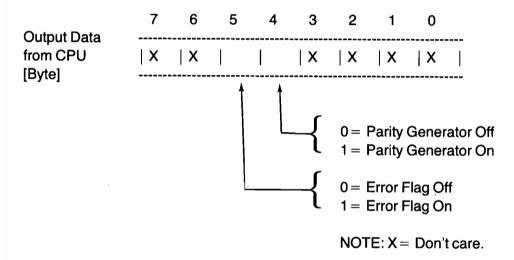

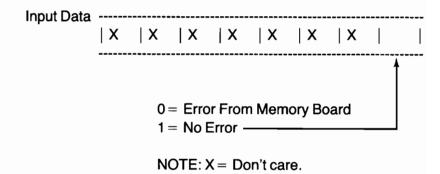

A single I/O port is used for parity control and status monitoring. The following representations show you the input data from the memory board and what information being sent as output data from the CPU will look like. Both representations are of a data byte.

# **Parity Generator**

The parity generator is an onboard circuit that writes a 1 into the parity RAM when the incoming byte has an even number of 1's. It writes a 0 into the parity RAM when the incoming byte has an odd number of 1's. You can disable this function by writing a data word with bit 4 set to 0, and outputting this byte to the I/O port.

# CONFIGURATION

### **Error Flag**

The error flag is set by onboard circuitry when the parity detected during the read cycle is even (or incorrect). To clear an error flag: output XX01XXXX and then XX11XXXX to the I/O port selected by SW1.

NOTE: On power up, the parity generator and error flag circuits are disabled. Thus, you must enable these circuits by software commands. You may enable them by writing a 1 to bits 4 and 5 and outputting the byte to the I/O port.

### **Parity Error from Memory Board**

If a parity error happens, you can determine which memory board it occurred on by inputting from the I/O port and checking bit 0. If an error occurred, bit 0 will be set to 1; if not, bit 0 will be set to 0.

# **INSTALLATION**

- NOTES: 1. If you have more than one Z-205 Card, install only one of them at this time. You will install the others after you complete the "Initial Test."

- Be sure the DIP switches (SW1 and SW2) and the programming jumpers are in the correct positions before you install the Card. See "Configuration." Page 11.

- Disconnect the 8-inch floppy drive cable from your H/Z-207 board if it has been installed. Reconnect this cable after installing your Z-205 Card(s).

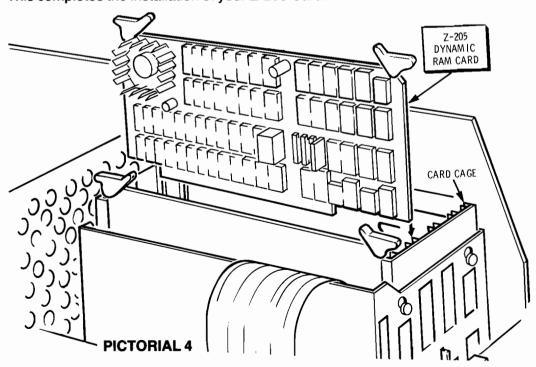

Refer to Pictorial 4 for the following steps.

- Select a vacant slot in the card cage assembly (we recommend slot 2).

- Insert the Z-205 Card with the components facing you into the vacant slot and seat it firmly by pushing straight down.

This completes the installation of your Z-205 Card.

# **INITIAL TESTS**

Use the following procedure to test your newly installed Z-205 Dynamic RAM Card. If you have purchased more than one Card:

- 1. Test each Card separately.

- After you complete the tests on the first Card, remove it from the card cage and install the second Card in its place.

- 3. Repeat the tests on this Card.

Be sure, on each Card, that the DIP switches (SW1 and SW2) and the programming jumpers are in the correct positions before you install the Card. See "Configuration," Page 11.

| Turn your Computer and monitor on.                            |  |  |

|---------------------------------------------------------------|--|--|

| At the prompt, enter the following commands exactly as shown: |  |  |

| F [your Computer will reply] FILL                             |  |  |

| FILL 3000:0-FFFF, 33 RETURN                                   |  |  |

| FILL 4000: 0-FFFF, 44 RETURN                                  |  |  |

| FILL 5000:0-FFFF, 55 RETURN                                   |  |  |

| FILL 6000:0-FFFF, 66 RETURN                                   |  |  |

# **INITIAL TESTS**

| Running the Tes | ning the To | est |

|-----------------|-------------|-----|

|-----------------|-------------|-----|

|                                 | To display the last 128 Bytes in the first 64K block enter:  DUMP 3000: FF90-000F RETURN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                 | To display the last 128 Bytes in the next 64K block enter: DUMP 4000:FF90-000F RETURN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|                                 | To display the last 128 Bytes in the next 64K block enter:  DUMP 5000:FF90-000F RETURN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                                 | To display the last 128 Bytes in the last 64K block enter:  DUMP 6000:FF90-000F RETURN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                                 | To exit this test sequence enter:   RETURN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                                 | s completes the Initial Test. Repeat these tests for each d if you have more than one.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| Z-2                             | form the following steps only if you have more than one 05 Card for your system. If you have only one card, produce of the control of the con |  |

| Final Configuration, Multi-Card |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Se                              | cond Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                                 | Set DIP switch SW2 positions 7, 4, 3, and 0 to the ON (1) position. Set all others to OFF (0).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

Install your Z-205 Cards in the vacant slots in the card cage.

### **Screen Display**

This completes the entry of the Initial Test. Pictorial 5 shows the display as the memory test is cycled\*. Your screen display should resemble the display shown in Pictorial 5. If you experience any difficulties, refer to the "In Case of Difficulty" section of this Manual.

```

3333333333333333

3333333333333333

3000: FFC0

33333333333333333

3000: FFD0

33333333333333333

3000: FFE0

3333333333333333

3000: FFF0

3333333333333333

33333333333333333

DDDDDDDDDDDDDDDD

DODDDDDDDDDDDDDDDDD

DDDDDDDDDDDDDDD

DDDDDDDDDDDDDDDD

DDDDDDDDDDDDDDD

DDDDDDDDDDDDDDD

DDDDDDDDDDDDDDD

UUUUUUUUUUUUUUUU

UUUUUUUUUUUUUUU

UUUUUUUUUUUUUUUU

UUUUUUUUUUUUUUU

(плинилинилиний)

UUUUUUUUUUUUUUU

UUUUUUUUUUUUUUU

ffffffffffffffff

ffffffffffffffff

ffffffffffffffff

ffffffffffffffff

fffffffffffffff

fffffffffffffff

```

**PICTORIAL 5**

Proceed to "Re-Assembly."

<sup>\*</sup>Only 25 lines of the display can be shown on the screen at one time.

# **REASSEMBLY**

# All-in-One

- ☐ Reconnect your 8" drive cable (if necessary).

- Refer to Pictorial 6. Replace the top case by bringing it straight down into its position and slide the latches all the way to the front.

This completes the reassembly of the All-in-One model.

**PICTORIAL 6**

# **Low Profile**

- ☐ Reconnect your 8" drive cable (if necessary).

- ☐ Refer to Pictorial 7. Replace the top case by bringing it straight down into its position. Push the latches all the way to the front.

This completes the reassembly of the Low-Profile model.

**PICTORIAL 7**

## THEORY OF OPERATION

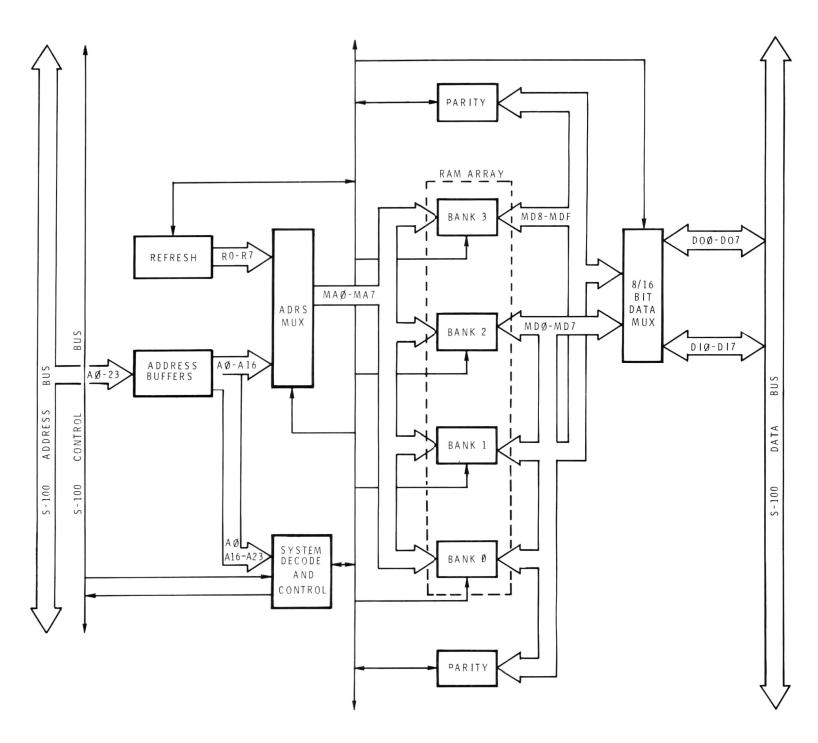

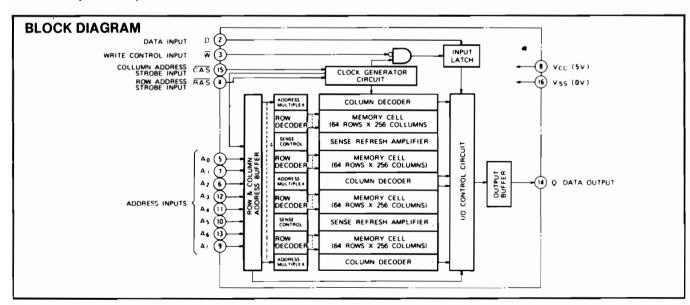

Refer to Pictorial 8, the Block Diagram, as you read the following description.

The Z-205 Dynamic RAM Card is divided into seven main sections.

The address bus buffers.

The address multiplexer (MUX).

The refresh circuit.

The system decode and control circuits.

Four banks of dynamic Random Access Memory (RAM).

The parity circuit.

The 8/16-bit data multiplexer circuit.

### **Address Bus Buffers**

The address bus buffers are bus receivers for the S-100 address and control signals.

### **Address Multiplexer (MUX)**

The address multiplexer circuit passes the eight bits of row address during the row address strobe (RAS) time, and then the eight bits of column address during the column address strobe (CAS) time. They also pass the eight-bit refresh address during memory refresh cycles.

### **Refresh Circuit**

The refresh timer circuit periodically generates a high-going edge to start the refresh process. Flip-flops are used to synchronize the refresh pulses to the bus clock and start the refresh cycle. A programmable array logic (PAL™) contains the logic to handle contention problems between normal memory accesses and refresh cycles.

PICTORIAL 8

Block Diagram of the Z-205 Dynamic RAM Card

### System Decode and Control

The system decode and control circuits contain all of the logic necessary to control normal memory accesses and I/O accesses, to perform address decoding, to generate memory array strobes, to select row and column addresses for the RAM array, to handle refresh contention, to handle parity errors, and to control the eight and 16-bit data transfers.

### **Random Access Memory Array**

The dynamic random access memory array consists of four banks of eight 64K by one bit RAM chips. The four banks are capable of storing up to 262,144 (256K) bytes of data and program instructions. To populate the RAM array, all four banks are filled with RAM chips for 256K, or bank 0 and bank 1 are filled for 128K, or bank 0 is filled for 64K. The Card is supplied fully populated.

### **Parity Circuit**

The parity circuit consists of two 9-bit parity generators/ checkers and four parity RAMs identical to the 64K dynamic RAMs used in the memory array. Each parity generator/ checker monitors an internal data bus coming from the memory array. The output of the parity generators drive the error detection circuitry in the system control portion of the board, passing parity bits to the RAMs for storage. The parity checkers test the parity bits from the parity RAMs along with the original data byte from the memory array to determine if an error has occurred.

### THEORY OF OPERATION

### 8/16-bit Data Multiplexer

The 8/16-bit data multiplexer consists of buffers and transparent latches.

Two buffers and one latch are connected to the data output lines (DO0–DO7) from the S-100 bus. The two buffers provide a path from the data output lines to either of the internal data busses, while the latch provides a path from the even-bank (bank 0 and bank 2) data bus to DO0–DO7 during a 16-bit read.

Two latches and one buffer are connected to the data input lines (DI0–DI7) on the S-100 bus. The two latches couple data from either bank of the memory array to DI0–DI7. The buffer connects DI0–DI7 to the odd bank (bank 1 and bank 3) of the memory array during 16-bit memory writes.

### **Overview**

Refer to the Schematic Diagram (fold-in) and the Block Diagram (Pictorial 8) for the following discussion.

The dynamic memory card consists of these seven major circuits:

- The memory array itself, which can be populated as a 256K, 128K, or 64K array, where K = 1024.

- The address multiplexer, used to convert the 16-bit address bus to the 8-bit address required by the dynamic random access memory (RAM).

- The board select circuitry, used to select the correct 256K, 128K, or 64K of memory within the 16M address space.

- Refresh circuits.

- Parity circuits.

- The 8/16-bit data bus which can read and write 8-bit words to an 8-bit bus master or 16-bit words to a 16-bit bus master (with 128K or 256K installed).

- The address bus buffers.

# **Dynamic RAM**

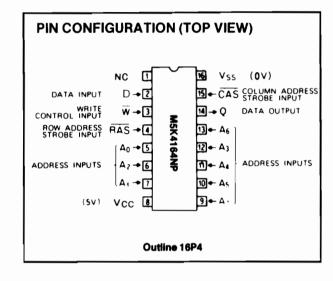

The Z-205 Card uses  $6665/M5K4164~64K \times 1$ -bit dynamic RAMs for the memory array. There is one IC per bit position, so eight ICs make up 64 kilobytes. For the first 64K bank, U87 corresponds to memory data bit 0 (MD0), and U80 corresponds to MD7 (memory data bit 7).

Refer to Pictorial 3, Page 9 for the following.

When the Card is configured for 64K, one set of RAMs make up the 64K address space:

```

U87-U80 = First 64K bank (Bank 0)

```

When the Card is configured for 128K, two sets of RAMs make up the 128K address space:

```

U87–U80 = First 64K even addressed bytes (Bank 0)

U69–U62 = First 64K odd addressed bytes (Bank 1)

```

When the Card is configured for 256K (normal configuration as supplied), four sets of RAMs make up the 256K address space:

```

U87–U80 = First 64K even addressed bytes (Bank 0)

U69–U62 = First 64K odd addressed bytes (Bank 1)

U78–U71 = Second 64K even addressed bytes (Bank 2)

U60–U53 = Second 64K odd addressed bytes (Bank 3)

```

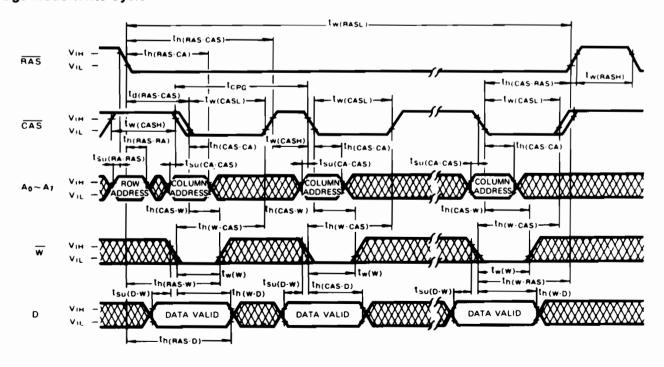

To read or write to memory, the address circuits select the correct RAM location by placing the lower eight bits of the address onto memory address bit 0 through 7 (MA0–MA7). One of the four row address strobe (RAS) lines 0–3 latches this address into the RAM bank. The upper 8-bits of the address is placed onto MA0–MA7. After waiting a short time for the lines to settle, the column address strobe (CAS) line latches the byte at MA0–MA7 into the RAM bank.

# **Address Multiplexer**

The address multiplexers consist of U33–U36. These ICs couple address bits 1 through 8 to MA0–MA7 during the RAS (row address strobe) time. They next pass, address bits 9 through 16 during CAS (column address strobe) time. They also couple the 8-bit refresh address to MA0–MA7 during refresh time.

If the Card is configured for only 64K, address bit 16 is jumpered out at J7 and replaced with address bit 0, permitting the memory array to read and write to only one bank of RAM.

### **NORMAL ACCESS**

During a normal access, when the CPU starts to access the memory and a refresh cycle is **not** occurring (RCYC="0"), the address select line SEL is logic 1. This couples the A inputs of the multiplexers to the Z outputs at MA0–MA7. U39, the RAM strobe generator, outputs a RAS (row address strobe) signal to the appropriate bank, causing the RAMs to latch in the lower eight address bits.

Later in the timing cycle, delay line output TAP1 goes from low to high, causing SEL to go high. This, in turn, passes the signals at the B inputs to the Z outputs of the multiplexers. The upper eight address bits are placed into MA0–MA7.

Next, TAP2 goes high. This causes the CAS (column address strobe) lines from U39 to be asserted, latching the upper eight address bits into the RAMs.

### REFRESH

During a refresh cycle, RCYC goes high and the 8-bit refresh address is placed onto MA0–MA7.

Later in the timing cycle, TAP1 goes high, causing all four RAS (row address strobe) lines to go active, which then latch the refresh address into the RAMs.

If a memory access is attempted during a refresh cycle, the refresh arbitration circuitry inserts a wait state until the refresh and the memory access is completed.

# Address Decode for Board Selection and I/O

### **BOARD SELECT**

The board select circuitry consists of an 8-section DIP switch (SW2), a quad exclusive OR gate (U6), a four bit full-adder (U7), and an 8-input NAND gate (U8). The upper four address bits (A20 through A23) are tested against the four most significant bits from DIP switch SW2. If A20 through A23 match SW2 bits 4 through 7, all outputs are high from the XOR (exclusive OR) gate, thus determining what 1M byte block is desired.

The decode sequence now depends on the state of address bits A16 through A19. These address bits are inverted and then fed into the adder along with bits 0 through 3 from SW2. The sum of the two sets of inputs then determines if the board is to be selected. For example, an address to be decoded is found by adding the inverse of address lines A19 through A16 to SW bits 3 through 0. If the result is x11xx (x means don't care), then the board is selected, assuming J1 and J2 are configured for 256K (both jumpers open). If 128K decoding is desired, the result of the above arithmetic must yield x11x, (J1 closed, J2 open). For 64K decoding, x1111 must result, with J1 and J2 closed. The example figures shown below explain how memory board addressing is determined:

### **Address Selection**

Switch settings for DIP switch SW2

| ADDRESS BIT | POSITION NUMBER |

|-------------|-----------------|

|             |                 |

| A23         | 7               |

| A22         | 6               |

| A21         | , 5             |

| A20         | 4               |

| A19         | 3               |

| A18         | 2               |

| A17         | 1               |

| A16         | 0               |

| SWITC          | 'H GE    |       | ıc  |                      | ADDDESSES (HEV) |               |  |

|----------------|----------|-------|-----|----------------------|-----------------|---------------|--|

| SWITCH SETTING |          |       |     | ADDRESSES (HEX)      |                 |               |  |

| SW2 PC         | OSIT     | 1 NOI | No. | MEMORY CONFIGURATION |                 |               |  |

| 3              | 2        | 1     | 0   | 256K                 | 128K            | 64K           |  |

| 0              | 0        | 0     | 0   | X00000-X3FFFF        | X00000-X1FFFF   | X00000-X0FFFF |  |

| 0              | 0        | 0     | 1   | X10000-X4FFFF        | X10000-X2FFFF   | X10000-X1FFFF |  |

| 0              | 0        | 1     | 0   | X20000-X5FFFF        | X20000-X3FFFF   | X20000-X2FFFF |  |

| 0              | 0        | 1     | 1   | X30000-X6FFFF        | X30000-X4FFFF   | X30000-X3FFFF |  |

| 0              | 1        | 0     | 0   | X40000-X7FFFF        | X40000-X5FFFF   | X40000-X4FFFF |  |

| 0              | 1        | 0     | 1   | X50000-X8FFFF        | X50000-X6FFFF   | X50000-X5FFFF |  |

| 0              | 1        | 1     | 0   | X60000-X9FFFF        | X60000-X7FFFF   | X60000-X6FFFF |  |

| 0              | 1        | 1     | 1   | X70000-XAFFFF        | X70000-X8FFFF   | X70000-X7FFFF |  |

| 1              | 0        | 0     | 0   | X80000-XBFFFF        | X80000-X9FFFF   | X80000-X8FFFF |  |

| 1              | 0        | 0     | 1   | X90000-XCFFFF        | X90000-XAFFFF   | X90000-X9FFFF |  |

| 1              | 0        | 1     | 0   | XA0000-XDFFFF        | XA0000-XBFFFF   | XA0000-XAFFFF |  |

| 1              | 0        | 1     | 1   | XB0000-XEFFFF        | XB0000-XCFFFF   | XB0000-XBFFFF |  |

| 1              | 1        | 0     | 0   | XC0000-XFFFFF        | XC0000-XDFFFF   | XC0000-XCFFFF |  |

| * 1            | 1        | 0     | 1   | XD0000-XFFFFF,       | XD0000-XEFFFF   | XD0000-XDFFFF |  |

|                |          |       |     | X00000-X0FFFF        |                 |               |  |

| 1              | 1        | 1     | 0   | XE0000-XFFFFF,       | XE0000-XFFFFF   | XE0000-XEFFFF |  |

|                |          |       |     | X00000-X1FFFF        |                 |               |  |

| 1              | 1        | 1     | 1   | XF0000-XFFFFF,       | XF0000-XFFFFF,  | XF0000-XFFFFF |  |

|                |          |       |     | X00000-X2FFFF        | X00000-X0FFFF   |               |  |

| JUMPER         | JUMPER J |       |     | OPEN                 | CLOSED          | CLOSED        |  |

| CONFIGU        | JRAT     | ION   | J2  | OPEN                 | OPEN            | CLOSED        |  |

|                |          |       | J7  | 2–3, 4–5             | 2–3, 4–5        | 1–2, 3–4      |  |

X = Determined by SW2 positions 7, 6, 5, 4 as shown:

| SW2 | POS | OITI | No. |        |

|-----|-----|------|-----|--------|

| 7   | 6   | 5    | 4   | X(HEX) |

| 0   | 0   | 0    | 0   | 0      |

| 0   | 0   | 0    | 1   | 1      |

| 0   | 0   | 1    | 0   | 2      |

| 0   | 0   | 1    | 1   | 3      |

| 0   | 1   | 0    | 0   | 4      |

| 0   | 1   | 0    | 1   | 5      |

| 0   | 1   | 1    | 0   | 6      |

| 0   | 1   | 1    | 1   | 7      |

| 1   | 0   | 0    | 0   | 8      |

| 1   | 0   | 0    | 1   | 9      |

| 1   | 0   | 1    | 0   | Α      |

| 1   | 0   | 1    | 1   | В      |

| 1   | 1   | 0    | 0   | С      |

| 1   | 1   | 0    | 1   | D      |

| 1   | 1   | 1    | 0   | E      |

| 1   | 1   | 1    | 1   | F      |

|     |     |      |     |        |

|     |     |      |     |        |

<sup>\*</sup>NOTE: Addresses selected near the "top" of a 1 M byte block wraparound.

# **Address Configuration Examples**

### Example 1

To configure your Z-205 Card for 64K operation at addresses 0B0000–0BFFFF (Hex):

| (                                                                                         |

|-------------------------------------------------------------------------------------------|

| Place programming jumpers on J1 and J2.                                                   |

| Place programming jumpers on J7 pins 1-2 and 3-4.                                         |

| Set SW2 positions 0, 1, and 3 to the ON (1) position. Set all other positions to OFF (0). |

| To  | configure your Z-205 Card for 128K operation at addresses 000–29FFFF (Hex):                                                        |

|-----|------------------------------------------------------------------------------------------------------------------------------------|

|     | Place a programming jumper on J1.                                                                                                  |

|     | Remove the programming jumper from J2 (if necessary).                                                                              |

|     | Place programming jumpers on J7 pins 2-3 and 4-5.                                                                                  |

|     | Set SW2 positions 3 and 5 to ON (1). Set all others to OFF (0).                                                                    |

| Eve | ample 2                                                                                                                            |

| То  | ample 3 configure your Z-205 Card for 256K operation at addresses 0000–CFFFFF (Hex):                                               |

| То  | configure your Z-205 Card for 256K operation at addresses                                                                          |

| То  | configure your Z-205 Card for 256K operation at addresses 0000-CFFFFF (Hex):  Remove programming jumpers from J1 and J2 (if neces- |

# **BOARD SELECT (Continued)**

When a memory address corresponds to the address space of the memory board, the board select (BSEL) line goes active, thus permitting memory accesses.

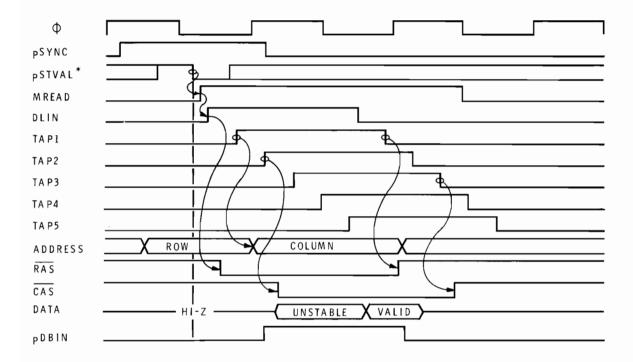

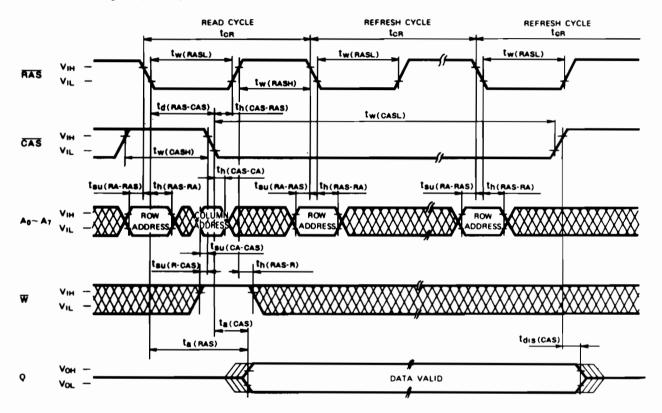

A memory read cycle is performed in the following manner:

The memory address appears at the inputs to address bus buffers U1–U4. The address is then decoded as described previously and BSEL goes active high.

Status signal sMEMR indicates a memory read is to be performed. This signal is active high and appears at U10–11 along with BSEL at U10–10 to drive the read request (RDREQ) signal active high.

The bus cycle is started when pSTVAL\* makes its high-to-low transition during pSYNC high. These signals appear at U10–1 and U10–13 respectively. The high-to-low transition of pSTVAL\* clocks the cycle control flip-flop at U13–1 and U13–13. If RDEQ is high, then the output at U13–9 goes high after the transition of pSTVAL\*, indicating the present bus cycle is for a memory read. At that time, MREAD goes high, then U12–3, then U40–3, the input to the delay line, (DLIN.) This signal, along with the outputs from the delay line, TAP1 through TAP4, is fed into the memory array strobe generator, U39. This PAL generates the appropriate RAS, SEL, and CAS signals to latch the address location into the RAM. RAS asserts when the delay line input (DLIN) and TAP1 are high. SEL asserts when TAP1 is high, and CAS asserts when TAP2 and TAP3 are high.

After CAS goes active, data from the RAM chips is stable at the data outputs after the access time delay. This data passes through one of the transparent latches at U47, U48, or U49 and is latched on the falling edge of the internally generated memory read (MREAD) signal. MREAD is returned to its inactive state by the clear memory cycle (CLRMCYC) pulse from U39–19. This signal is an active low pulse which is active when TAP1 goes low, but while TAP2 is still high. CLRMCYC is used to reset the cycle control flip-flop U13.

At this time, the data is present on the S-100 bus and is held valid until pDBIN goes inactive.

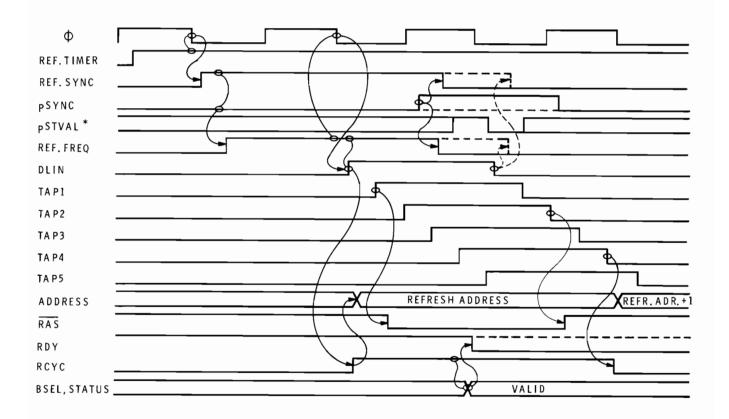

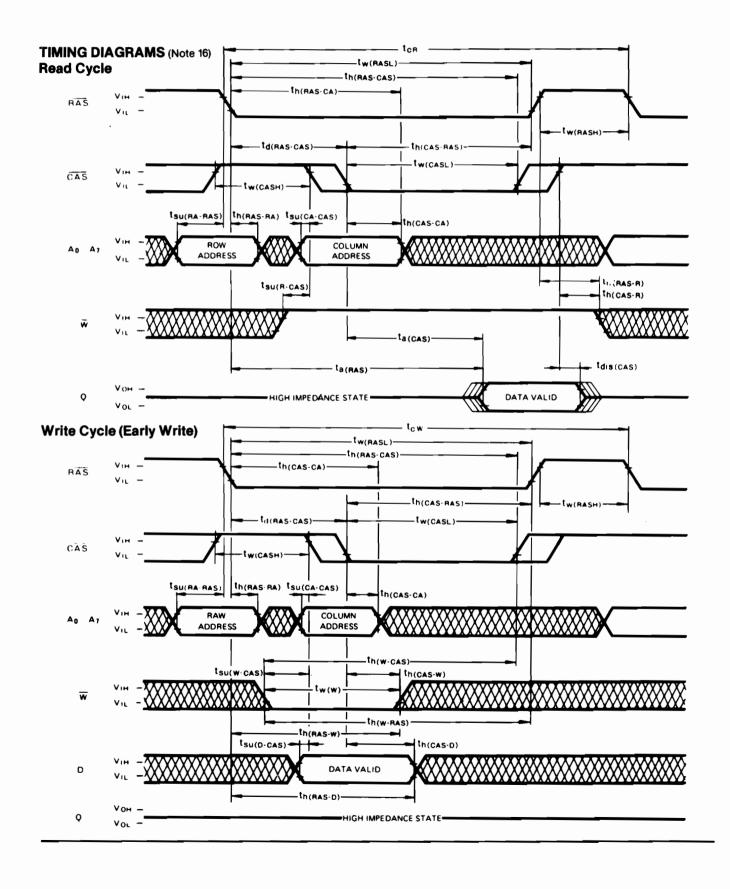

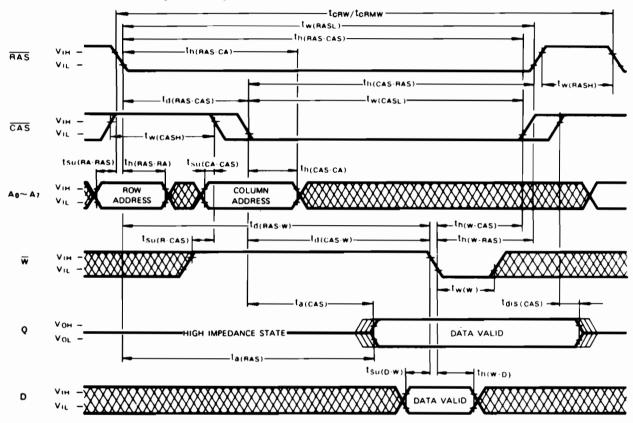

Read cycle timing in Z-100 systems.

**PICTORIAL 10**

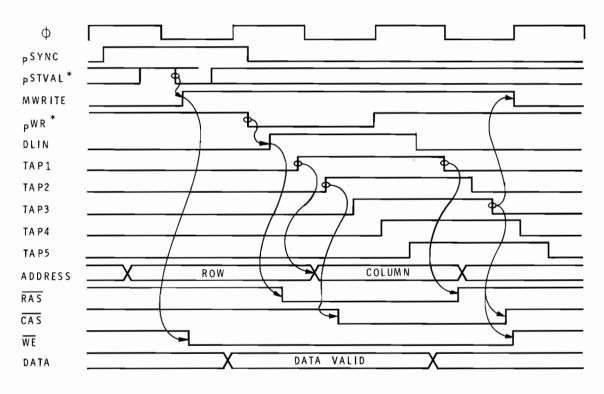

The memory write cycle is similar to the memory read cycle with the exception that when pSTVAL\* makes its transition and sets U13–5 high, the memory array is **not** accessed until pWR\* goes active, indicating that data is valid on the bus and ready to be written.

When pWR\* goes active, PWR makes a low-to-high transition, clocking U14–3 and initiating the write sequence.

Write cycle timing in Z-100 systems.

**PICTORIAL 11**

#### I/O SELECT

The I/O select circuitry consists of an eight-position DIP switch, SW1, and address comparator U5.

The positions on the DIP switch correspond to the eight least significant address lines. Address line A0 through A7 correspond to SW1 bits 0 through 7 respectively. Thus, you can select any one of 256 possible address locations as the I/O port address.

When an I/O instruction is issued by the CPU, address lines A0 through A7 are compared with the address selected by SW1 at U5. If an input instruction is being executed and if the addresses are the same, the output from U5 (DEVSEL) goes active low and the data appearing on data lines DO0–DO7 is written into U150.

If an output instruction is being executed and if the addresses are the same, the DEVSEL goes active low and the output from U118, pin 11 appears on data input line DI0.

### **Refresh Circuits**

The refresh circuits consist of a refresh clock U25, three flip-flops for synchronization and control (U23, U51, and U21), and a PAL, U28, for generating refresh request signals.

These circuits refresh the memory when the CPU is not accessing them. Sometimes a refresh is requested when the memory is being used. In this case, the refresh circuits contain arbitration logic to resolve any contentions which may arise during refresh.

Each row of the dynamic RAMs must be refreshed about every two milliseconds for 128-row devices, or about every four milliseconds for 256-row devices. Therefore, refresh clock U25 outputs a high signal every 15 microseconds to U23–3 to request a refresh. The signal is then synchronized with the falling edge of the phi clock from the bus at U51–5, and generates the refresh synchronization (REFSYNC) pulse.

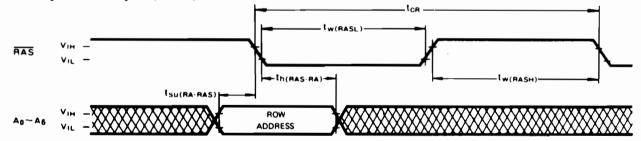

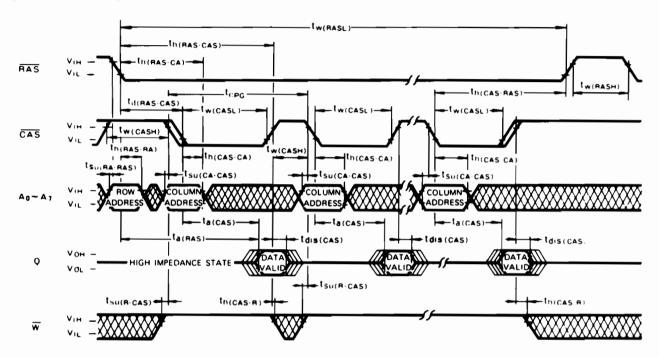

Refresh cycle timing.

**PICTORIAL 12**

#### **ARBITRATION**

The REFSYNC signal is then tested against memory read and write signals, as well as the pSYNC signal, to insure that a refresh cycle will not begin at the same time a memory cycle starts. If the conditions allow a refresh to occur, REFREQ goes active and requests a refresh at U51–12. After the next falling edge of the phi clock from the bus, the output from U51–9 is passed to delay line U20–1 via U12–13, U12–2 and U40. When the input to the delay line goes high, U21 is clocked and the output identifies the present cycle as a refresh cycle. The input to delay line (DLIN) causes the address multiplexers to pass the refresh address to the RAM array. Then TAP1 causes the refresh address to be strobed into the memories with the RAS signal present in all four banks.

As we mentioned previously, a memory refresh cycle is inhibited during pSYNC active and when a read or write cycle is being performed. If MREAD, MWRITE, or PSYNC are active at U28–1, U28–2, or U28–4, respectively, REFREQ is held low and U51–9 stays low after the clocking edge of phi passes. In this way, a refresh cycle cannot start during a memory cycle or at the same time as a memory cycle.

If a refresh cycle is in progress and the board is accessed for a read or write, the RDY line is pulled low for the duration of the refresh cycle as well as during the read or write cycle until the memory access is completed. When the RDY line is allowed to return to the high state, data which has been read will be ready on the bus, or will have been written if a write cycle was initiated.

#### **WAIT STATES DURING REFRESH**

A refresh cycle begins with RCYC becoming active. U21-10 goes low, setting U21-9 high. If a read or write cycle is occurring, RDREQ or WRREQ are high at U12-5 or U12-4. This then sets SMCYC high which, in turn, causes U17-11, RDY, to go low, and the CPU will insert wait states until the RDY line returns high. The output from U21-9 is reset to its low state when MEMWAIT, whose logic equation (MREAD + MWRITE), goes low and TAP5 returns to its inactive state, thereby clocking U21-11. This happens only at the end of a memory cycle, which assures that the data has been either read or written by the time RDY returns high.

When this board is used in systems with bus clocks in excess of 5 MHz or with fast fetch cycles, one or more wait states is required. A user-selectable wait state generator has been added to permit use of the Z-205 Card in these systems.

#### **WAIT STATES DURING NORMAL ACCESS**

One, two, or three wait states can be jump selected at J3, J4, or J5 respectively. The circuitry that performs this function consists of U24, the jumpers, and U17.

At the beginning of a bus cycle, PSYNC goes active. This resets the flip-flops inside U24, and the outputs at U24–6, U24–7, and U24–14 all go high. If the board is about to be accessed for a read or write, SMCYC at U17–10 goes high and the RDY signal goes low at U17–8. The Central Processor Unit (CPU) will then insert wait states into the bus cycle until a low level appears at U17–9. This will occur after phi clocks a low level to the selected output of U24.

### **Parity Circuit**

The parity circuit consists of U42, U43, U61, U70, U79, and U88.

This circuit maintains the parity status for each byte in the 256K of RAM. If a memory location should not match its parity bit, the parity circuit sends an error signal to the CPU. Also, a bit is set in the status latch to indicate an error. The latch can be interrogated by I/O instructions to determine which board is at fault in multiboard systems.

U61, U70, U79, and U88 are 64K by 1 bit RAMs and store one bit of parity information for each address location of RAM. These RAMs are addressed by RAS and CAS in the same way as the other RAMs. However, the write enable lines are gated through U118, so that the parity RAMs can be written to independently, and the data transfers take place through U42 and U43 instead of the data bus. U42 and U43 are 9-bit odd parity generators and even parity checkers that process and maintain the parity status.

During a memory write, the data written into RAM is present at pins 8–13 and 1–2 of U42 and U43. Pin 14 of each parity RAM is at a high impedance state so U42–4 and U43–4 are at logic 1 through pull-up resistors R4 and R5 respectively.

The following truth table shows the levels of the odd and even outputs for the number of high inputs:

| NUMBER OF INPUTS            | OUTPUTS |     |

|-----------------------------|---------|-----|

| THAT ARE HIGH.              | EVEN    | ODD |

| _                           |         |     |

| 0, 2, 4, 6, 8 (even number) | Н       | L   |

| 1, 3, 5, 7, 9 (odd number)  | L       | Н   |

So, if there is an odd number of high bits in the data byte, the logic 1 on U42–4 or U43–4 makes it even. U42–6 or U43–6 responds by going low and a logic zero is written into the addressed RAM location. Later, when that particular RAM location is read, the odd data byte is read along with the logic zero from the parity RAM and the total number of high bits still remains zero.

If there is an even number of data bits in the data byte, the logic 1 at U42–4 or U43–4 makes it odd. U42–2 or U43–6 respond, going low, and a logic 1 is coupled into the addressed RAM. Later, if that same memory location is read, the even data byte is read along with the logic 1 from the parity RAM and the total number of high bits is odd.

The parity circuit will only allow an odd number of high bits to be stored in a memory location. If an even number of high bits is read, an error has occurred.

The RAMs that store the parity bits can be enabled and disabled with the "no parity" (NOPAR) line. The NOPAR line at U118–2 is normally low. This can be brought up to high to force a parity error by disabling the parity RAM during a write sequence. Then, when the memory is read, an error will occur, provided that the byte that was written was of opposite parity to the stored parity RAM bit. You write a logic 0 to data bit D4 of the input port on the logic card to force the NOPAR line high. This feature is used to test the error-detection circuitry.

The even-parity outputs go to U12-9 and U12-10. These are coupled to U40-12. U40-13 is low except at the end of a read cycle, thus preventing a false error signal from being generated during a write or refresh cycle.

During a memory read, data output from the addressed RAMs are present at the inputs of U42 and or U43. The corresponding parity bits from U61, U70, U79, or U88 are placed on U43–4 or U42–4. If the bit pattern that was previously written into data RAM has not changed, the total number of logic 1 bits is always odd. Therefore, U42–5 and U43–5 remain low, which is the nonerror condition.

If, due to a chip failure, the bit count totals an even number, U43–5 or U42–5 go high. When the memory read cycle is nearly complete, the error enable (ERREN) line at U40–13 goes high, causing U23–11 to clock a high level out at U23–9, asserting the ERROR\* line at U17–6. This generates an error interrupt to the CPU. When KILPAR is asserted low, U23 is cleared, preventing a parity error interrupt. To assert KILPAR, set data bit D5 to zero and output it to the I/O port on the Z-205 Memory Card.

### Eight-bit and 16-bit Data Transfer Capability

The data bus buffers, U44–U49 and with data bus controllers U52, make up the data multiplexing network through which the CPU can access the RAM array in either the 8-bit bytes or the 16-bit words. The size and direction of the data transfer is controlled by a single chip, U52. This 8/16-bit data transfer controller responds to the conditions of address line A0, SIXTN\*, pDBIN, and MWRITE, the on-board memory write signal. The read and write signals, pDBIN and MWRITE, identify the direction of data flow in or out of the RAM array, respectively. The status signal, SIXTN, determines if a 16-bit data transfer is desired, and A0 determines if an odd or even byte is to be read from or written to for 8-bit transfers. If A0 is low, the byte is considered even. If A0 is high, the byte is odd.

The following table shows how U52 enables U44 through U49:

| MEMORY CYCLE TYPE | DATA BUFFER(S) ENABLED |

|-------------------|------------------------|

| Even byte read    | U47                    |

| Even byte write   | U45                    |

| Odd byte read     | U48                    |

| Odd byte write    | U44                    |

| Word read         | U48, U49               |

| Word write        | U45, U46               |

The memory array is divided into two-odd banks and two-even banks. The memory board appears as either a 256K byte card when used in an 8-bit system, or as a 128K word card when used with a 16-bit system.

Data lines DO0–DO7 (DATA0–DATA7) are connected to the inputs of U44 and U45 so that 8-bit data can be written to either the odd or even bank. U45 also provides data passage to the even bank during a 16-bit write. During a 16-bit read, data from the even bank passes through U49 and onto data lines DATA0–DATA7 (DO0–DO7).

Data lines DI0-DI7 (DATA8-DATA15) are connected to the outputs from U47 and U48 so that 8-bit data can be read from either the odd or even bank. U48 also provides data passage from the even bank during a 16-bit read. During a 16-bit write, data from DATA8-DATA15 (DI0-DI7) passes through U46 and into the even bank.

NOTE: A Z-205 Card configured for 64K (1 bank only) should not be used in a system with only 16-bit data capability. The system must use the sXTRQ\* (pin 58, S-100 Bus) line.

### **Address Line Buffers**

The address bus buffers consist of two 74S240 inverting Schottky type buffers and two 74LS244 noninverting, low-power, Schottky type buffers. These devices act as bus receivers for the S-100 address and control signals.

## IN CASE OF DIFFICULTY

The Z-205 Dyanmic RAM Card is considered to be too complex for user servicing. If your Card does not operate properly, first refer to the problem — resolution chart below. If the problem persists, return the Card to one of the repair centers listed in the documentation you received with your Z-100 Computer.

| PROBLEM                                                                                                                | RESOLUTION                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System responds with parity or bus error.                                                                              | Check switch SW1 for correct settings per the Configuration section of this manual.                                                                                                                                                                                                                                                                                                                          |

| System fails to operate.                                                                                               | <ol> <li>Check J6 and J7 for proper programming jumper installation.</li> <li>Check switches SW1, SW2 settings.</li> <li>Ensure that the Card is fully seated in the card edge connector.</li> <li>Inspect all IC packages for proper seating in sockets.</li> </ol>                                                                                                                                         |

| System fails Initial Test; Displays all "FF" in place of data shown as screen display. Display is other than expected. | <ol> <li>Check switch settings to ensure proper configuration. Code "FF" display tells you that the bank under test is not addressed or not present.</li> <li>Switch SW2, in wrong position, causing errors in display. Repeat Initial Test.</li> <li>If problem persists, return your Z-205 Card to the nearest service center with a description of the problem, and the system it was used in.</li> </ol> |

## REPLACEMENT PARTS LIST

| Circuit Comp. No.                                       | Part<br>No.                                             | Description                                                            |

|---------------------------------------------------------|---------------------------------------------------------|------------------------------------------------------------------------|

| RESISTORS                                               |                                                         |                                                                        |

| R1, R6–R8, R101<br>R2, R3<br>R4, R5, R9, R10            | 6-102-12<br>6-682-12<br>6-103-12                        | 1000 ohms<br>6800 ohms<br>10 kohms                                     |

| RP1, RP4, RP5,<br>RP101, RP102<br>RP2, RP3, RP6,<br>RP7 | 9-119<br>9-126                                          | 10 k R-pack<br>33 Ohm R-pack                                           |

| CAPACITORS                                              | 0 120                                                   | oo ommin paak                                                          |

| C1<br>C2, C3<br>C4<br>C5<br>C6, C7<br>C8–C66            | 21-769<br>21-763<br>29-44<br>25-180<br>25-820<br>21-786 | 0.01 μF<br>330 pF<br>0.001 μF<br>2.2 μF, 50 V<br>10 μF, 10 V<br>0.1 μF |

200 ns Delay line

# U20 41-10 INTEGRATED CIRCUITS

**MISCELLANEOUS**

See "Semiconductor Identification."

This section is divided into two parts. The "Component Number Index" relates circuit component numbers to Heath part numbers. The "Part Number Index" relates part numbers to manufacturers' part numbers, as well as providing lead configuration drawings for each part.

## **Component Number Index**

| CIRCUIT                                                                                             | HEATH                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COMPONENT                                                                                           | PART                                                                                                                                                                                             |

| NUMBER                                                                                              | NUMBER                                                                                                                                                                                           |

| NUMBER  U1 U2, U3 U4 U5 U6 U7 U8 U9 U10 U11 U12 U13 U14 U15 U16 U17 U18 U19 U20 U21 U22 U23 U24 U25 | 443-753 443-753 443-753 443-971 443-915 443-855 443-732 not used 443-755 443-975 443-975 443-730 442-702 not used 443-898 not used 41-10 443-900 not used 443-730 443-730 443-730 443-752 442-53 |

| U26                                                                                                 | not used                                                                                                                                                                                         |

| U27                                                                                                 | not used                                                                                                                                                                                         |

| U28                                                                                                 | 444-147                                                                                                                                                                                          |

| CIRCUIT                                                                                                              | HEATH                                                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COMPONENT                                                                                                            | PART                                                                                                                                                                                                                                |

| NUMBER                                                                                                               | NUMBER                                                                                                                                                                                                                              |

| U29 U30 U31 U32 U33–U36 U37 U38 U39 U40 U41 U42–U43 U44–U46 U47–U49 U50 U51 U52 U53–U88 U89–U117 U118 U119–U149 U150 | not used<br>not used<br>443-973<br>443-1100<br>not used<br>not used<br>444-144<br>443-976<br>not used<br>443-1001<br>443-791<br>443-1070<br>not used<br>443-730<br>444-145<br>443-970<br>not used<br>443-857<br>not used<br>443-857 |

## **Part Number Index**

| Part<br>Number | May Be<br>Replaced With | Description                             | Identification                                                            |

|----------------|-------------------------|-----------------------------------------|---------------------------------------------------------------------------|

| 442-53         | NE555                   | Timer                                   | THRESHOLD  DISCHARGE CONTROL  VOLTAGE  8 7 6 5  GND TRIGGER RESET  OUTPUT |

| 442-702        | LM323                   | Voltage regulator                       | GND WIDE SPACE                                                            |

| 443-42         | 74S112                  | Dual J-K, negative<br>trigger flip-flop | 1 2 2CK 2K 2J 2PR 2Q 16 15 14 13 12 11 10 9 9 1                           |

| 443-730        | 74LS74                  | Dual D flip-flop                        | Vcc 2 CLR 2D 2CK 2 PR 2Q 2 Q                                              |

| Part<br>Number | May Be<br>Replaced With | Description                     | Identification                                                                                                                                                                                                                                                                 |

|----------------|-------------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|