# **Technical Manual**

Hardware Z-100 Series Computers

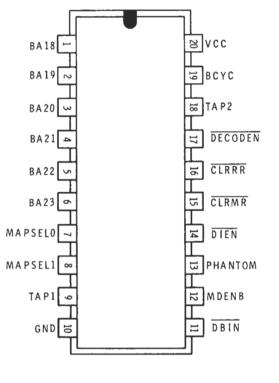

593-0038-04 CONSISTS OF

MANUAL 595-2918-04

FLYSHEET 597-2792-04

TAB SET (VOL. I) 597-3437

TAB SET (VOL. II) 597-3438

SCHEMATIC ENVELOPES 597-2918-02 MAIN BOARD SCHEMATIC 585-0018-02

VIDEO LOGIC SCHEMATIC 585-0019-01

VIDEO DEFLECTION SCHEMATIC 585-0020-01

FLOPPY CONTROLLER SCHEMATIC 585-0021-02

TM-100

# This Document was scanned and contributed by:

# Barry A. Watzman

i

This technical manual set for the H/Z-100 Series of Desktop Computers (Low-Profile and All-in-One) is divided into a number of volumes for easy handling and quick reference.

- Hardware Volumes 1 and 2 These two volumes contain disassembly information, module definitions, user options, theory of operation and programming information (of the hardware), parts lists, and schematics for your computer.

- Hardware Appendices This volume contains reprints from various manufacturers and includes the S-100 bus specifications, IC data sheets and the iAPX 88 Book. Place this last item in this binder as it includes the 8088 architecture and instruction set.

- ROM Source listings These volumes are printouts of the source code used in the various boot (monitor) ROM's that can be part of your system.

We have made every effort to give you up-to-date information in these volumes and it was considered to be correct at the time it was written. However, Zenith Data Systems Corporation may alter the products described herein from time to time and these changes may or may not be reflected in this publication. Zenith Data Systems Corporation reserves the right to make these changes without incurring any obligation to incorporated new features in products previously sold.

# CONTENTS

| Chapter 1                     |         | Information |

|-------------------------------|---------|-------------|

| Introduction                  |         |             |

| System Description            |         | 1.2         |

| Disassembly                   |         | 1.7         |

|                               |         |             |

| Chapter 2                     |         | Main Board  |

| Description                   |         |             |

| User Options and Jumpers      |         | 2.3         |

| Programming Information       |         | 2.6         |

| Theory of Operation           |         | 2.19        |

| Circuit Description           |         | 2.23        |

| Parts List                    |         | 2.92        |

| Semiconductor Identification  |         | 2.95        |

| Circuit Board X-Ray View      |         |             |

| Interconnect Pin Definitions  |         |             |

|                               |         |             |

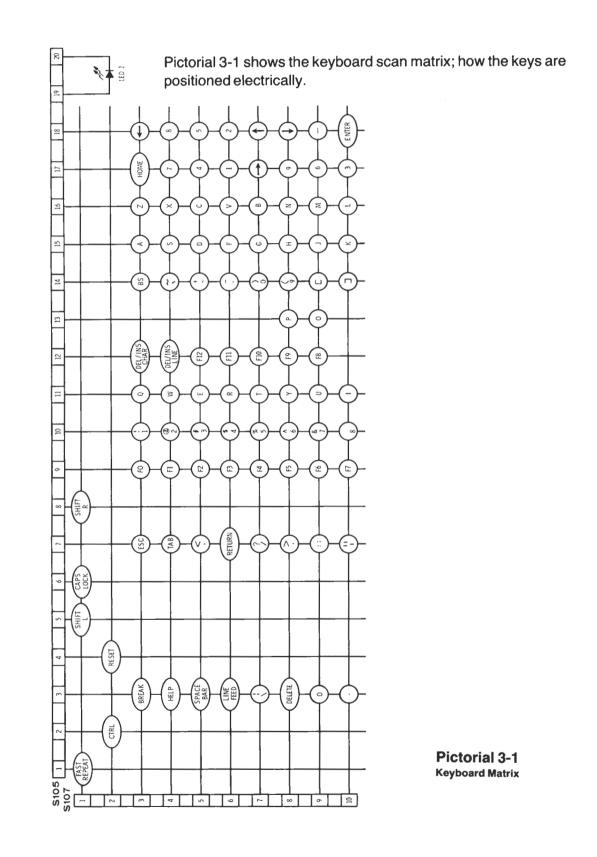

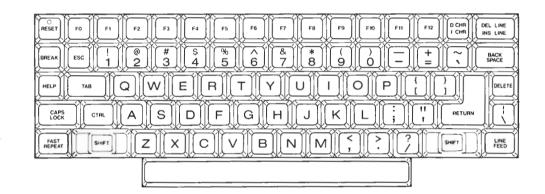

| Chapter 3                     | Keyboa  | ard Encoder |

| Description                   |         |             |

| User Options and Programming  |         | 3.3         |

| Theory of Operation           |         | 3.8         |

| Troubleshooting               |         |             |

| Keyboard Scan Matrix          |         |             |

| Encoder Output Codes          |         |             |

| Keyboard Key Layout           |         |             |

|                               |         |             |

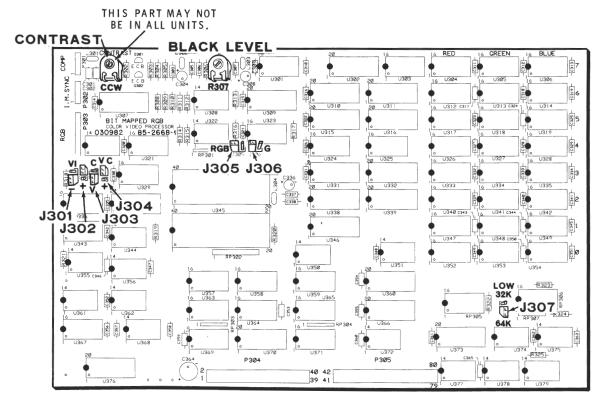

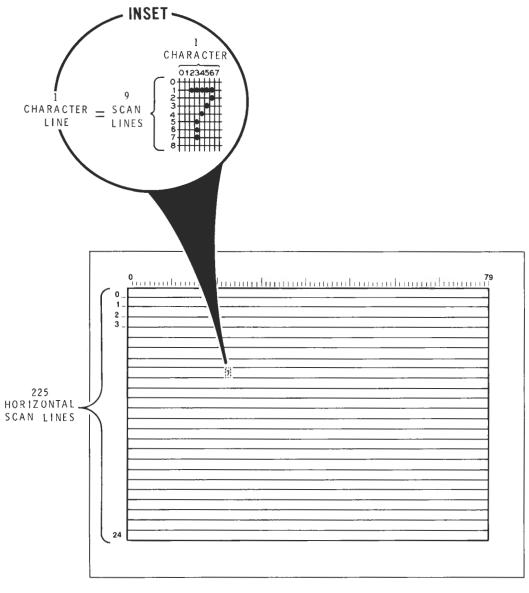

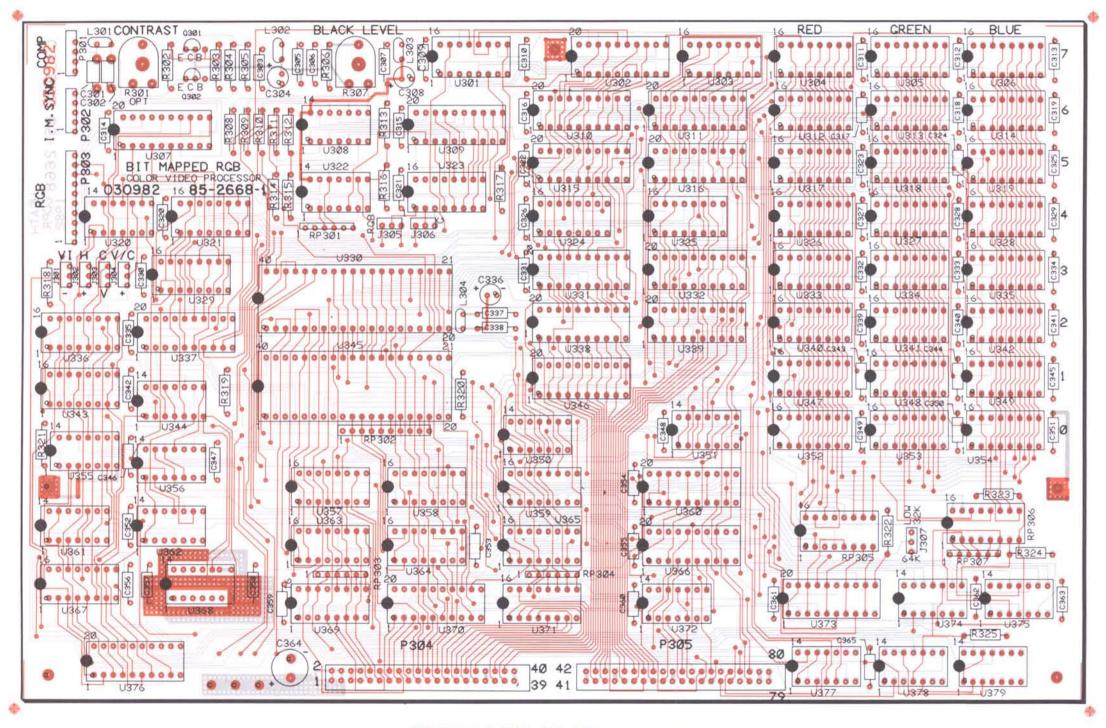

| Chapter 4                     | Video I | Logic Board |

| Description                   |         | 4.2         |

| User Options and Jumpers      |         | 4.3         |

| Theory of Operation           |         | 4.5         |

| Programming Data              |         | 4.29        |

| Circuit Description           |         |             |

| Troubleshooting               |         | 4.69        |

| Parts List                    |         | 4.70        |

| Semiconductor Indentification |         |             |

| Circuit Board X-Ray View      |         |             |

| Interconnect Pin Definitions  |         |             |

|                               |         |             |

(

#### CONTENTS

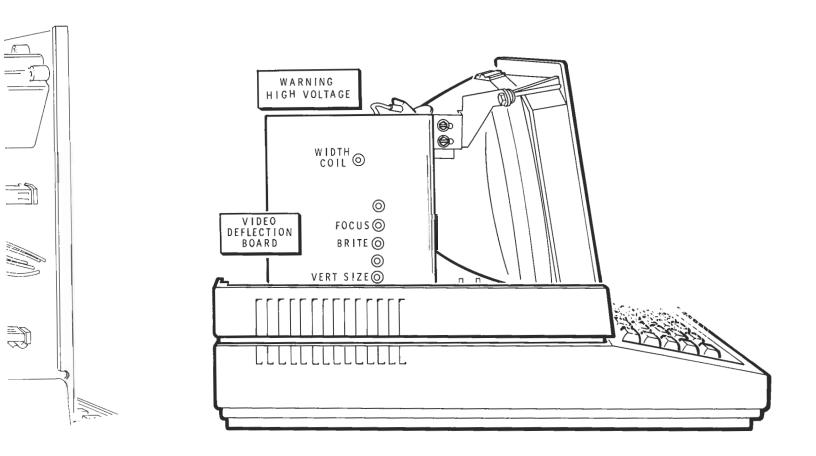

# Chapter 5Video Deflection BoardCircuit Description5.2Troubleshooting5.4Recalibration5.5Parts List5.8Circuit Board X-Ray View5.11

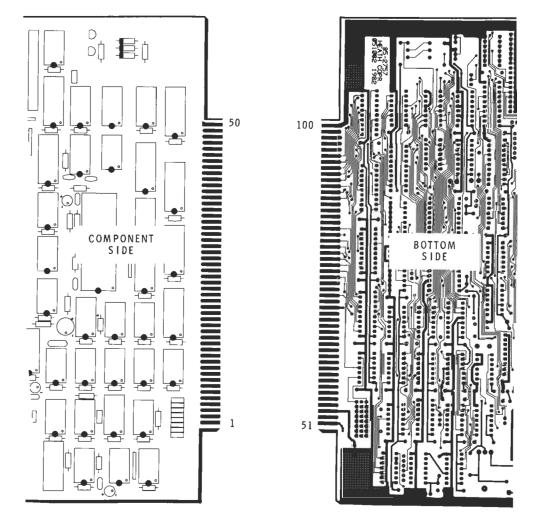

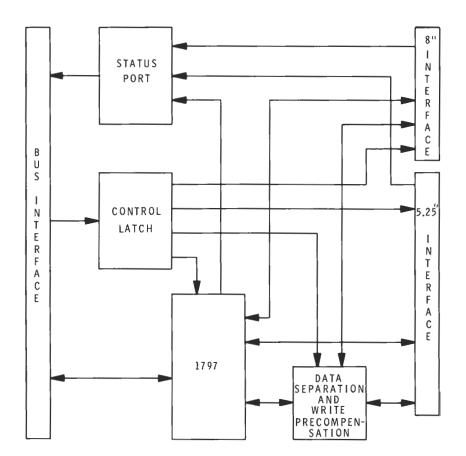

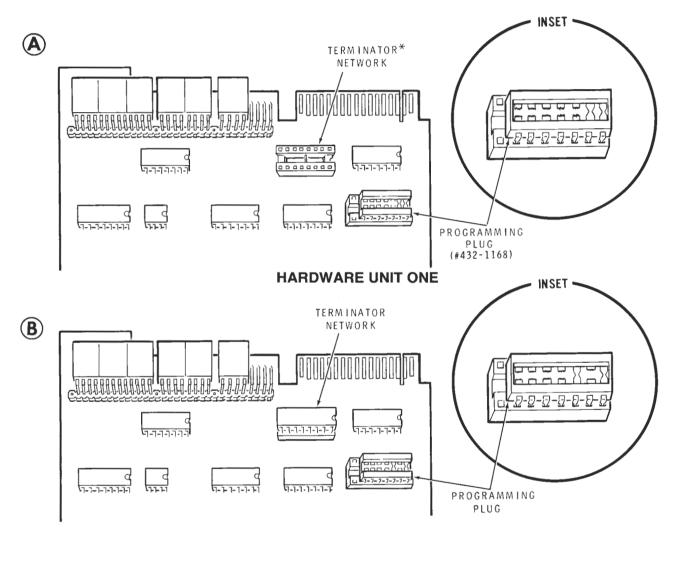

| Chapter 6                          | Floppy  | Disk | Controller |

|------------------------------------|---------|------|------------|

| Description                        |         |      | 6.2        |

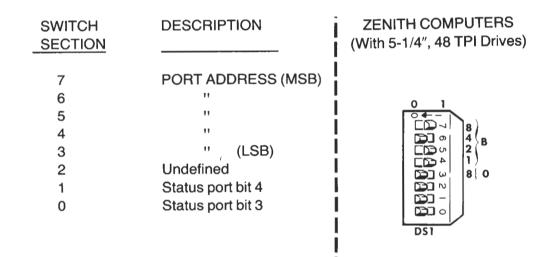

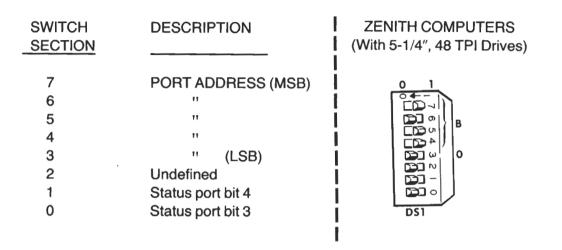

| User Options                       |         |      | 6.3        |

| Programming Data                   |         |      | 6.7        |

| Theory of Operation                |         |      | 6.21       |

| Circuit Description                |         |      | 6.23       |

| Troubleshooting                    |         |      | 6.32       |

| Calibration                        |         |      | 6.34       |

| Parts List                         |         |      | 6.38       |

| Semiconductor Identification       |         |      | 6.39       |

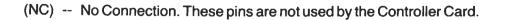

| Circuit Board X-Ray View           |         |      | 6.49       |

| Interconnect Pin and Signal Defini | tions . |      | 6.50       |

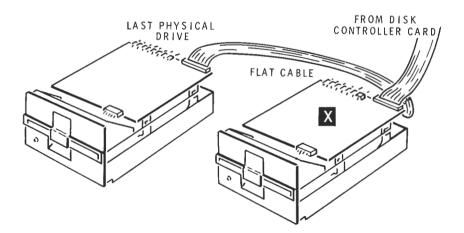

| Chapter 7         | Floppy | Disk | <b>Drives</b> |

|-------------------|--------|------|---------------|

| Description       |        |      | 7.2           |

| Programming       |        |      | 7.3           |

| Cable Connections |        |      | 7.5           |

| Operation         |        |      | 7.6           |

| Chapter 8                 | Power | Supply |

|---------------------------|-------|--------|

| Power Line Considerations |       | 8.2    |

| Specifications            |       | 8.3    |

| Chapter 9                   | Chassis, | Cabinet, | and | Cables |

|-----------------------------|----------|----------|-----|--------|

| Parts Lists                 |          |          |     | 9.2    |

| Cables Location/Description | n        |          |     | 9.12   |

| Circuit Boards & Hardware   |          |          |     | 9.17   |

# CONTENTS

| Chapter 10                          | Programming Data |

|-------------------------------------|------------------|

| Description                         | 10.2             |

| General Information                 |                  |

| Devices Permitting User Programming | 10.10            |

| Port Addresses                      |                  |

| Z-DOS Initialization Sequence       |                  |

| ASCII Chart                         |                  |

| Escape Codes                        |                  |

| Definitions                         |                  |

| Key Code Chart                      |                  |

| Keypad Code Chart                   |                  |

| Function Key Code Chart             |                  |

|                                     |                  |

#### Chapter 11

#### Addendums

Index

C

#### Chapter 1

# GENERAL INFORMATION Introduction

The Z-100 Series Desktop Computers (Low-Profile and All-in-One Models) are a series of profession computers that easily handle demanding computer tasks. Advanced state-of-the-art digital electronics and unique engineering concepts have been combined to form a truly exceptional and versatile family of computers.

Features of the Z-100 Series include:

- automatic selection on bootup of either an 8-bit processor (Intel 8085) or 16-bit processor (Intel 8088) allowing use of software for either.

- up to 3/4 megabyte of user addressable memory (RAM).

- an S-100 IEEE 696 standard bus with five slots for expansion.

- two RS-232 serial input/output ports.

- one parallel output port for Centronics-type devices.

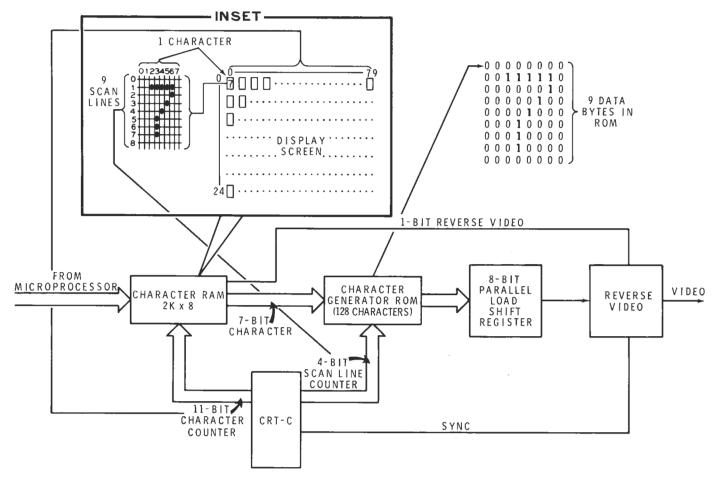

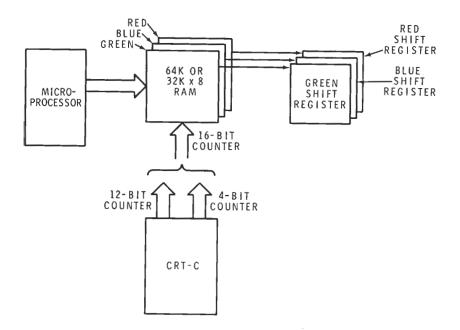

- dynamically definable character set.

- high resolution pixel oriented (bit mapped) graphics for either color (8 colors) or monochrome (8 intensity levels) displays.

- a floppy disk controller that supports both 5.25-inch and 8-inch soft-sectored disk drives (single- or double-sided, single- or double-density, and 48- or 96-tpi, 5.25-inch drives).

These features, along with Zenith's commitment to quality, will give you a high-performance, dependable computer for many years to come.

#### Page 1.2

# GENERAL INFORMATION System Description

The Z-100 Series All-in-One and Low-Profile Computers provides expandability; 8088, 8086, and 8080 code compatibility; and a 5MHz clock for computing power.

Expandability is provided through a 5-slot backplane on the main board. This allows you to expand your system with Heath/Zenith Data Systems peripherals and options or IEEE 696 standard S-100 cards from outside suppliers.

Code compatibility is provided through the use of an 8-bit processor (an Intel 8085) for 8080 code, and a 16-bit processor (an Intel 8088) for 8086 and 8088 code. The 8-bit processor allows you to use many of the large number of 8-bit code packages that run under the popular CP/M<sup>®</sup> operating system. The 16-bit processor allows you to utilize many of the 16-bit software packages that are rapidly becoming available for CP/M-86<sup>®</sup> and MS<sup>®</sup>-DOS.

The 5 MHz clock provides high performance from both the 8088 and 8085 processors and will allow you to realize higher capabilities in input/output power than previously possible on limited 8-bit systems running under slower clocks.

#### **System Modules**

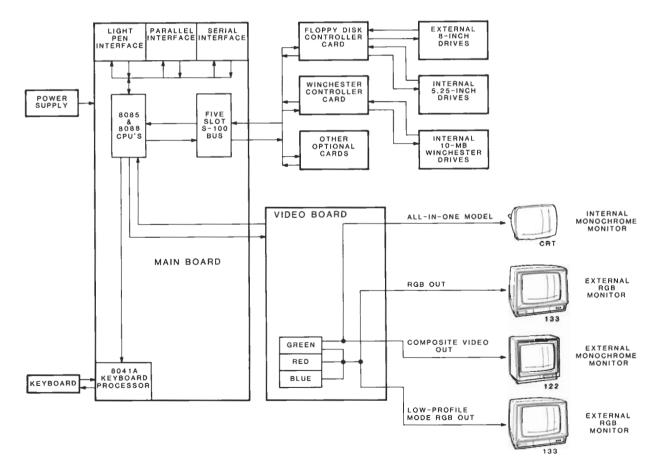

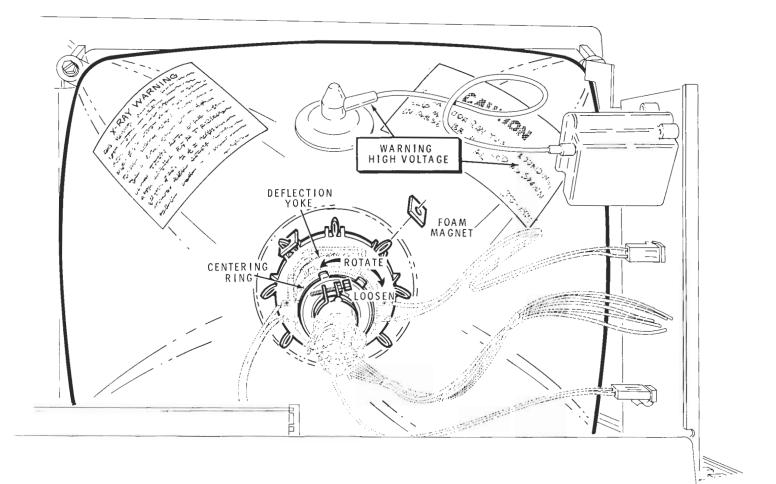

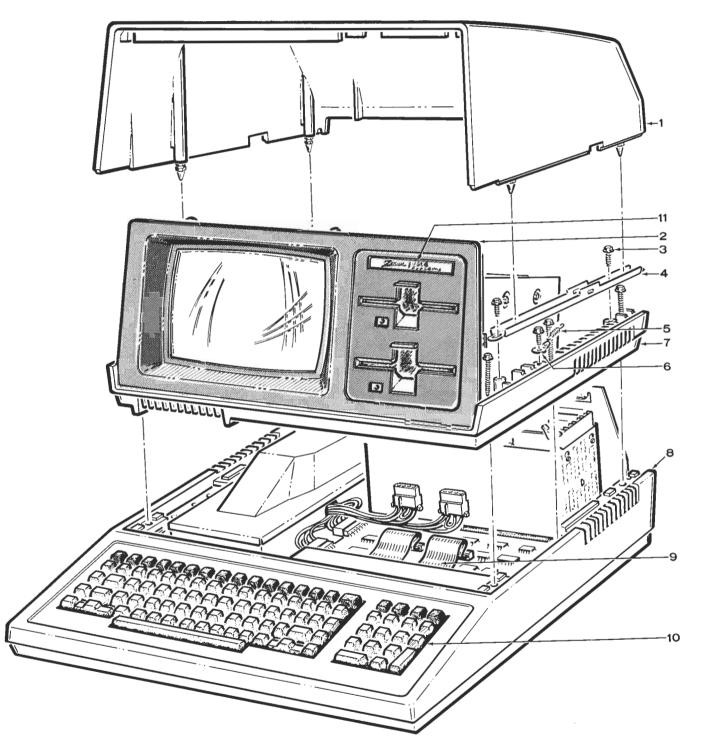

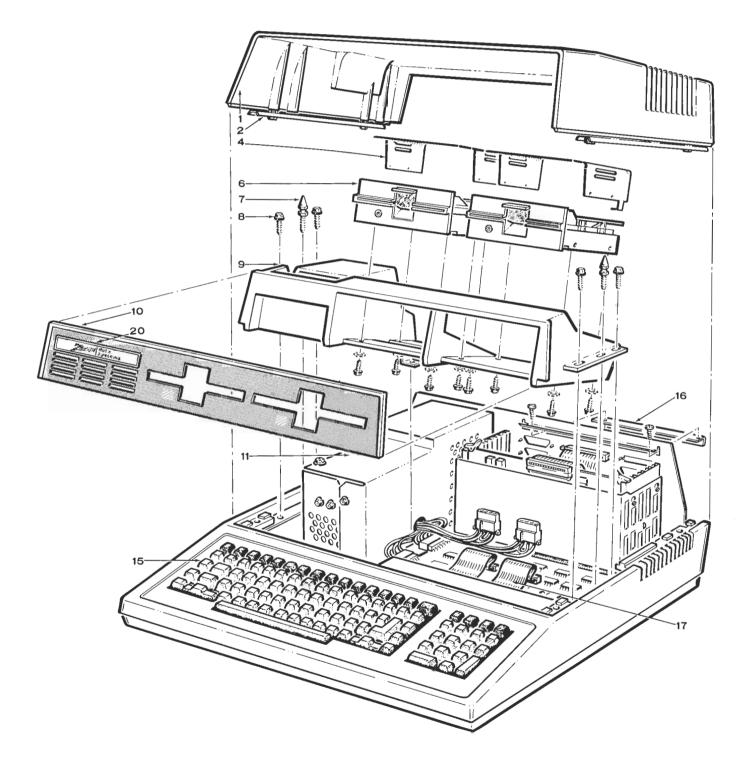

Refer to Pictorial 1-1 for the following discussion.

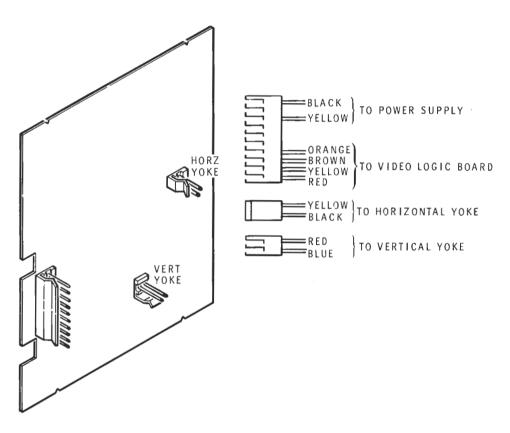

#### **Power Supply**

The power supply is an on line, switching power supply, providing +12VDC, -12VDC, +5VDC, and -5VDC. It is cooled by an internal fan and is protected from overvoltage, undervoltage, overcurrent, and overtemperature operation. This power supply is not serviceable.

Pictorial 1-1. System Block Diagram

#### **Main Board**

The main circuit board contains the two processors, an 8085 and an 8088, (CPU's—referred to as the master processors); the 5-slot backplane with an S-100 IEEE 696 bus; capacity for 3 banks of 64K devices for user memory, up to 192K; 8041A keyboard processor and connections for the keyboard; two RS-232 serial interfaces and connectors, one parallel interface and connector, and interface with the video board.

The CPU's control the timing, addressing, and generation of control signals for the computer. In addition, switches and jumpers on the main board control autobooting, vertical scan frequency, interfacing for the serial ports, and PROM size (8, 16, or  $32K \times 8$ ).

Temporary master processors on cards plugged into the backplane slots can directly access the memory and peripheral ports of the system. They cannot, however, access the interrupt controllers for the two master processors, the high order address latch, or the processor swap port (these can only be accessed by the master processors on the main board — the 8085 and 8088).

128K of user memory on the main board is supplied in the standard configuration, however 192K is supplied for some systems, which is required for Winchester operation and some application packages. Associated circuitry provides parity checking and refresh cycles.

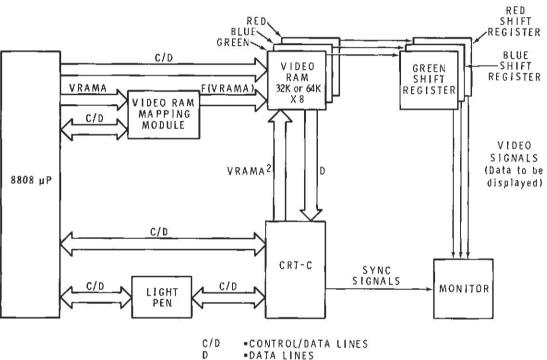

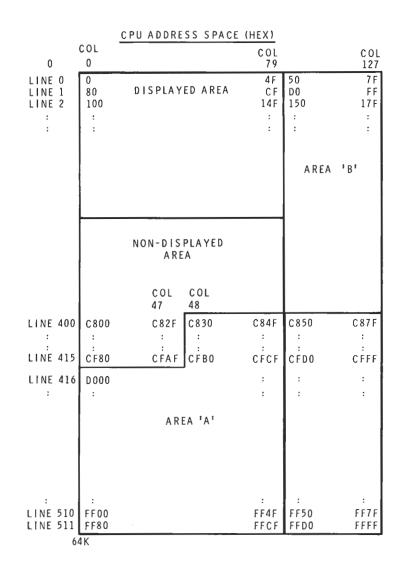

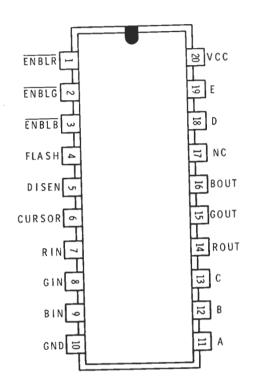

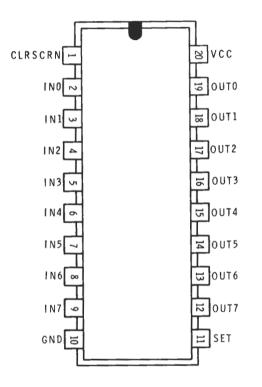

#### Video Circuit Board

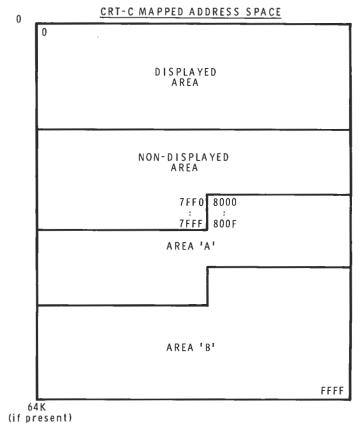

The Z-100 series computers support a powerful bit-mapped video system, requiring a minimum of one bank of 32K for video memory. The video circuit board has the capacity for up to three banks (one each for red, green, and blue) of 32K or 64K memory devices. The video board interfaces with the main board and contains the CRT controller (CRTC) and output facilities for both composite monochrome monitors and RGB color monitors.

Jumpers provide flexibility in selecting memory device types, although they may not be mixed, and RGB or monochrome operation. In addition, if 32K of 64K devices are used, the board has provisions for addressing the upper or lower 32K.

The video board is directly accessible from the S-100 bus and may controlled by either temporary or master processors. The CRTC, video control bits, and video RAM are all accessible from the S-100 bus and are compatible with it. However, the board is not an S-100 board and does not meet S-100 standards for signal interfacing or power supply requirements.

#### **Floppy Disk Controller**

The floppy disk controller is on a card that occupies one of the five S-100 slots. It conforms to IEEE-696 standards for S-100 cards and provides the necessary read/write and control signals for up to four 5.25-inch and four 8-inch floppy disk drives. Drive types may be mixed and are dependent upon the operating system for control. Note: Standard Z-DOS, CP/M-85, and CP/M-86 operating systems, as supported by Zenith Data Systems, are configured to support only two of each drive size. If additional drives are required, the operating systems will have to be modified by the user.

#### Winchester Disk Controller

The optional Winchester disk controller is on a card that also occupies one of the five S-100 slots. It conforms to IEEE 696 standards for S-100 cards. The data separator for the Winchester system is on a separate circuit board and is mounted on the Winchester disk drive itself. The two cards provide the necessary read/write and control signals for up to two Winchester drives. Note that Zenith Data Systems supports operating system software for only one Winchester drive at this time for single user installations.

#### **Other Options**

Other optional S-100 cards are available from Zenith Data Systems. They include the NET-100 Z-LAN<sup>®</sup> network card and interface software, the Z-204 multiport input/output card (available with or without ring detect), and the Z-205 memory card (with a capacity for 256K additional RAM memory).

In addition, cards from other suppliers may be added that are IEEE 696-compatible. Note that neither Zenith Data Systems nor Heath support nor recommend the use of any of these cards.

Page 1.7

### **GENERAL INFORMATION**

#### **Disassembly**

There are a number of versions of both the Low-Profile and All-in-One Z-100 Series available. The variations in the configurations are limited to 5.25-inch drive size (both full-sized and half-height versions are available) and whether or not the optional Winchester disk system is installed in the computer.

In addition, optional cards can be added to accommodate additional memory, additional input/output ports, and the Zenith Local Area Network (Z-LAN).

When you are disassembling your system, keep in mind there various options and if installed, draw a chart of the cable connections of the S-100 cards in your particular system.

**NOTE:** If you have a Winchester system, make sure that the drive is in the SHIP position. See your *Z-100 User's Manual Winchester Supplement* for instructions.

#### **Cabinet Removal**

Before proceeding with disassembly, disconnect all line cords to your computer and its peripherals.

#### Disassembly

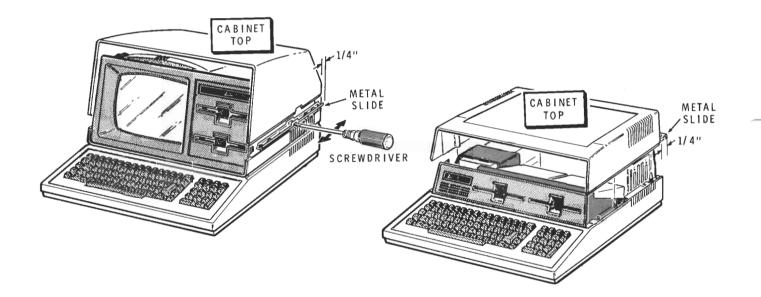

Refer to Pictorial 1-2 and move the metal slides to the rear approximately 1/4-inch as shown. Carefully lift off the cabinet top and set it to one side. (On the All-in-One models, you will have to use a flat-bladed screwdriver as illustrated in the pictorial.

**Pictorial 1-2. Cabinet Removal**

# GENERAL INFORMATION Disassembly

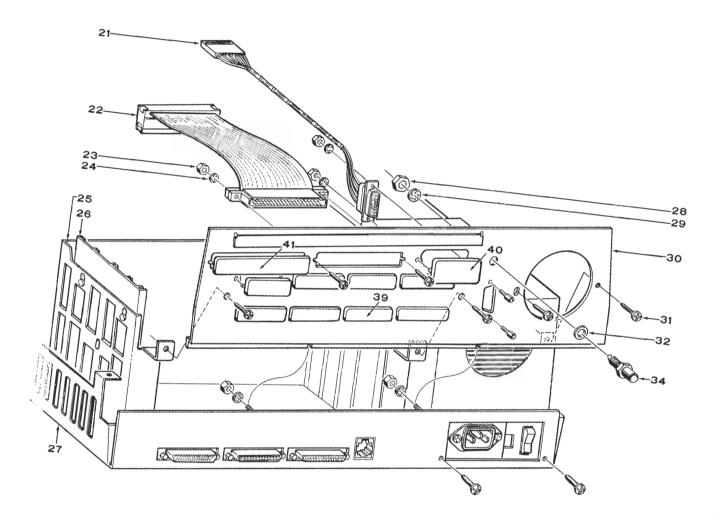

#### **Card Removal**

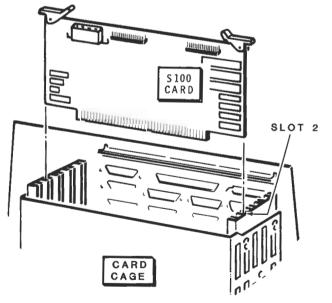

Refer to Pictorial 1-3. The various cards in your computer can be removed as your needs dictate. However, be aware that you will occasionally have to remove cables from several different cards to remove one card.

For instance, if you want to remove the floppy disk controller card and you have a Winchester card installed *to the back of it* (as viewed from the front of the computer, you will have to remove the cables going from the Winchester card to the drive. Likewise, if you are removing the Winchester controller card (for installation of the jumper for PREP operation), you may have to remove one of the two cables going from the floppy disk controller card.

Cards may be removed by simultaneously pivoting up both of the card lifters as illustrated in the pictorial, unplugging any cables (including those that may be routed over the card you are removing), and then lifting the card up out of the computer.

**Pictorial 1-3. Card Removal**

#### Disassembly

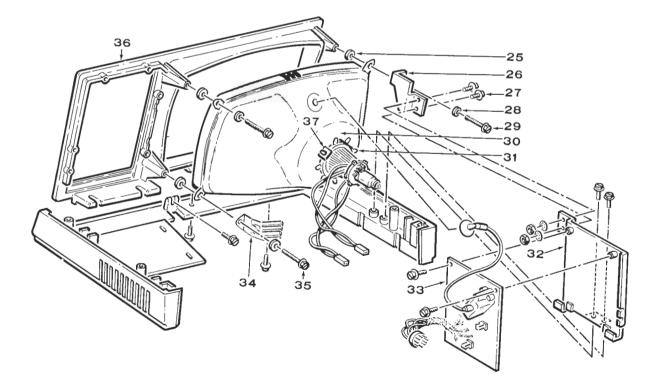

# Display and Disk Drive Assembly (All-in-One Computer)

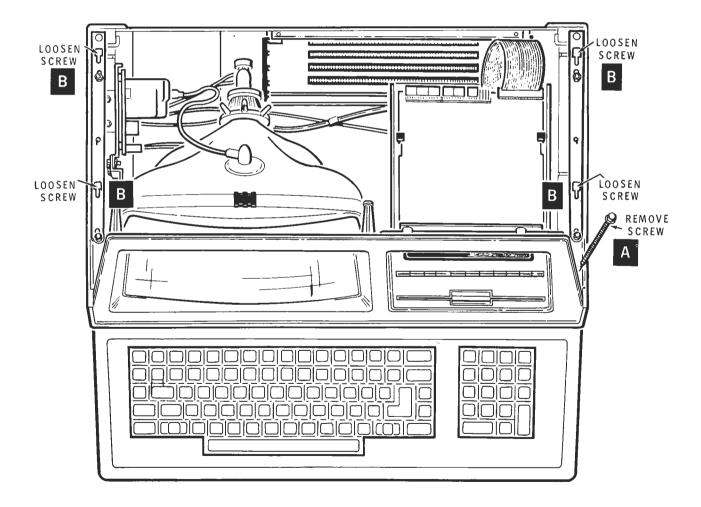

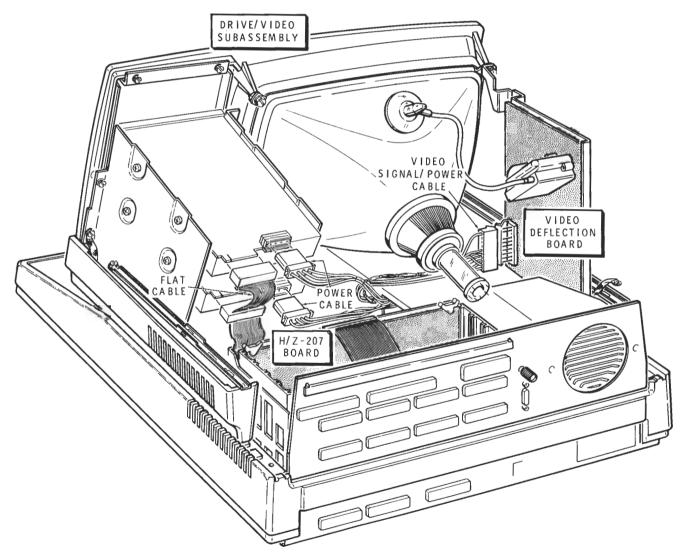

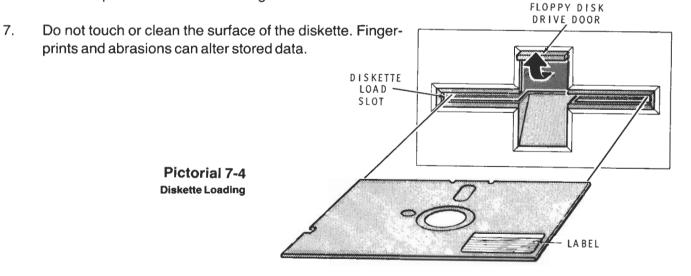

Refer to Pictorial 1-4.

Remove screw A and completely loosen the four B screws (these last four may be accessed through holes in the cabinet slides. Lift the display and disk drive assembly up and forward a short distance.

Pictorial 1-4. Display and Disk Drive Assembly Removal

#### **Disassembly**

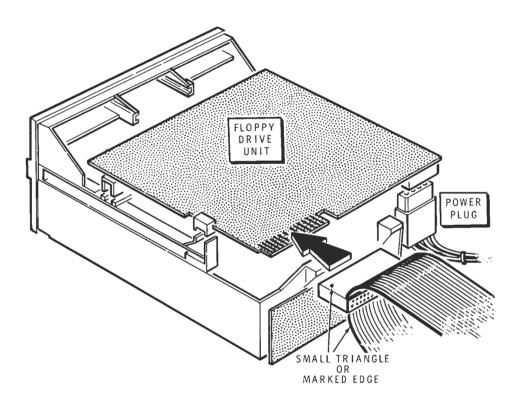

- Floppy Disk Systems only; refer to Pictorial 1-5 and remove:

- the flat cable from the floppy disk controller card,

- the power supply cable(s) at the drive(s), and

- the video signal/power cable on the video deflection board.

Pictorial 1-5. Disconnecting the Floppy Disk Drives

### Disassembly

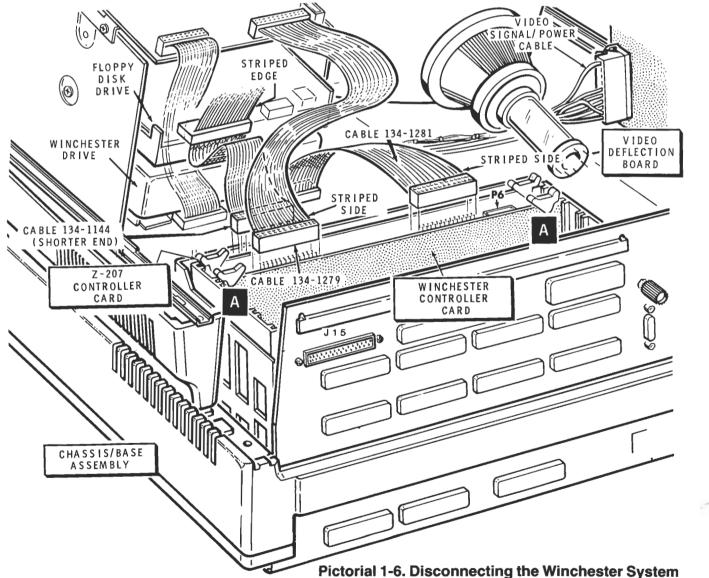

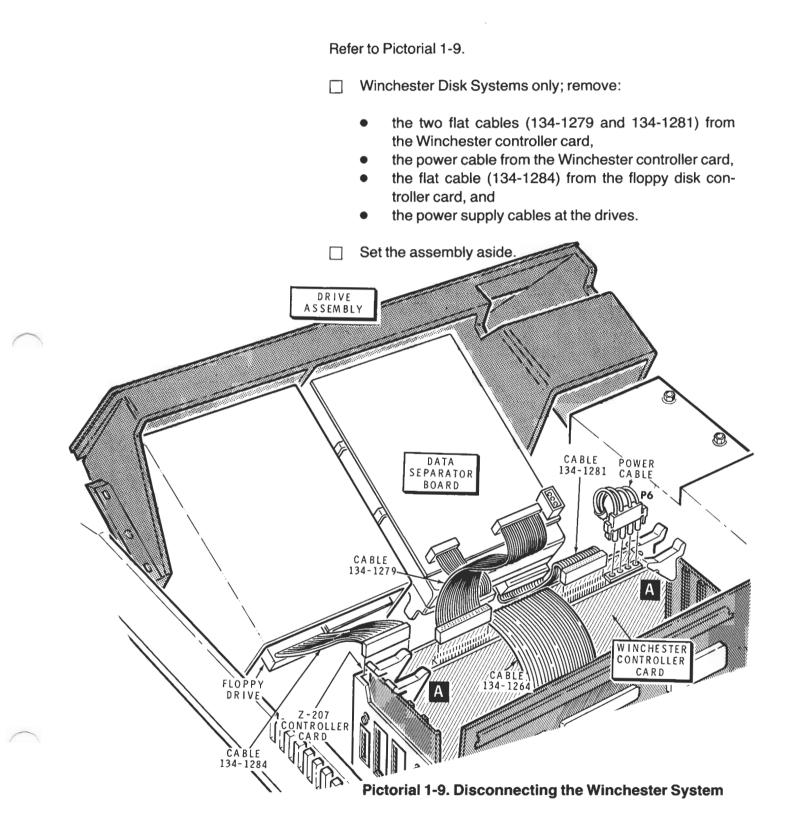

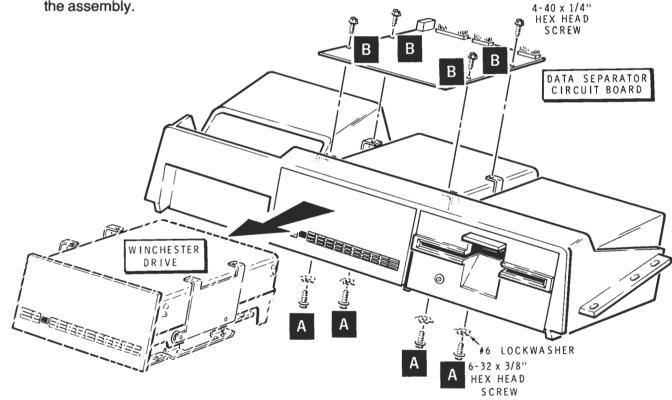

- Winchester Disk Systems only; refer to Pictorial 1-6 and remove:

- the two flat cables (134-1279 and 134-1281) from the Winchester controller card,

- the flat cable (134-1144) from the floppy disk controller card,

- the power cable from the Winchester controller card,

- the power supply cables from the drives, and

- the video signal/power cable on the video deflection board.

#### Disassembly

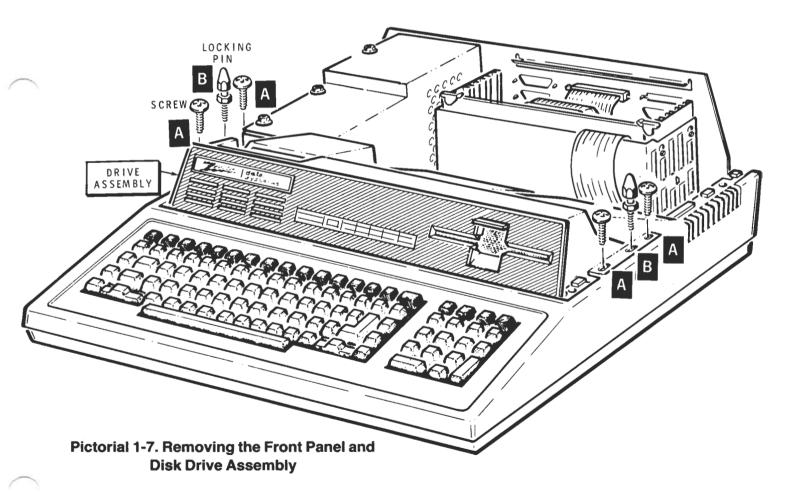

# Low-Profile Front Panel and Disk Drive Assembly

Refer to Pictorial 1-7.

- Remove the four screws at A and two locking pins at B.

- Lift the front panel and disk drive assembly out of the computer and to the front a short distance.

#### Disassembly

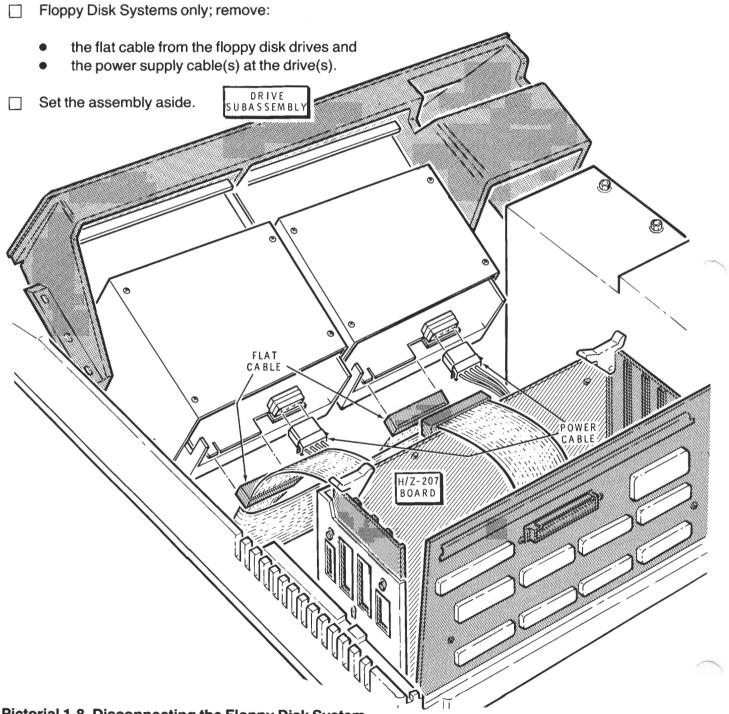

Refer to Pictorial 1-8.

Pictorial 1-8. Disconnecting the Floppy Disk System

#### Disassembly

### Disassembly

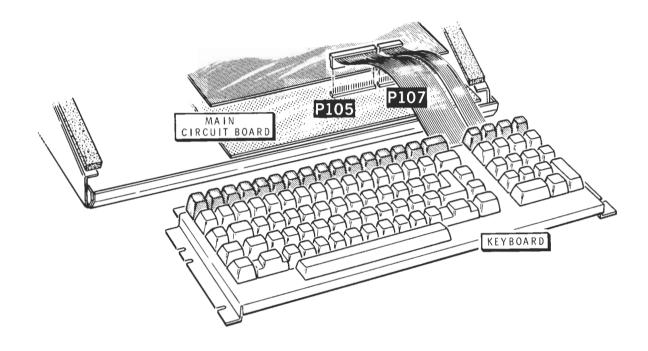

#### Keyboard

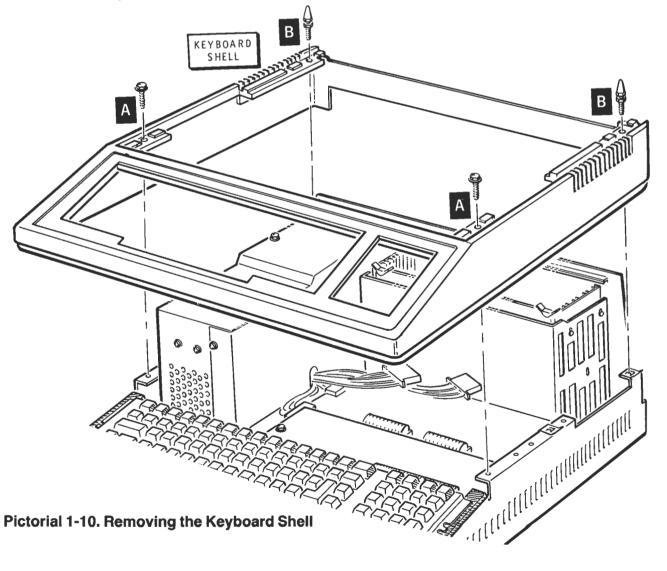

Refer to Pictorial 1-10.

- Remove the two screws at A from near the top of the keyboard.

- Low-Profile models only; remove the two locking pins at B from near the rear of the computer.

- Lift off the keyboard shell. Set the shell to one side.

# GENERAL INFORMATION Disassembly

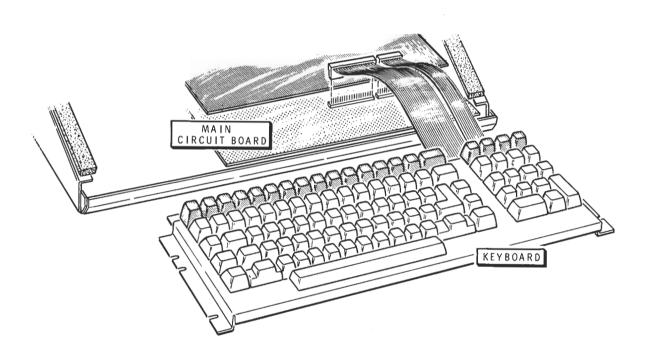

Refer to Pictorial 1-11.

Move the keyboard forward and unplug the two cables from the main board. Set the keyboard to one side.

Pictorial 1-11. Removing the Keyboard

#### Disassembly

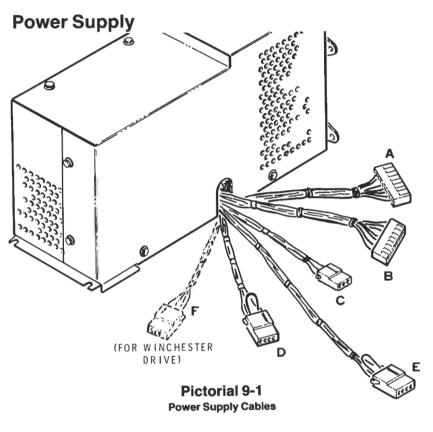

#### **Power Supply**

Refer to Pictorial 1-12.

**NOTE:** Your power supply may look different than the one illustrated.

- Unplug remaining power cables.

- Remove the four screws at A from the rear panel as illustrated.

- Remove the two screws at B from the front bottom of the power supply that hold it to the base.

- Lift the power supply out of the computer and set it to one side.

**WARNING:** There are no user-serviceable parts inside your power supply. Never open it up or break the seal; with a line cord attached, there are lethal voltages present!

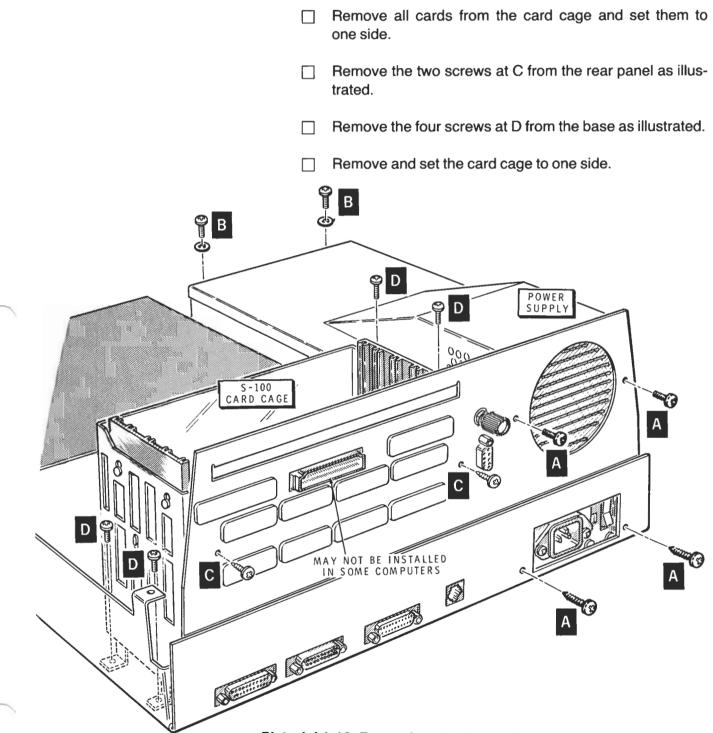

#### **Card Cage**

Disconnect any remaining cables to cards in the card cage. Note their positions; because of the large variety of options available and new or planned products, no illustrations are provided in this manual for reconnecting these cables.

#### Disassembly

#### Disassembly

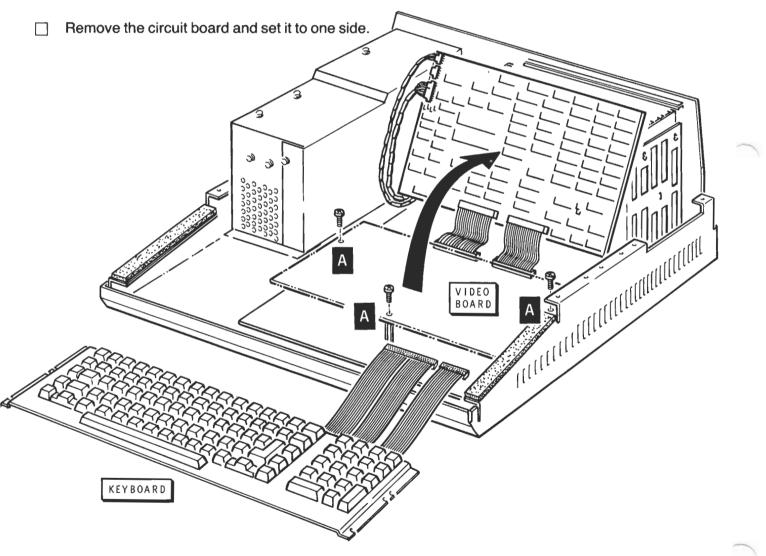

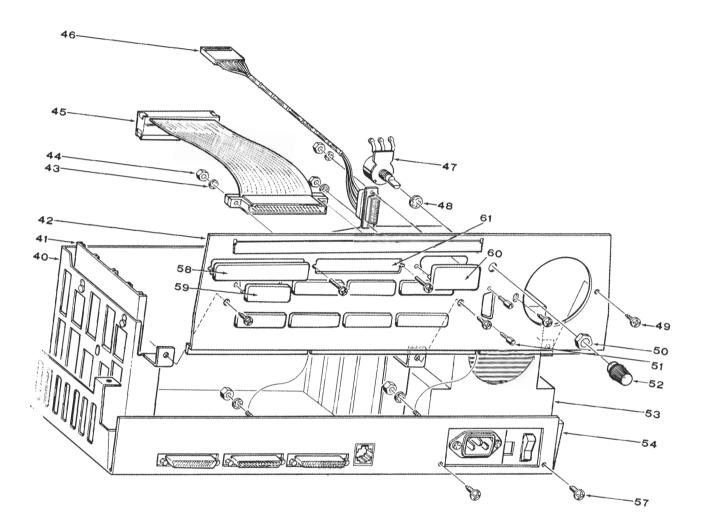

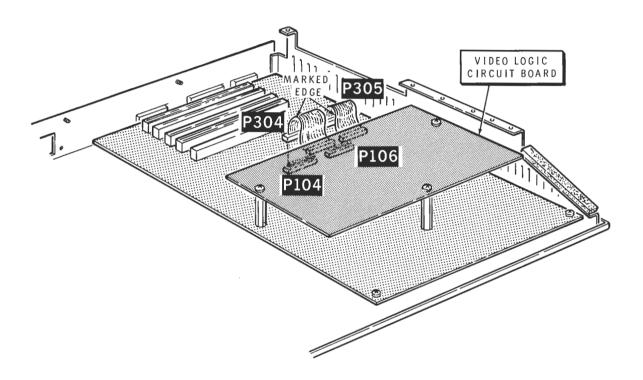

#### Video Logic Circuit Board

Refer to Pictorial 1-13.

- Remove the three screws holding the board to the three hex mounting spacers.

- Unplug the two cables from the main board.

Pictorial 1-13. Removing the Video Logic Board

# GENERAL INFORMATION Disassembly

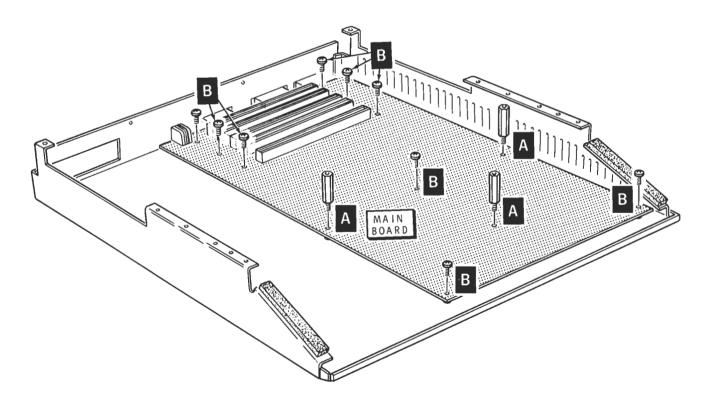

#### **Main Board**

Refer to Pictorial 1-14.

- Remove the three hex mounting spacers at A from the main board.

- Remove the nine screws at B from the main board.

- Remove the main board and set it to one side.

This completes the disassembly of the modules of your computer. The next section covers disassembly of the disk drive modules.

Pictorial 1-14. Removing the Main Board

#### Disassembly

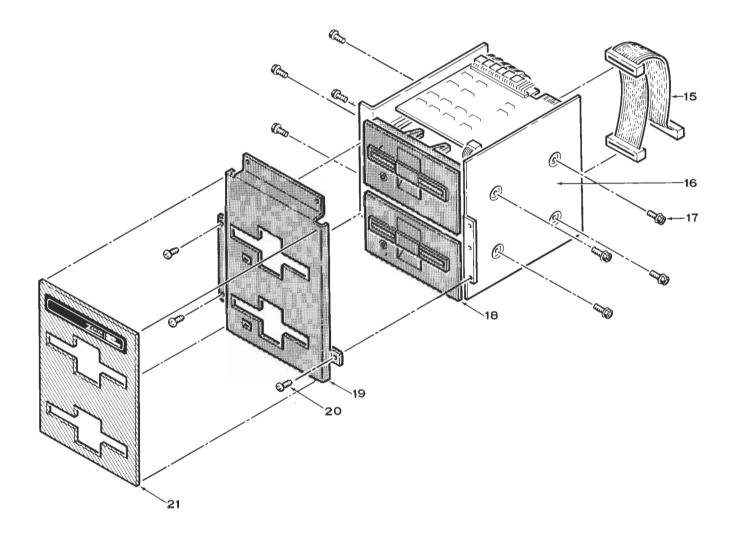

#### **Disk Drive Modules**

There are several different configurations of disk drives for your computer. These include units with one or two floppy disk drives, one floppy disk drive and one Winchester drive, and similar modules with half-height floppy disk drives.

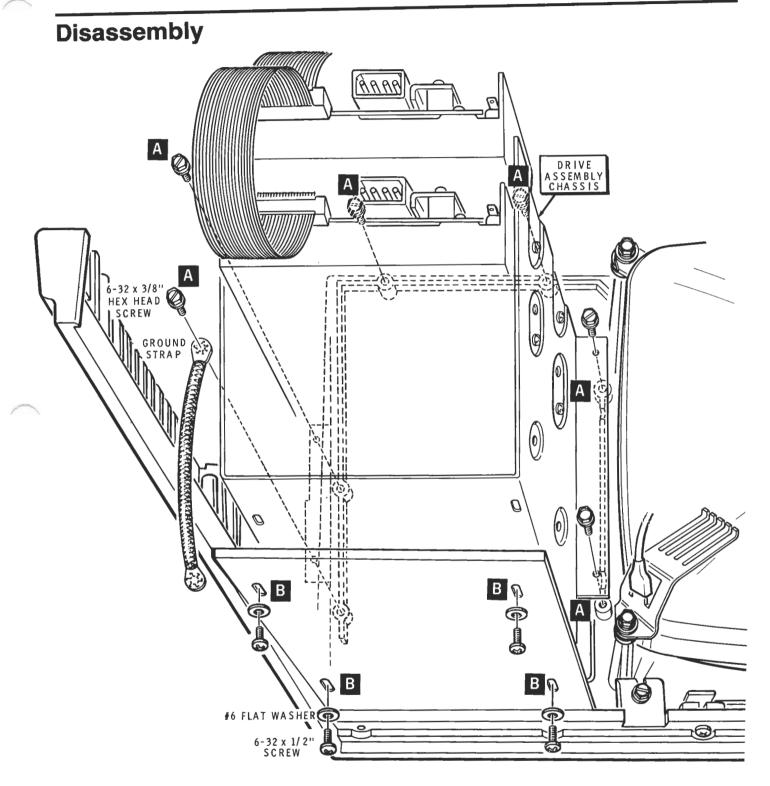

#### All-in-One Models

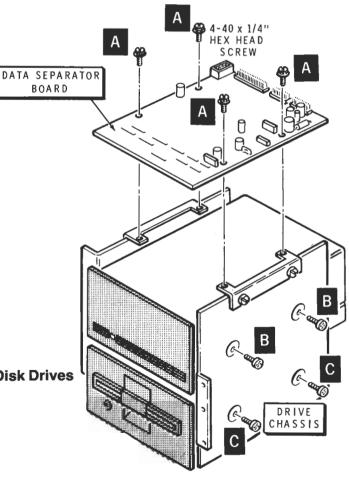

Refer to Pictorial 1-15. Note that this pictorial illustrates a twodrive half-height module; the following instructions apply equally to all configurations of the All-in-One computer — fullsized floppy disk, half-height floppy disk, and Winchester versions.

- Remove the four screws and spacers at B.

- Remove the six screws at A. Note the ground strap placement.

- Remove the drive assembly chassis from the display and disk drive assembly.

- Set the display assembly to one side.

Pictorial 1-15. Removing the Disk Drive Assembly

#### Disassembly

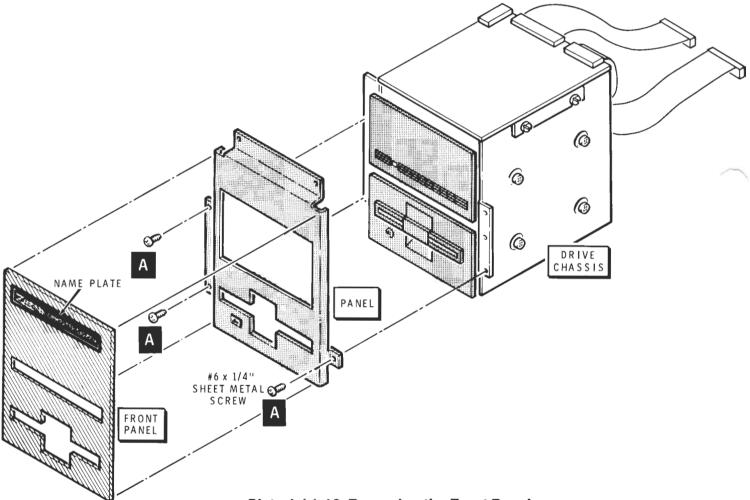

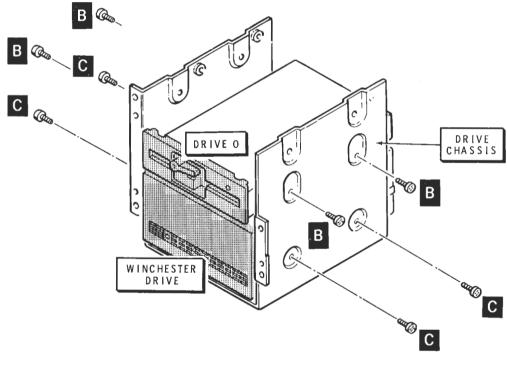

Refer to Pictorial 1-16. This pictorial illustrates a Winchester and full-sized floppy disk system. Your system, whether it is a half-height or floppy disk only version will be similar.

Remove the three screws at A and remove the front panel and panel from the assembly.

#### Disassembly

#### **Winchester Systems**

Refer to Pictorial 1-17.

- Remove the data separator cable assembly 134-1380 from the data separator board.

- Remove the four screws at A and remove the data separator board; set it to one side.

- Full-sized floppy disk drives only; remove the four screws at B and remove the Winchester disk drive.

- Full-sized floppy disk drives only; remove the four screws at C and remove the floppy disk drive.

Pictorial 1-17. Removing the Disk Drives

#### Disassembly

Refer to Pictorial 1-18.

- ☐ Half-height floppy disk drives only; remove the four screws at B and remove the floppy disk drive.

- ☐ Half-height floppy disk drives only; remove the four screws at C and remove the Winchester disk drive.

#### **Disassembly**

#### **Low-Profile Models**

- Get the front panel and disk drive assembly that you set to one side earlier.

- ☐ Carefully remove the front panel from the front of the assembly. Set it to one side where the tacky side will not be contaminated by dust, lint, paper, or other objects.

Refer to Pictorial 1-19.

- Winchester versions only; remove the four screws at B and remove the data separator board.

- Winchester versions only; remove the four screws at A and carefully slide the Winchester drive out the front of the assembly.

Pictorial 1-19. Removing the Winchester Drive

#### **Disassembly**

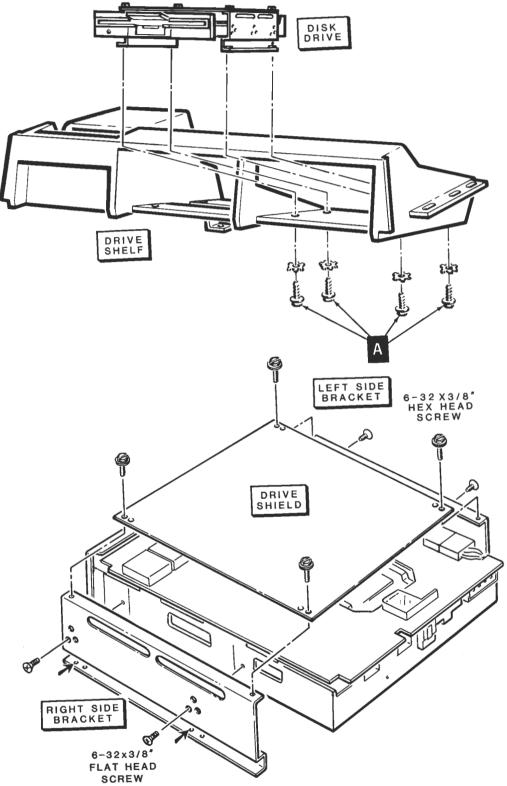

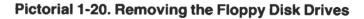

Refer to Pictorial 1-20. This pictorial illustrates removal of a half-height drive from the drive shelf. Removal of a full-sized drive is similar.

- Remove the four screws at A and slide the floppy disk drive out the front of the assembly.

- Half-height versions only; remove the four screws holding the drive shield to the left and right side brackets.

- ☐ Half-height versions only; remove the two flat head screws that hold each side bracket to the drive. Note the placement of the mounting screws in the side bracket; the position and holes used will vary according to the drive used in your system.

- ☐ If your system has two floppy disk drives, the second drive may be removed in a similar manner to the first.

This completes the disassembly section of your manual. Parts are identified in the various parts lists through this and other technical manuals published by Zenith Data Systems. A complete service manual is also available from Heath replacement parts or your local dealer.

## **GENERAL INFORMATION**

## Disassembly

~

# **Main Board**

| Description 2.2                                |

|------------------------------------------------|

| User Options and Jumpers 2.3                   |

| Programming Information 2.6                    |

| Theory of Operation 2.19                       |

| Circuit Description 2.23                       |

| Replacement Parts List 2.92                    |

| Semiconductor Identification 2.95              |

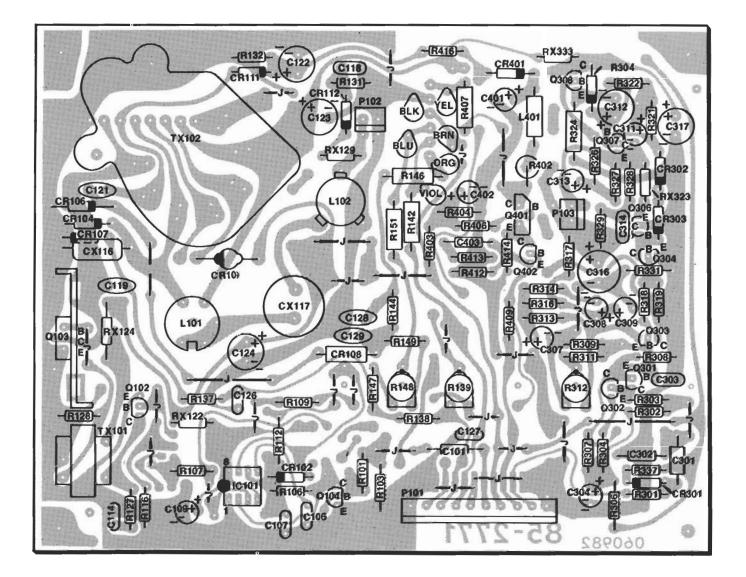

| Circuit Board X-Ray Views 2.136                |

| Interconnect Pin Definitions 2.137             |

| Schematic (Inside Envelope at rear of manual.) |

\_\_\_\_\_

## DESCRIPTION

The main board is the permanent bus master unit in the S-100 bus system and contains two microprocessors, an 8085 and an 8088. Both operate at 5 MHz. The 8088 has a 16-bit internal architecture that interfaces to an 8-bit external architecture, while the 8085 is a pure 8-bit processor.

The main board also contains up to 32k bytes of ROM, and up to 192k bytes of RAM with parity. There are two serial ports, a parallel printer port, a light pen port, a keyboard, and a timer. All of these ports are accessible from the S-100 bus.

The five-slot S-100 bus is located on the main board. This bus meets the proposed IEEE-696 definition of an S-100 bus.

The main board itself is not an S-100 card, although it meets the signal interface requirements of an S-100 card.

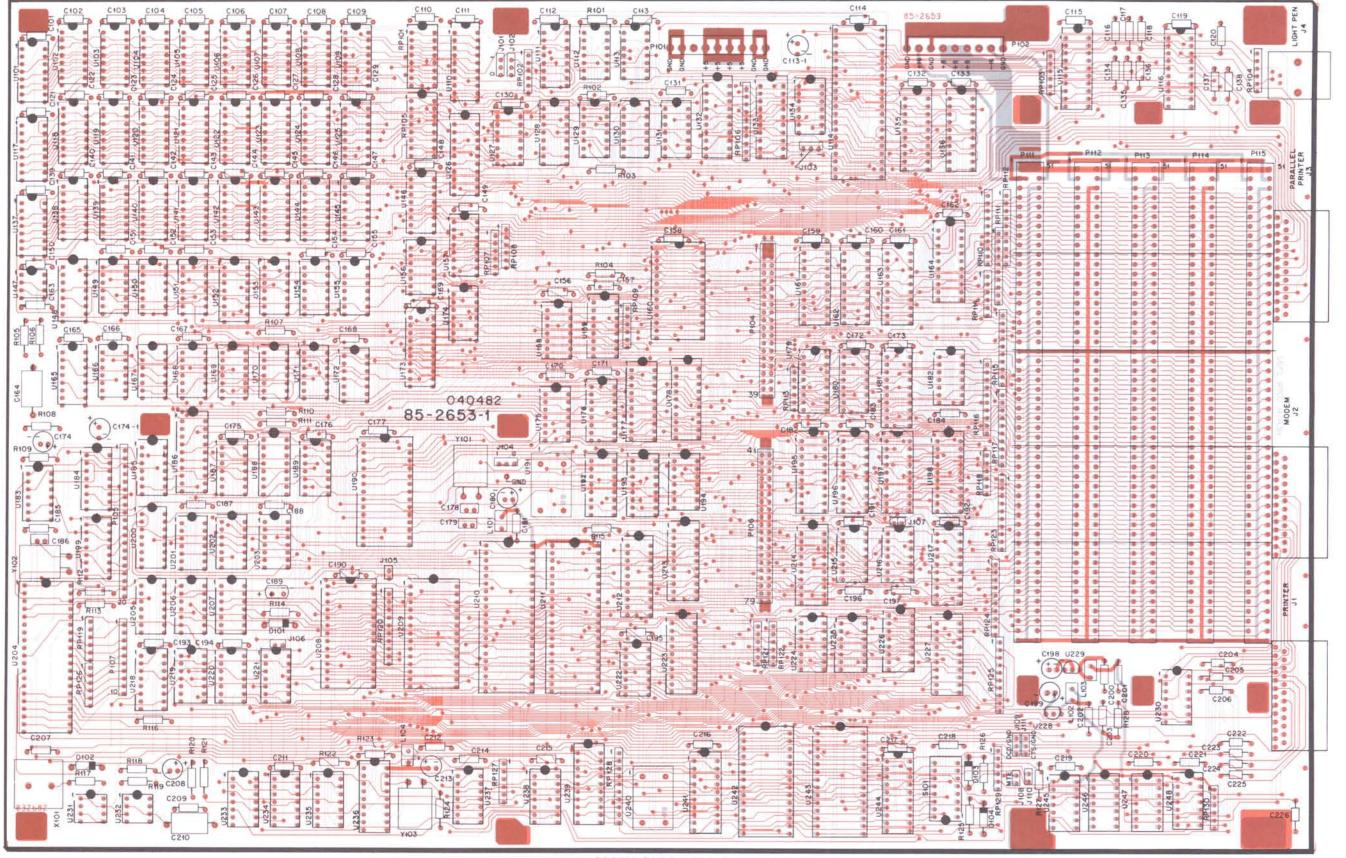

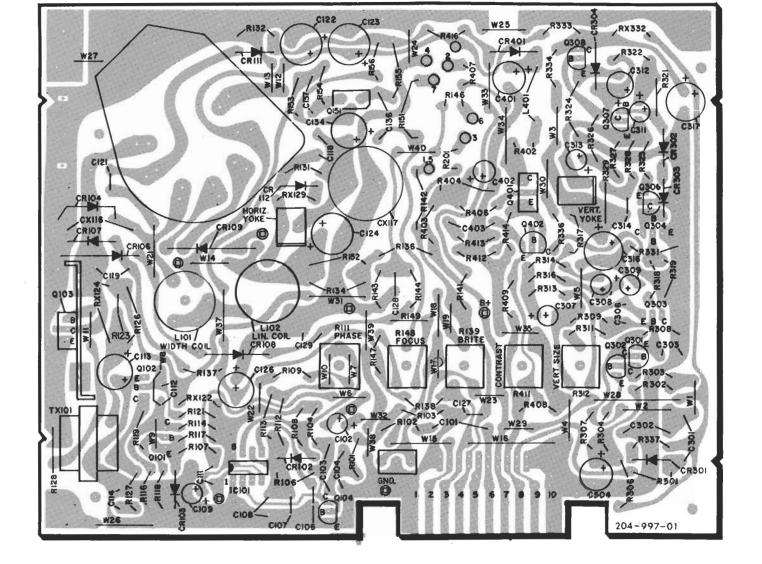

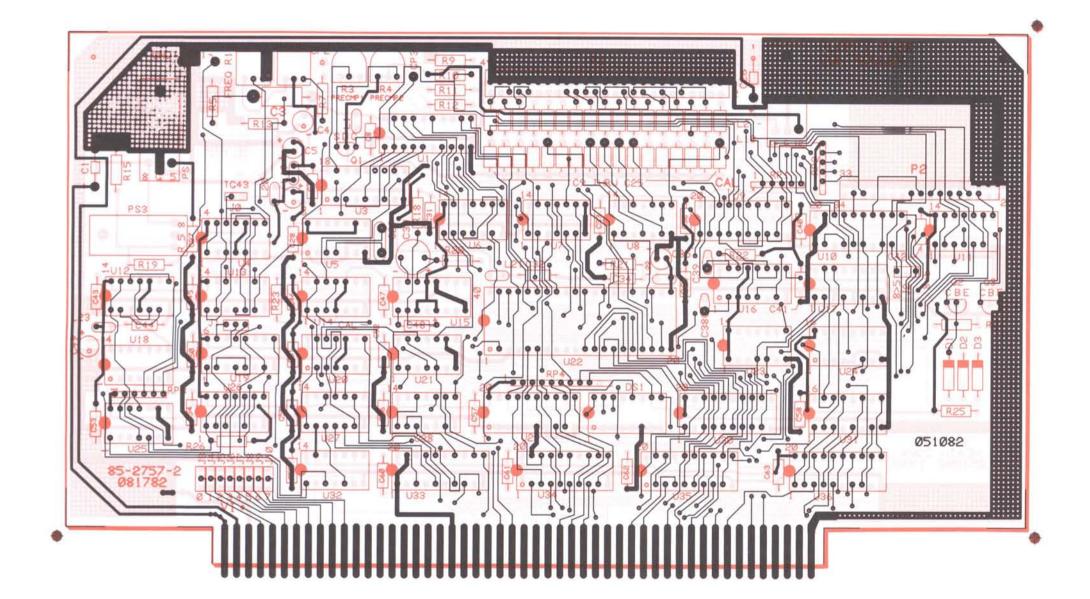

Pictorial 2-1 Main Circuit Board

~

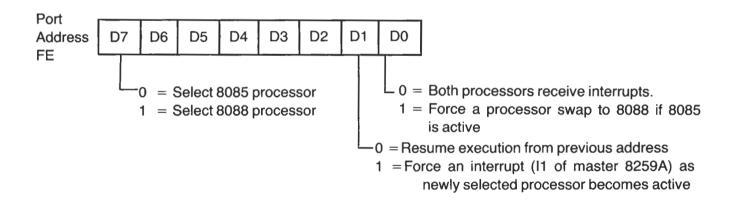

Refer to Pictorial 2-1 as you read the following information.

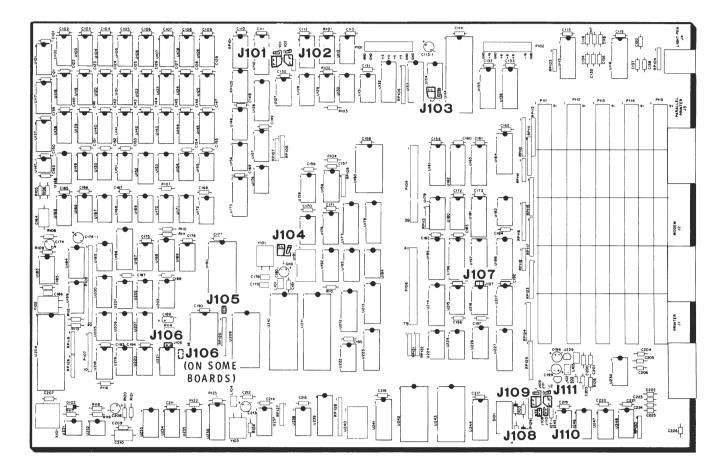

#### Switch S101

DIP switch S101 selects the following functions during powerup or master reset. Set the switches for your system and preferences.

| Switch S101,<br>Section              | Description                                                                                                                           |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | <pre> } Default boot device* 1 = Auto boot, 0 = Manual boot } not used 0 = 60 Hz, 1 = 50 Hz; for video vertical scan frequency.</pre> |

Sections 0, 1, and 2 should be set to reflect the type of drive that the system is to be booted from:

| Swite<br>Secti |   |   | Device                                 |

|----------------|---|---|----------------------------------------|

| _2             | 1 | 0 | Туре                                   |

| 0              | 0 | 0 | 5-1/4″ floppy disk drive<br>(internal) |

| 0              | 0 | 1 | 8" floppy disk drive (external)        |

| 0              | 1 | 0 | 5" Winchester disk (internal)          |

# USER OPTIONS AND JUMPERS

#### **Circuit Board Jumpers**

The main board circuit board jumpers perform the following functions:

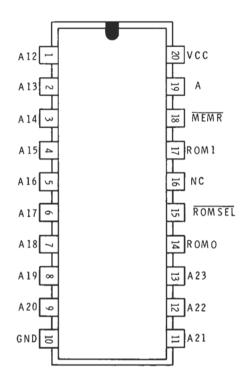

**J101** — Selects whether +5VDC or address line BA14 is applied to pin 27 of the PROM. The position shown has +5VDC connected to pin 27 for an 8K  $\times$  8 or 16K  $\times$  8 PROM. Move the jumper to the other position to use a 32K  $\times$  8 EPROM.

**J102** — Same as J101 except for address line BA13 and pin 26 of the PROM. The position shown is for using an 8K  $\times$  8 EPROM. Move the jumper to the other position to use a 16K  $\times$  8 or a 32K = 8 EPROM.

**J103** — Controls which transition of the light pen strobe (LTPNSTB) will cause a light pen interrupt. The position shown causes an interrupt on the negative-going edge. It is properly jumpered for operation with a light pen that causes a negative pulse during a "hit."

**J104** — No jumper is needed at this position. A foil trace connects the indicated two pins as shown. If the foil is cut and a jumper is installed in the other position, an NMI (TRAP for the 8085) will be generated when the S-100 power fail signal (PWRFAIL\*) is active.

**J105** — No jumper is needed at this position. If a jumper is installed, the TEST input to the 8088 will be grounded. Otherwise, this input is high.

J106 — For factory test use only.

**J107** — No jumper is needed at this position. A foil trace connects the two pins together. If the foil is cut, the main board will not provide the S-100 MWRT signal. Currently, the main board does provide this signal to the S-100 bus.

## USER OPTIONS AND JUMPERS

**J108** — No jumper is presently used at this position. If a jumper plug is installed, serial port B will generate an interrupt when the transmitter is empty (TXEMT active) in addition to its normal interrupts.

**J109** — This jumper connects serial port A DCD input to either ground or RTS from the connector. It is normally set in the mode shown that connects DCD to RTS.

J110 — Same as J108, but for serial port A.

**J111** — This jumper connects the serial port A CTS line to either ground or RTS from the serial connector. It is normally set in the position shown, which connects the CTS line to ground.

The information in this section concerns the main board only and is meant to be used by the experienced programmer. Programming for the entire system is contained in "Programming Data" toward the end of this manual.

#### **Port Addresses**

The following port addresses are for devices located on the main board. A more complete list can be found in "Programming Data."

| Device Name                        | Port Address (HEX) |

|------------------------------------|--------------------|

| DIP Switch                         | FF                 |

| Processor Swap                     | FE                 |

| High Address Latch                 | FD                 |

| Memory Control Latch               | FC                 |

| 8253 Timer Status                  | FB                 |

| reserved                           | FA                 |

| reserved                           | F9                 |

| reserved                           | F8                 |

| reserved                           | F7                 |

| resérved } for manufacturing tests | F6                 |

| 8041A Keyboard                     | F5                 |

| – 8041A Keyboard                   | F4                 |

| 8259A Master                       | F3                 |

| – 8259A Master                     | F2                 |

| 8259A Slave                        | F1                 |

| – 8259A Slave                      | F0                 |

| 2661 Serial B                      | EF                 |

| – 2661 Serial B                    | EE                 |

| – 2661 Serial B                    | ED                 |

| – 2661 Serial B                    | EC                 |

| Device Name     | Port Address (HEX) |

|-----------------|--------------------|

| 2661 Serial A   | EB                 |

| – 2661 Serial A | EA                 |

| – 2661 Serial A | E9                 |

| – 2661 Serial A | E8                 |

| 8253 Timer      | E7                 |

| 8253 Timer      | E6                 |

| 8253 Timer      | E5                 |

| 8253 Timer      | E4                 |

| 68A21 Parallel  | E3                 |

| 68A21 Parallel  | E2                 |

| 68A21 Parallel  | E1                 |

| 68A21 Parallel  | E0                 |

#### **Port Bit Definitions**

The definitions given below are for the bits that are written to or read from the ports listed earlier that do not connect to peripheral devices.

#### Dip Switch Port (FF)

The function of the DIP switch bits are defined by the monitor program in ROM on power-up or master reset, but they may be redefined and reread by the operating system when it is loaded. The following chart gives the definition of the DIP switch's bits for the monitor ROM.

| *Sections 0, 1, and 2 should be set to reflect the type of drive |

|------------------------------------------------------------------|

| that the system is to be booted from:                            |

| Swite<br>Sect |   |   | Device                                         |                                |

|---------------|---|---|------------------------------------------------|--------------------------------|

| 2             | 1 | 0 | Type:                                          | 4000 MIE 000/0400 MIE 000/0400 |

| 0             | 0 | 0 | 5-1/4″ Floppy Disk Drive (internal)            |                                |

| 0             | 0 | 1 | 8" Floppy Disk Drive                           |                                |

| 0             | 1 | 0 | (external)<br>5″ Winchester Disk<br>(internal) |                                |

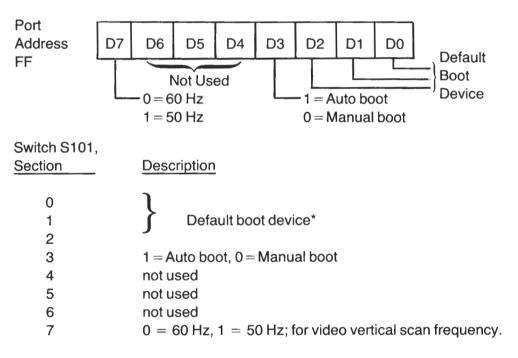

#### **Processor Swap Port (FE)**

Processor swap is accomplished by the presently selected processor writing to bit 7 of the processor swap port (PSP). If a 1 is written, the 8088 is selected. A 0 selects the 8085. (See the following chart.)

When the processor swap occurs, the newly selected processor can be restarted where it left off, or, an interrupt (I1 on 8259A) can be generated. Interrupt generation is enabled by writing a 1 to bit 1 (not LSB) of the PSP.

The last option that concerns the swap port is the masking of interrupts. If interrupts are not masked, the currently selected processor is signaled when an interrupt is requested. If the MASK mode is selected, no interrupts will get through to the 8085. The 8088 will service all interrupts. In the MASK mode, a processor swap to the 8088 is generated whenever an interrupt occurs with the 8085 active. MASK is bit 0 of the PSP. A 1 activates this function.

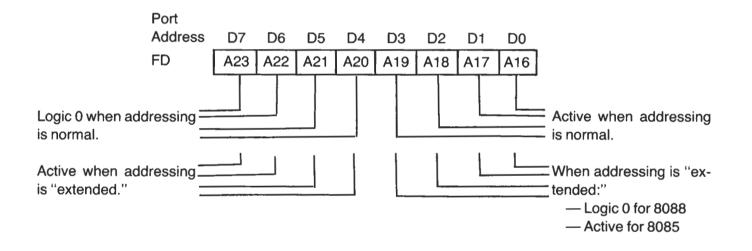

#### High Address Latch (FD)

The 8085 in its natural state has 16 bits of addressing capability. By writing to the high address latch, HIGHADDR, the user can control the upper eight address bits placed onto the bus, and thereby generate 24-bit addresses.

The 8088 naturally has 20 bits of addressing. The upper four bits placed on the bus are controlled by HIGHADDR. The hardware automatically selects bits A16-A19 coming from the 8088 when the 8088 is selected.

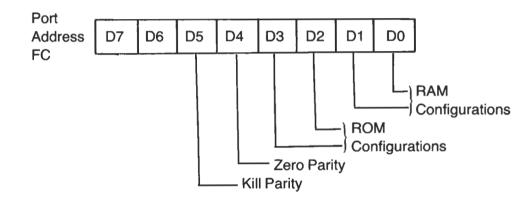

#### Memory Control Latch Port (FC)

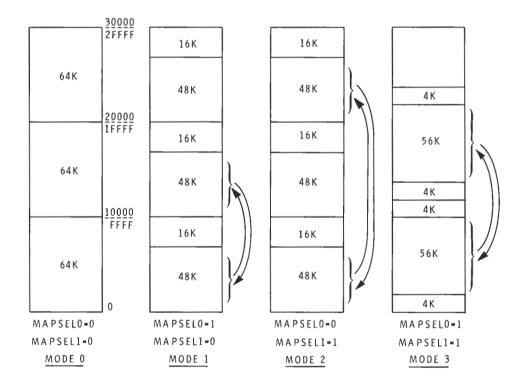

This port controls the configuration of memory, both ROM and RAM. It also provides an option for checking RAM parity. The options, which affect how the ROM is addressed, are enabled by writing to the memory control latch (MEMCTL) port.

The following chart shows which port bits control the various **RAM** configurations.

| BITS | DEFINITION |

|------|------------|

|      |            |

| 1,0 | 00 = Option 0 | 01 = Option 1 |  |  |  |

|-----|---------------|---------------|--|--|--|

|     | 10 = Option 2 | 11 = Option 3 |  |  |  |

Option 0, the power-up master reset configuration, provides contiguous addressing; from 0 to 192 K.

Option 1, swaps the RAM block from 0 to 48 K with the block at 64 to 112 K.

Option 2, swaps the RAM block from 0 to 48 K with the block at 128 to 172K.

Option 3, swaps the RAM block from 4 to 60 K with the block at 68 to 124 K.

The following chart shows which port bits control the four **ROM** configurations.

| BITS | DEFINITION    |               |

|------|---------------|---------------|

| 3,2  | 00 = Option 0 | 01 = Option 1 |

|      | 10 = Option 2 | 11 = Option 3 |

Option 0, the power-up or master reset configuration, makes the code in ROM appear to be in all of memory when reads are performed. Writes, however, occur normally.

Option 1 makes the ROM code appear to be at the top of every 64K page of memory.

Option 2 makes the ROM code appear to be at the top of the first megabyte of memory.

Option 3 disables the ROM.

Parity consists of a parity bit for each byte in RAM. This adds one, two, or three 64K-bit chips (depending on how much RAM is installed: 64K, 128K, or 192K) and the associated support circuitry.

RAM parity has two control options: ZERO\_PARITY and KILL\_PARITY. The ZERO\_PARITY option sets the parity to the zero state. This sets the parity bit to 0 regardless of the data pattern that was written and can be used to force a parity error to check the parity logic. The option is activated by writing a 0 to bit 4 of the Memory Control Latch (MEMCTL) port.

The KILL\_PARITY option disables the parity checking circuitry by writing a 0 to bit 5 of the MEMCTL port. It also clears a parity error by first writing a 0 to bit 5 and then a 1.

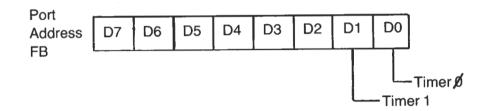

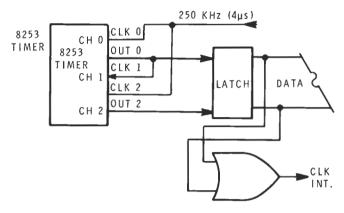

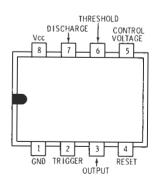

#### 8253 Timer Status Port (FB)

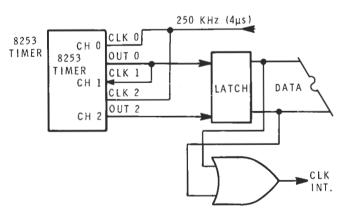

The timer circuitry consists of an 8253 timer IC and several other IC's. (See the Timer Port Address Block Diagram.) The 8253 has three channels. Each channel has a input clock (-CLK) and an output (OUT). The CLO0 and CLK2 inputs are tied to a 250 kHz (4  $\mu$ S) clock. The CLK1 input is tied to the output of channel 0, and thus channels 0 and 1 are cascaded.

Outputs OUT0 and OUT2 produce the timer interrupt input to the 8259. A latch is provided which can be read to determine which of the channels caused the interrupt (TMRSTAT). Outputs of these latches are OR'ed together to produce the interrupt input to the 8259.

To find out which timer caused an interrupt, the timer status port must be read. A high level on either the Timer 0 or Timer 1 bit indicates that the corresponding timer has had a positive transition on its OUT signal. In order to detect the next transition on the OUT signal, the latch should be cleared by writing a zero to the appropriate bit position in the timer status port.

The 8253 data sheet is supplied in the Appendices portion of this documentation. The following chart is provided for the convenience of those who may already be familiar with the 8253 device.

| <u>BIT</u>  | DEFINITION                                                                     |                                                                            |  |  |  |  |

|-------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|--|--|--|

| 0           | 0 = Use 16-bit binary counter<br>1 = Use 4-decade binary coded decimal counter |                                                                            |  |  |  |  |

| 1<br>2<br>3 | 000 = Mode 0<br>X10 = Mode 2*<br>100 = Mode 4                                  | 001 = Mode 1<br>X11 = Mode 3<br>101 = Mode 5                               |  |  |  |  |

| 4           | 00 = Counter latch                                                             | 01 = Read/load least<br>significant byte<br>only                           |  |  |  |  |

| 5)          | 10 = Read/load most<br>significant byte<br>only                                | 11 = Read/load least<br>significant byte,<br>then most<br>significant byte |  |  |  |  |

| 6<br>7      | 00 = Counter 0<br>10 = Counter 2                                               | 01 = Counter 1<br>11 = Undefined                                           |  |  |  |  |

\*X = Don't care.

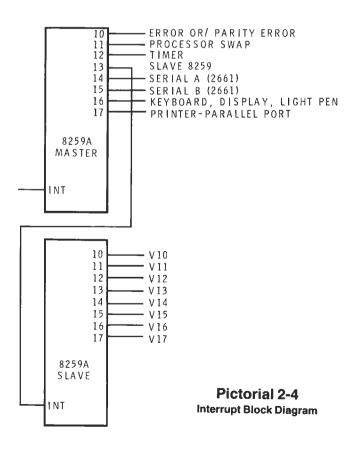

#### 8259A Interrupts (F0-F3)

The following list shows the possible interrupts. The slave 8259A handles only the vector interrupts you configure your hardware to generate.

Timer Port Address Block Diagram

#### Master 8259A

- I0 S-100 error signal (parity error from main board memory).

- I1 Processor swap

- I2 Timer

- l3 Slave 8259A

- 14 Serial A

- I5 Serial B

- 16 Keyboard video display, and light pen

- 17 Parallel printer port

#### Slave 8259A

#### 68A21 Parallel Port (E0-E3)

| Port<br>Address | 7     | 6     | 5           | 4      | 3    | 2      | 1           | 0      |                                  |

|-----------------|-------|-------|-------------|--------|------|--------|-------------|--------|----------------------------------|

| E0(CRA2=1)      | CLPHT | LPSWT | CVINT       | VIDINT | INIT | STROBE | PD2         | PD1    | Peripheral<br>Register A<br>Data |

| E0(CRA2=0)      | 1     | 0     | 1           | 0      | 1    | 1      | 1           | 1      | Direction<br>Register A          |

| E1              | IRQA1 | IRQA2 | CA2 Control |        |      | CRA2   | CA1 Control |        | Control<br>Register A            |

| E2(CRB2 = 1)    | PD8   | PD7   | PD6         | PD5    | PD4  | PD3    | ERROR       | BUSY   | Peripheral<br>Register A         |

| E2(CRB2 = 2)    | 1     | 1     | 1           | 1      | 1    | 1      | 0           | 0      | Data<br>Direction<br>Register B  |

| E3              | IRQB1 | IRQB2 | CB2 Control |        |      | CRB2   | CB1 C       | ontrol | Control<br>Register B            |

CA1 = LTPNSTB (light Pen Strobe)

CA2 = QVIDINT (Latched Vertical Sync)

CB1 = ACK (Printer Acknowledge Signal)

CB2 = BUSY (Printer Busy Signal)

The 68A21 and associated circuitry perform three functions:

- Parallel printer port

- Light pen port

- Couples video retrace signal to CPU

The 68A21 is configured as a parallel printer port. The CPU programs the 68A21 and controls it during data transfer.

This printer port uses portions of both port A and port B in the 68A21. The eight bits of data out to the printer, PD1–PD8, are assigned to port A, bits 0 to 1, and to port B, bits 2 through 7 assigned to port A, bits 0 to 1, and to port B, bits 2 through 7 respectively. Data is latched at the printer by pulsing the STROBE signal (Port A, bit 2). The printer may respond by activating the BUSY signal, which can be interrogated for a level condition by reading Port B, bit 0, or for a transition by appropriate use of the CB2 input and control bits. (See the 68A21 Data Sheet in the Appendices for detailed operation.) The printer may also respond by pulsing the ACK line, which may be detected through use of the CB1 input and the CB1 control bits. The printer error signal, ERROR, is read by Port B, bit 1. The printer may be initialized by activating the INIT line by Port A, bit 3.

The CPU will not respond to a signal from the light pen circuits. It requires a user-supplied program to set up interrupts, handle timing, and take care of bit locations that are pointed to by the light pen.

A pulse from the light pen is latched in a flip-flop, the output of which, LTPNSTB, is connected to the CA1 input. The flipflop must be cleared after detecting a light pen pulse by bringing  $\overline{\text{CLPHT}}$  (Port A, bit 7) low momentarily. The switch on the light pen may be read by inputting from Port A and examining bit 6,  $\overline{\text{LPSWT}}$ .

The vertical sync signal from the video board, VIDINT, Is also connected to the 68A21 of Port A, bit 4. The vertical sync is also latched in a flip-flop whose output, QUIDINT, is connected to teh CA2 input. By using the CA2 control bits, this input may be used to detect a transition of the vertical sync signal. This flip-flop is cleared by momentarily bringing CVINT (Port A, bit 5) low.

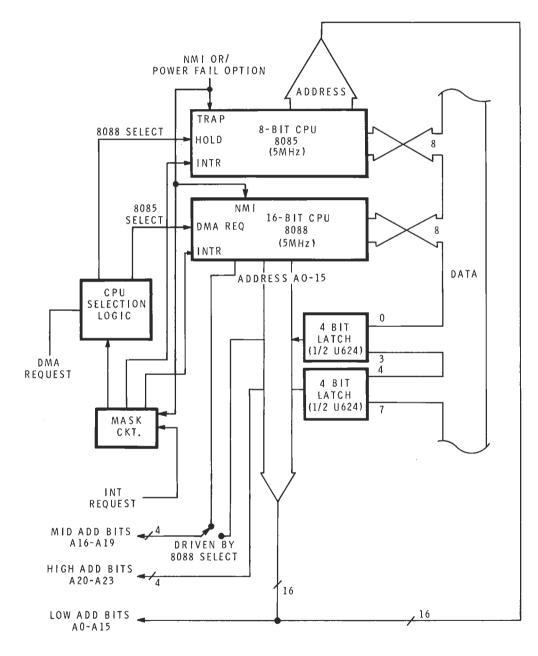

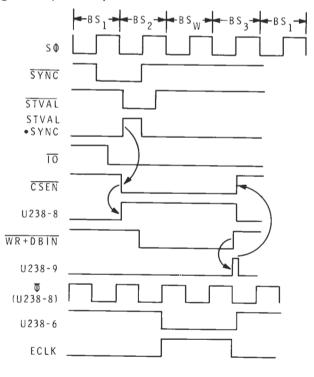

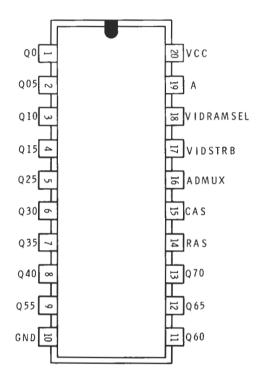

The Z-100 main board has five major parts: the CPU, the memory, the interrupt circuitry, the keyboard and timer, and the I/O circuitry. Each of these parts is shown in the block diagrams in Pictorials 2-1 through 2-5.

#### The CPU

As you can see in Pictorial 2-2, the CPU can be one of two different processors, either an 8085 or an 8088. The 8085 has 8-bit internal architecture and the 8088 has 16-bit internal architecture. They both communicate with the outside world via an 8-bit data bus.

The 8085 processor is built to generate 16-bit-wide memory addresses, but this range has been extended by 8 bits, generated through the address/data bus and latched by two 4-bit address latches. The total address width then becomes 24 bits. The 8088, on the other hand, is built to generate 20-bit addresses. This capability has been extended by 4 bits, which are similarly generated through the data bus and latched by one 4-bit address latch.

The two processors do not operate independently. Rather, they operate on an either/or basis, each being selected for use by software through the CPU selection logic. Upon power up, the 8085 is automatically selected, but the processors can be swapped at any time. When they are swapped, the newly selected processor can be restarted where it left off. Processor swapping may also occur whenever an interrupt occurs and the interrupt mask is enabled. The interrupt mask can prevent interrupts from reaching the 8085; instead, upon an interrupt, it can cause the CPU selection circuitry to select the 8088.

Pictorial 2-2 CPU Block Diagram

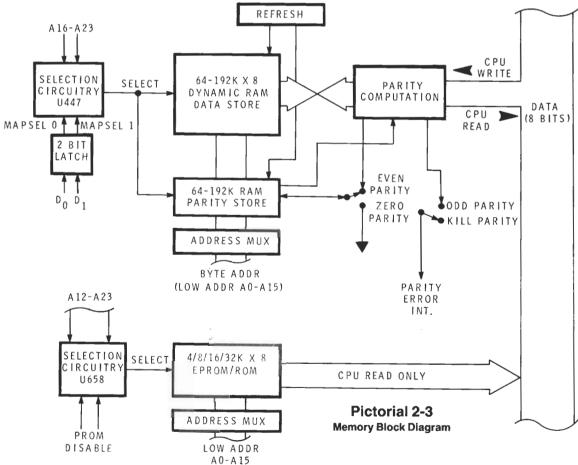

#### Memory

Pictorial 2-3 shows that the memory portion of the main board consists of memory selection circuitry, parity computation and storage, an address multiplexer, a refresh circuit, up to 192K of data and parity RAM, and up to 32K of ROM.

The selection circuitry decodes the address bits from the CPU to access the proper memory or port locations.

The parity computation and storage circuitry computes and stores a parity bit for every byte written into data RAM, and recomputes the parity and checks it against the value stored in parity RAM every time a word is read from data RAM. If a discrepancy is found, a parity error interrupt is sent to the 8259 interrupt controllers.

The address multiplexer converts the 16-bit address bus to the 8-bit row and column addresses required by the RAM chips.

The refresh circuit prevents the data in RAM from decaying.

The data and parity RAM is made up of 64K increments, while the ROM consists of a single EPROM or ROM chip.

#### **Interrupt Circuitry**

This circuitry consists of two 8259A interrupt processors, one a master and the other a slave. See Pictorial 2-4. The slave 8259A services vector interrupts from the S-100 bus if the hardware has been configured to use them.

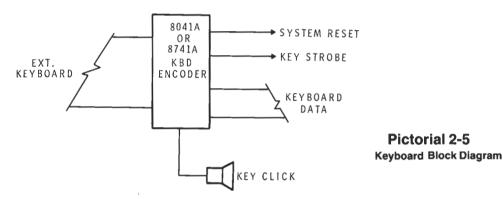

#### **Keyboard**

As shown in Pictorial 2-5, this circuitry is made up of a keyboard and a keyboard encoder.

The encoder detects a closed key contact in the keyboard and converts it into the corresponding ASCII code for that key.

#### I/O Circuitry

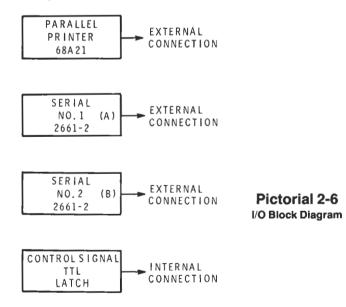

The I/O circuitry consists of a 6821 parallel printer port, two 2661-2 serial ports, and a TTL control latch for internal use of the main board, as shown in Pictorial 2-6.

Please refer to the main board schematic while you read the following detailed description.

#### The 8085 CPU

#### General

The 8085 CPU (U210 on the schematic) is the Computer's 8-bit processor. Because the 8085 uses the same instruction set as the Intel 8080, the Z-100 computer can maintain a high degree of software compatibility with previous Zenith Data Systems Computers.

To understand the 8085, study the pin-out and basic timing discussion that follows. If you need to know more about the 8085, see the IC data sheets Appendix C of this Manual.

NOTE: In this and all pln-out descriptions in this Manual, active low signals may be designated as such <u>by the traditional bar over the signal name</u> (e.g., SIGNAL).

#### **Pin-Out Description**

**A8-A15, pins 21-28 (3-state address).** These multiplexed lines contain the upper eight bits of the memory address during a memory access. During an I/O operation they contain the port address. The lines are tri-stated during HOLD, HALT, and RESET.

**AD0-AD7, pins 12-19 (3-state address/data).** These multiplexed lines first contain the lower eight bits of the memory address during a memory access. This address is then stored in external latches. The CPU next places the input or output data associated with that address on AD0-AD7. During an I/O operation, these lines first contain the port address, and then the data (either input or output) associated with that port.

### CPU

**ALE, pin 30 (address latch enable).** This output line pulses high, and then low, when either the memory or I/O address is on lines A0-A7. The external circuits use the negative-going transition to latch the address information. The falling edge of ALE is also used to strobe CPU status information.

S0, S1, IO/M, pins 29, 33, 34 (status output 0 & 1, input output/memory). These output lines are used in conjunction with ALE to develop the S-100 machine cycle status lines at U227. (See "Bus Status Circuits" on Page 2.35 for more details.)

**RD**, **pin 32 (3-state read control).** This input line goes to logic 0 to indicate that the data bus is ready to transfer data from memory or I/O to the CPU. 3-stated during HOLD, HALT, and RESET.

**WR**, pin 31 (3-state write control). This output line goes to logic 0 to indicate that the data bus is ready to transfer data from the CPU to memory or I/O. Data is set up on the trailing edge of the pulse. 3-stated during HOLD, HALT, and RESET.

**READY, pin 35 (ready).** If this input line is at logic 0, the CPU enters a wait state until READY is brought to logic 1 again. This allows using the 8085 with slow memories or peripherals.

**HOLD, pin 39 (hold).** If this input line is at logic 0, the CPU halts operation, raises the hold-acknowledge line (HLDA), and places the following lines into a high impedance state: Address/Data,  $\overline{WR}$ ,  $\overline{RD}$ , and  $IO/\overline{M}$ . This allows other processors, such as the 8088, to gain control of the bus.

**HLDA, pin 38 (hold acknowledge).** This input line goes high to indicate that the CPU received the HOLD request and will release control of the bus in the next cycle. HLDA goes low again after the HOLD request is removed.

CPU

**INTR, pin 10 (interrupt request).** If this input line is brought high, and the interrupts are not disabled through software, the CPU completes its current cycle and then processes the interrupt. (See "Interrupt Circuits" for more details.)

**INTA**, **pin 11 (interrupt acknowledge).** This output line goes low to indicate that the CPU has accepted the interrupt.

**TRAP, pin 6 (nonmaskable interrupt).** This input line is the highest priority interrupt and cannot be disabled.

**RESETIN**, pin 36 (reset input). Bringing this input line low resets the Computer. It sets the program counter to 0, disables interrupts, and resets the HLDA flip-flop.

**X1, X2, pins 1, 2 (clock input).** This clock input, provided by the 10-MHz crystal at Y101, is internally divided down to 5 MHz.

**CLK (clock output).** This clock output provides 5-MHz timing to the Computer when the 8085 has control.

RST 5.5, pin 9. Not used and tied to ground.

RST 6.5, pin 8. Not used and tied to ground.

RST 7.5, pin 7. Not used and tied to ground.

SID, pin 33. Not used and tied to ground.

SOD, pin 29. Not used and left unconnected.

CPU

8085A Timing

#### Timing

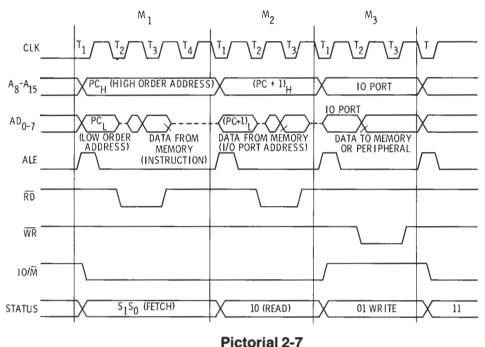

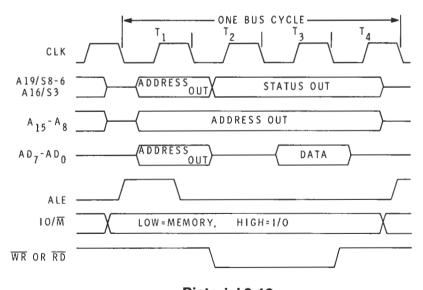

To better understand how the Computer works, you should become familiar with the 8085 timing. Pictorial 2-7 shows the waveforms that occur when the 8085 processes the OUT instruction. Though there are seven possible types of machine cycles (see the data sheets), these waveforms are typical.

During the M1 cycle, the Computer fetches the op code; in this example, the OUT instruction. The M1 cycle lasts for four clock states (T-states). During this time, A8 through A15 contain the upper eight bits of the memory address of the instruction to be fetched.

From time T1 to T2, lines AD0-AD7 contain the lower eight bits of memory address. The ALE line goes low to strobe this information into the external address latches. The  $IO/\overline{M}$  line goes low to indicate that this is a memory-read operation. The signals on the status lines, S0 and S1, indicate that the op code fetch cycle is taking place.

CPU

## CIRCUIT DESCRIPTION

From time T2 to T3,  $\overline{RD}$  goes low and the instruction in the memory location pointed to by the address latches is placed on lines AD0-AD7, which are now acting as data lines. The data, which consists of an OUT instruction, is loaded into the Computer for internal processing during time T3 to T4.

From time T3 to T4, RD goes high and AD0-AD7 goes to a high impedance state.

During the M2 cycle, the Computer reads the data in the next memory location, which is the I/O port address the Computer is to OUTput the data to. At time T1, lines A0-A15 contain the address of the memory location that holds the I/O port address. The ALE line strobes this address into the external address latches. Line IO/M is still low to indicate that the M2 cycle is a memory read cycle. This is also indicated by the logic states on status lines S1 and S0.

At time T2 to T3, RD goes low to read the memory location pointed to by the address latches. This location contains the address of the I/O port to be accessed.

During the M3 cycle, the Computer transfers the data in its accumulator to the port address specified by the M2 cycle. This time, during T1 to T2, lines AD0-AD7 contain the port address fetched during the M2 cycle. Line ALE strobes this information into the external address latches. Lines AD8-AD15 also contain the port address, but are not used. The IO/ $\overline{M}$  line goes high to indicate that this cycle is an I/O cycle, rather than a memory cycle. Also, the logic states of the status lines, S0 and S1, indicate that this cycle is an I/O write cycle.

During time T2 to T3, the data in the accumulator of the 8085 is placed on the data bus and  $\overline{WR}$  goes low to write it to the port pointed to by the address latches.

After T3, the 8085 generates another M1 cycle and fetches the next instruction in the program.

## CPU

#### The 8088 CPU

#### General

The 8088 CPU is the Comupter's 16-bit processor, which is located at U211 on the schematic. This IC combines the resources of a 16-bit microprocessor's internal architecture with the easy-to-use 8-bit bus interface. In fact, most of the functions of the bus lines in the 8088 are identical to the 8085 at U210.

Some of the features of the 8088 are:

- A 20-bit address bus, allowing the 8088 to directly address up to 1 megabyte of memory.

- A 16-bit input/output port address range, allowing the 8088 to select up to 65536 port addresses. However, only the lower eight bits are used in Z-100 Series Computers.

- Pipelined architecture to allow fetching instructions and processing previously-fetched instructions at the same time. (Refer to the "iAPX 88 Book" in Appendix C.)

CPU

#### **Pin-Out Description**

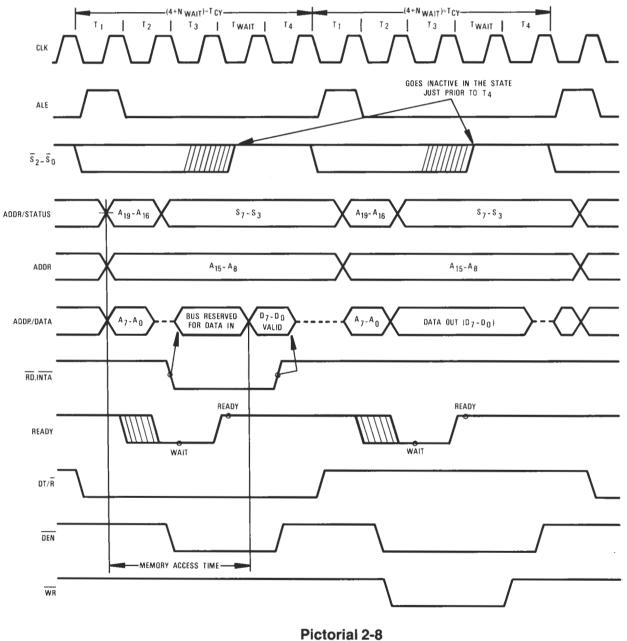

Refer to Pictorial 2-8 while you read the following paragraphs.

8088 Timing

## CPU

**RD**, **pin 32 (read strobe)**. This line goes low when the CPU reads from memory or an I/O port, and goes to a high impedance state during hold acknowledge (HLDA).

**WR**, pin 29 (write strobe). This line goes low when the CPU writes to memory or an I/O port, and goes to a high impedance state during HLDA.

$IO/\overline{M}$ , pin 28 (status line). This line goes low during a memory read or write ( $\overline{RD}$  or  $\overline{WR}$  asserted). It is logic 1 for an I/O read or write. It is 3-stated during HLDA.

$DT/\overline{R}$ , pin 27 (data transmit/receive). This line is similar to  $IO/\overline{M}$ .

**SSO**, pin 34 (status line). This line is used with  $DT/\overline{R}$  and  $IO/\overline{M}$  to develop the S-100 status circuit signals. The logic levels on this line depend on what type of instruction the CPU is processing. This line is brought to a high impedance state during HLDA.

**ALE, pin 25 (address latch enable).** This line pulses high when the CPU places the address information on the address/ data bus. In the Computer, this line clocks the address into external latches on the negative-going edge of ALE.

**AD0-AD7, pins 16-9 (address/data bus).** When ALE is asserted, these lines contain the lower eight bits of the 20-bit address. This can be a memory address or an I/O port address. Later in the machine cycle, when data is to be transferred, these lines contain the input or output data. Demultiplexing circuits in the Computer are used to separate the data and address information. These lines are 3-stated during HLDA.

**A8-A15, pins 2-8 & 39 (address bus).** These lines carry the next eight bits of the address. This is memory address during a memory access and I/O address during the port access. These lines hold the address during the entire bus cycle. They are 3-stated during HLDA.

CPU

**NMI, pin 17 (non-maskable interrupt).** A positive-going transition on this line interrupts the CPU. It cannot be blocked with software. The CPU will complete its current instruction and then service the interrupt.

**INTR, pin 18 (interrupt request).** The CPU tests this line during the last clock cycle of each instruction to see if some device is requesting an interrupt. If pin 18 is logic 1, then an interrupt request is taking place. The CPU processes the interrupt unless the interrupt is masked by software.

**INTA**, **pin 24 (interrupt acknowledge).** The CPU brings this line to logic 0 to inform the interrupting device that it is processing the interrupt. It is used as a read strobe to get vector information from the interrupt circuits (see the interrupt circuit description for more details).

**HLDA, pin 30 (hold acknowledge).** This pin goes high to indicate that the CPU has acknowledged a hold request at pin 31.

**HOLD, pin 31 (hold request).** This line goes high when another device requests control of the bus, such as when the 8085 is the active processor. The CPU asserts the HLDA line and suspends operation.

A19-A16, pins 35-38 (address/status bus). These lines hold the top four bits of the 20-bit address bus when the ALE is active. ALE clocks this value into external latches when it returns to 0. These lines contain status information during the last part of the machine cycle. This feature is not used in the Computer since it gets the status information in a different manner. These lines are 3-stated during HLDA.

**TEST, pin 23 (test input).** This input is examined by the "WAIT FOR TEST" software instruction. If pin 23 is low, execution continues. Otherwise, the processor waits in an idle state.

#### CPU

**MN/MX**, **pin 33 (minimum/maximum).** A logic 1 on this pin places the 8088 in the minimum mode, the mode used by the Computer. When it is placed in the maximum mode, some of the pin functions change. Usually, the maximum mode is used for larger systems and multiprocessing systems.

**RESET, pin 21 (reset).** This pin goes high to reset the 8088. The interrupts are disabled, certain registers in the 8088 are set or cleared, and the instruction pointer (program counter) points to the address 16 bytes below the top end of the 1 megabyte range (FFFF0H).

The line is asserted when the  $\overline{\text{RESET}}$  line at U236, pin 11 is pulled low. A Schmitt trigger shapes up this signal and the clock retimes it before applying it to the 8088.

**READY, pin 22 (ready).** This is an acknowledgement signal from the addressed memory or I/O port that it is ready to transfer data. When this line is low, the CPU goes into a wait state until the addressed device brings it high. This allows using the 8088 with slow memory or I/O devices.

The READY signal is generated when U205-9 places a logic 1 on U236, pin 4. U236 synchronizes this signal with the 8088 clock to ensure correct set-up and hold times.

**CLK, pin 19 (8088 clock input).** This is a 5-MHz clock that provides timing to the 8088.

This signal comes from U236, pin 8, which derives it from the 15-MHz crystal at Y103. Duty cycle is about 33% for optimized timing inside the 8088. [When the 8088 is the active processor, this line ( $88\Phi$ ) also goes to the CPU dock swap logic to provide system timing.]

#### Timing

Timing for the 8088 is essentially the same as the timing for the 8085, since the 8088 is operated in the "min" mode.

CPU

#### **Processor Swap Port**

#### General

The processor swap port controls which CPU is to be active, handles interrupt routing, and ensures proper timing of the clock circuits during the swap. To access the swap port, the CPU writes a control byte to port 0FEH. Only three bits of the byte are used: AD0 controls the automatic wrap and/or mask mode, AD1 controls the swap interrupt line, and AD7 performs the processor swap.

At power up, the reset circuits clear U171 pin 9 to logic 0. This pin, 8SEL, connects to U186, a 12H6 PAL, through pin 5. This IC responds by placing a logic 0 on U187 pin 12 and a logic 1 on U187 pin 2. On the first positive transition of  $\overline{85\Phi}$ , the 85HOLD line goes low, enabling the 8085 CPU. On the first positive transition of  $\overline{88\Phi}$ , the 88HOLD line goes high, disabling the 8088 CPU.

The 8085, while executing the code in the monitor ROM, soon transfers control to the 8088. It does this by setting bit 7 of the processor swap port control byte to logic 1 by writing to that port.

The CPU address port 0FEH asserts SWAPCS (from the I/O decoder) at U206 pin 5. It then sets AD7 to logic 1 at U171 pin 12. Finally, it asserts the write line at U206 pin 6. As a result, U171 pin 11 goes high and latches U171 pin 9 to logic 1. The 8SEL line is now asserted. The values at U172 pin 12 and U172 pin 2 are also latched to their respective outputs.

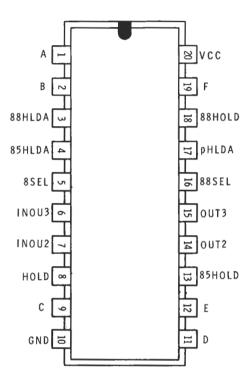

The 8SEL line, now logic 1, causes U186 pin 13 to change to logic 1, pin 18 to change to logic 0, and pin 16 to change to logic 1. This last line, 88SEL, couples to U215 to form the S-100 bus line (pin 21), NDEF (8088). This line is a "not-tobe-defined" line that can be used for any function. In the Computer, this line asserts when the 8088 is active.

The HOLD\* line at U185 pin 11 asserts whenever a board on the S-100 bus takes control of the Computer. This causes U186 to disable both the 8085 and the 8088 through U187. Both CPUs respond by returning their HLDA signals; the 8088 at U186 pin 3 and the 8085 at U171 pin 2. When this happens, U188 asserts the HAK line at pin 17. This, in turn, raises the S-100 pHLDA line to logic 1 at U180 pin 9. The board that generated the HOLD\* request can now take control of the Computer.

#### Swap Timing

The 88SEL line also goes to U188, pin 4, a quad D-type latch that suppresses any glitches on the system clock line when the Computer switches from one CPU to the other. It also ensures that the CPU being disabled is no longer active when the other CPU is enabled.

The 8085 and the 8088 run on separate crystal-controlled clocks; the 8085 from Y101 and the 8088 from Y105. Although these clocks are stable, they are not in phase. Switching from one clock to another can cause a glitch on the system clock line, S $\Phi$ , that can upset the timing in other circuits.

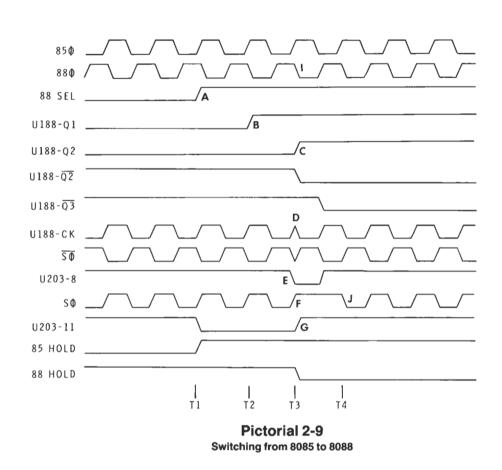

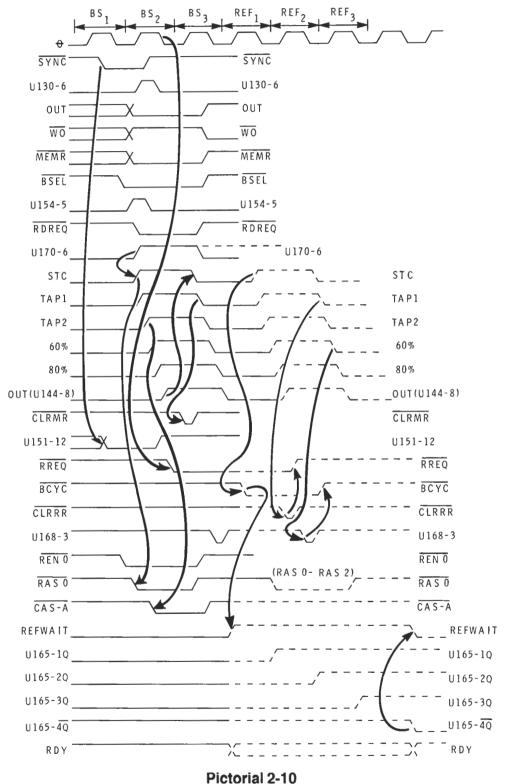

To see how U188 and its associated circuits block this spike, refer to Pictorial 2-9.

CPU

The two top waveforms are the respective clocks for the 8085 and 8088 CPUs. These are present at the inputs of inverters U200 pin 2 and U200 pin 14. Assuming that the 8085 is the active processor, then U200 pin 1 is low and  $\overline{85\Phi}$  couples through the inverter to form  $\overline{S\Phi}$ . It also couples through U225B to clock U188.

At time T1, the 8088 is selected; the 88SEL line goes to logic 1 as shown at A in Pictorial 2-9 (waveforms illustration). On the next positive edge of the clock at U188 pin 9, this logic 1 latches into U188 pin 2, which is the Q1 output at B. The next clock pulse causes the Q2 output to latch high, shown at C.

### CPU

When Q2 goes high, it 3-states U200 through the exclusive-OR gate at U203B. At the same time,  $\overline{Q2}$  goes low to couple the 88 $\Phi$  clock to the  $\overline{S\Phi}$  line. Since, in this example, the two clocks are nearly 180 degrees out of phase, the clock immediately returns to 0, causing the spike at D in Pictorial 2-9.

Up until this time, the output of U203, pin 8, another exclusive-OR gate, has been logic 1. This is because its inputs Q2 and  $\overline{Q3}$  of U188 have been in opposite states. However, since Q2 went high at time T3, both inputs to U203C are the same, causing U203 pin 8 to go to logic 0 (waveform E). This forces the system clock output at U225 pin 3 to logic 1 until time T4 (waveform F).

At time T4, the first positive-going edge of the 8088 clock causes the  $\overline{Q3}$  output of U188 to go high. This opens the gate at U225A to pass the system clock, which is now the 8088 signal.

As mentioned earlier, the other function that 88SEL and U188 performs is to ensure that the CPU being disabled is completely disabled before the CPU to be enabled is activated. To see how this is done, again refer to Pictorial 2-9.

Assume as before that the Computer is switching from the 8085 to the 8088. At time T1, the 88SEL line, which is coupled to U203 pin 11, goes high, the other input of this exclusive-OR gate is the  $\overline{Q2}$  U188. Since both inputs are now the same state, U203, pin 11 goes to logic 0 to preset both HOLD latches at U187.

Both CPUs go into a HOLD state and keep HLDA signals asserted at U186; the 8088 to pin 3 and the 8085 to pin 4 through U171.

At time T3, the  $\overline{Q2}$  line goes low and U203 pin 11 returns to logic 1, releasing the latches at U187 from their preset states. On the next positive-going edge of the  $\overline{88\Phi}$  clock signal, the logic 0 at U187 pin 2 is latched into U187 pin 5, removing the 8088 from the hold state.

CPU

U188 pin 7 goes high to drive U215 pin 3 high. This last IC connects to pin 21 of the S-100 bus to form the NDEF (8088/8085) line. This line is a "not-to-be-defined" line that can be used for any function by the computer manufacturer. For the H/Z-100 Series Computer, this line asserts when the 8088 is active.

The same process takes place when control of the system is switched from the 8088 to the 8085; the only difference is that the Q outputs of U188 are going from logic 1 to logic 0. (See the bottom group of waveforms in Pictorial 2-9.)

#### Auto Swap On Interrupt/Mask Mode

The interrupt mask circuits ensure that interrupt requests are sent to the currently active CPU. The mask bit, MSK, is set or cleared by setting or clearing bit 0 of the processor swap port. If cleared, and the 8085 is active, the 8085 gets all interrupt requests. If set, and the 8085 is active, the interrupt request is blocked but the swap port disables the 8085 and enables the 8088. If the 8088 is active, all interrupt requests are sent to the 8088 regardless of the mask bit.

After reset, 5SEL at U171 pin 8 and  $\overline{\text{MSK}}$  at U172 pin 6 are logic 1, so that the 8085 is active and handles all interrupts. These two lines connect to U225 pin 9 and U225 pin 10, which are shown near the 8085 on the schematic. U220 pin 2 inverts the resulting logic 0. This enables U189A and U189D. U189D can now couple non-maskable interrupts to the trap input of U210, and U189A can pass standard interrupts to U210's interrupt request input.

The 8SEL line, which is the complement of 5SEL, disables U189B and U189C, the AND gates to the 8088.

### CPU

If, while the 8085 is selected, the  $\overline{\text{MSK}}$  line is set to logic 0, then U220 pin 2 disables U189A and U189D. This blocks the interrupt request from both the 8085 and the 8088. However, if either a standard or an NMI interrupt request occurs, U156 pin 6 will go high to assert the NMINT line.

This line connects to U155 pin 9 in the processor swap port. The other input is the MSK line which is also high. As a result, U155 pin 8 goes low to assert the 8SEL line. The Computer switches to the 8088 processor as described previously.

When the 8088 is active, 8SEL is high to enable U189B and U189C. U189A and U189D are disabled because 5SEL is logic 0 at U225 pin 9. So, no matter what the setting of the  $\overline{\text{MSK}}$  bit at U225 pin 10, all interrupt requests are routed to the 8088 processor.

#### Swap Interrupt

Whenever one of the CPUs is placed into the HOLD state, it does not lose the contents of its registers. This way, when that CPU is again enabled, it can begin processing where it left off.

Alternatively, the currently active CPU can generate a swap interrupt to start the disabled CPU at a different memory location than where it was when it was turned off. It does this by programming the master 8259A to mask all interrupts except the swap interrupt, and then it asserts the SWAPINT line.

To generate the swap interrupt command, the Computer sets bit 1 to logic 1 in the processor swap port. It does this by asserting  $\overline{SWAPCS}$  (from the I/O decoder) at U206 pin 5, setting AD1 to logic 1 at U172 pin 12, and then asserting the  $\overline{WR}$  line at U206 pin 6. U206 pin 4 goes high to latch U172 pin 9 to logic 1, sending the SWAPINT command to the interrupt circuits.

CPU

At the same time, the CPU also writes the correct control bits to 8SEL and MSK on the processor swap port. The Computer changes CPUs, finds that the SWAPINT line is asserted, and jumps to the correct location to process the interrupt.

### **Reset Circuits**

#### **Power-Up Reset**

R114 and C189 provide the power-up reset signal for the Computer. Upon turn-on, C189 charges through R114, holding U207 pin 8 low for about 200 ms. This signal connects to several buffers to provide the proper reset levels to the rest of the computer:

U201B buffers the reset signal to provide the S-100 power-on clear (POC\*) signal. This signal is logic 0 for reset and logic 1 otherwise. POC\* resets the video board through U215D and P106 pin 64.

U201A buffers the reset signal to provide the S-100 SLAVE CLR\* signal. Because U207 pin 8 controls U201A through its gate line (pin 1), SLAVE CLR\* is logic 0 to clear and opencollector otherwise. This signal is present only to meet IEEE-696 (S-100) standards. Currently, it is not used in the Computer.

U210C is also wired to provide a logic 0 for reset and a highimpedance state otherwise. This is because several circuits may share the S-100 RESET\* line. This line drives U177H and, through the S-100 bus, resets the Floppy Disk Controller Board.

U177H inverts the reset signal, which can be the power up reset or a keyboard reset, to drive the RESET line high. This line is again inverted by U177G and U177F to provide RESET1 and RESET2; all three lines go to several places on the motherboard and video board to provide the proper reset signals.

CPU

#### **Keyboard Reset**

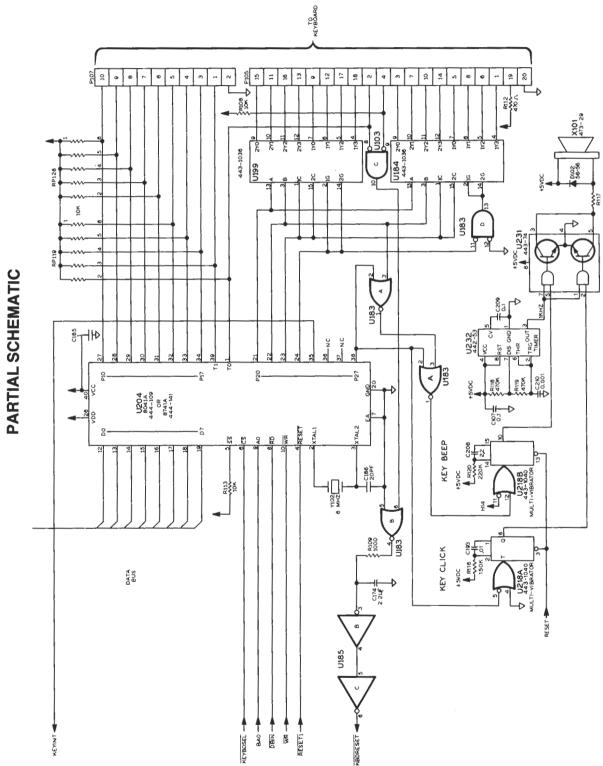

When you press the CRTL key and the RESET key at the same time, pins 8 and 9 of U103 go low and force U183 pin 10 to logic 1. This is inverted at U183 pin 4 and coupled to U185A through the filter network, R109 and C174.

U185B and U185C invert the signal twice to provide the activelow KBDRESET pulse that couples to U201 pin 13. The output, U201 pin 11, is logic 0 for reset and high-impedance otherwise.

From U201 pin 11, the reset signal is processed as described earlier in "Power-Up Reset."

#### **Dip-Switch Select Circuits**

U239, S101, and U156A make up the DIP-switch select circuits. The position of these switches determine the operating mode of the Computer.

The Computer reads the status of S101 during power-up by addressing input port 0FFH. To read the DIP-switch port, the CPU asserts the DSWSEL port select line coming from the I/O port decoder at U159 pin 7. The CPU also asserts the S-100 pDBIN line to indicate that an I/O read operation is to take place. U195 inverts the pDBIN line to produce DBIN at U156 pin 2.

Since pins 1 and 2 of U156 are both low, pin 3 of this OR gate also goes low to enable U239. The outputs of U239 go from a high-impedance state to the logic level of each switch section. This, in turn, is loaded into the accumulator of the CPU for further processing.

CPU

# CIRCUIT DESCRIPTION

### S-100 Bus Status Circuits

The IEEE-696 S-100 bus contains eight status lines, because there are eight basic types of machine cycles. The Computer uses all but one of these lines. The unused line, sXTRQ\*, is still available for use by plug-in boards.

Following the S-100 (proposed IEEE-696) standard, the status lines designations are prefixed with a lower-case "s." All but two of the lines, sWO\* and sXTRQ\*, assert on logic 1. Briefly, this is what each status line does:

**sXTRQ\***, **pin 58 (sixteen-bit request).** This line allows 8-bit and 16-bit boards to share the same bus. Since the Computer is an 8-bit machine externally and a 16-bit machine only inside the 8088, this line is kept disabled by connecting U227 pin 18, to logic 1.

However, if a true 16-bit CPU board is plugged into the S-100 bus, the Computer can be programmed to give control to this CPU, and this CPU can perform 16-bit transfers with other 16-bit boards on the bus.

It does this by asserting sXTRQ\* and addressing the 16-bit board (U227 pin 19 is 3-stated at this time by a low at U182 pin 9). If the addressed device can process 16-bit words, it asserts another S-100 line called SIXTN\*. Next, the data buses are ganged together; lines DO0-DO7 handle even bytes while lines DI0-DI7 handle odd bytes, and the data transfer takes place. (Odd bytes is defined as A0 = 1, and even bytes as A0 = 0.

If the device cannot process 16-bit words, such as memory and I/O on the motherboard and video board, SIXTN\* remains high. In this case, DO and DI lines operate normally and the CPU must process the data a byte at a time.

### CPU

**sM1, pin 44 (op code fetch).** This line asserts when the 8085 processor fetches a new instruction from program memory. It returns to logic 0 at the end of the M1 machine cycle. However, when the 8088 is operating, the asserted sM1 line does not guarantee the fetch of a new instruction. It only indicates that a "code access" has been decoded by the 8088. (In future versions of the Z-100 Computers, the 8088 might not assert the sM1 line at all.)

**sOUT, pin 45 (write to output port).** This line asserts to indicate that the CPU is going to send data to the addressed output port.

**sINP, pin 46 (read from input port).** This line asserts to indicate that the CPU is going to read data from the addressed input port.

**sMEMR, pin 47 (memory read).** This line asserts to indicate that the CPU is going to read data from the addressed memory location.

**sHLTA, pin 48 (halt acknowledge).** This line asserts when the CPU processes a HALT command and has stopped executing the program.

**sINTA, pin 96 (interrupt acknowledge).** This line asserts when it is processing an interrupt.

**sWO\*, pin 97 (memory write).** This line asserts when the CPU is going to write data to either memory or an output port.

These lines are derived from the status lines of whichever CPU is active. In the 8088, these lines are  $IO/\overline{M}$ , DT/ $\overline{R}$ , and  $\overline{SSO}$ . In the 8085, these lines are  $IO/\overline{M}$ , S1, and S0.

When the 8088 is active, the 88SEL line at U226 pin 13 is logic 1. This causes the  $32 \times 8$  PROM to correctly decode the bit pattern on pins 10, 11, and 12 as an 8088 status code. As you will see later, this code is different for the 8085.

CPU

88SEL also 3-states 85S0 and 85S1 at pins 1 and 4 of U237. The line from  $85I0/\overline{M}$  is in a high-impedance state when the 8085 is disabled, so it does not need a buffer.

U226 decodes the machine cycle status and asserts the correct line on the output. U226 pin 1, through U226 pin 7. When the ALE line goes low, the outputs of U226 are latched into U227.

When the 8085 is active, the 88SEL line at U226 pin 13 is logic 0. This causes U227 to correctly decode the bit pattern on pins 10, 11, and 12 as an 8085 status code. U226 decodes this status which is subsequently latched into U227 when ALE goes low.

The following chart shows the status codes of each CPU and what S-100 status line each code affects.

| 8085 |    |    |                | 8088 |      |     | S-100          |            |

|------|----|----|----------------|------|------|-----|----------------|------------|

| 10/M | S1 | S0 | Status         | IO/M | DT/R | SS0 | Status         | Status     |

| 0    | 1  | 1  | Op code fetch  | 0    | 0    | 0   | Code access    | sM1, SMEMR |

| 1    | 0  | 1  | I/O write      | 1    | 1    | 0   | Write I/O port | sOUT, SW0* |

| 1    | 1  | 0  | I/O read       | . 1  | 0    | 1   | Read I/O port  | sINP       |

| 0    | 1  | 0  | Memory read    | 0    | 0    | 1   | Memory read    | sMEMR      |

| Z    | 0  | 0  | HALT           | 1    | 1    | 1   | HALT           | sHLTA      |

| 1    | 1  | 1  | Interrupt Ack. | 1    | 0    | 0   | Interrupt Ack. | sINTA      |

| 0    | 0  | 1  | Memory write   | 0    | 1    | 0   | Write memory   | sWO*       |

Z = High impedance at CPU IO/ $\overline{M}$  3-state line.

### CPU

### **Wait Timing**

The WAIT line at pin 9 of U226 equalizes the timing characteristics between the 8085 and the 8088. It does this by adding the appropriate wait states during a memory or I/O access. The number of wait states depends on the active CPU and the type access, as shown in the chart below.

#### Wait Timing

|               | 8085 Active   | 8088 Active  |  |  |

|---------------|---------------|--------------|--|--|

| Memory Access | 1 wait state  | 0 wait state |  |  |

| I/O Access    | 2 wait states | 1 wait state |  |  |

U233 pin 5 provides the basic wait timing. When ALE asserts, pin 5 is cleared. After ALE goes low, pin 5 goes high on the next system clock pulse. If the machine cycle is a memory or I/O access, the wait line asserts according to the chart above.

The asserted wait line is inverted by U206A to clear pin 9 of U205. This logic 0 couples directly to the 8085 READY input and indirectly to the 8088 READY input through U236. The active CPU goes into a wait state until the next system clock pulse at pin 11 of U205. Operation then proceeds normally.

The RDY and XRDY lines are S-100 "ready" lines. If either line is low, the CPU goes into a wait state at the end of a machine cycle, as follows.

The ALE line clears U205 at the beginning of each machine cycle. Both RDY and XRDY are normally logic 1 at pin 12 of U205. Unless the wait line is asserted, the next clock pulse will latch U205 pin 9 to a logic 1, ensuring that the active CPU will not generate a wait state during that machine cycle.

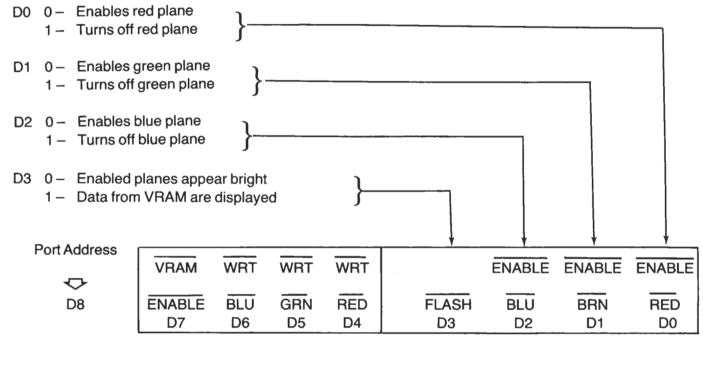

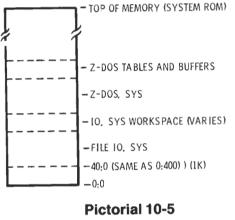

CPU